App installieren

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: This feature may not be available in some browsers.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

AMD: Wieso kein Octacore?

- Ersteller Matzelinho

- Erstellt am

Matzelinho

Vice Admiral Special

- Mitglied seit

- 22.06.2006

- Beiträge

- 584

- Renomée

- 4

- Standort

- Münsterland

- Mein Laptop

- ASUS X50Z (Athlon X2 QL-60 | HD3200 | 3GB | 320GB HDD)

- Details zu meinem Desktop

- Prozessor

- Intel Xeon X3350 | 3,6GHz | 1,24V

- Mainboard

- ASUS P5Q | 450MHz FSB

- Kühlung

- Thermalright Ultra-120 eXtreme | Scythe S-Flex 1200rpm

- Speicher

- Corsair 4GB DDR2-800 DHX Kit | 900MHz

- Grafikprozessor

- Gainward Radeon HD4850 1024MB "Golden Sample"

- Display

- Samsung SyncMaster 245B plus 24"

- HDD

- Samsung 2x200GB | WD 640GB | SATA2

- Optisches Laufwerk

- LG DVD-Brenner | LG-DVD Laufwerk | SATA

- Soundkarte

- HD-Sound Onboard

- Gehäuse

- CoolerMaster Centurion 5

- Netzteil

- Corsair VX 450W (80+)

- Betriebssystem

- Windows 7 Ultimate

- Webbrowser

- Firefox

Diese Frage müsste man sich doch stellen, wenn man sich Intel´s "zusammengebastelten Quad" anschaut, oder? Kein Privatman braucht einen Prozessor mit 8 Kernen, allerdings wäre eine solche Entwicklung ein gewaltiger Schub für das angekratzte Image...

Im Servermarkt ließe sich sowas bestimmt gut verkaufen?!

Weiß jemand ob so etwas geplant ist, oder überhaupt realisierbar? (Zwei Barcelonas in einer Cpu die über den HTT kommunizieren)

Bin mal gespannt wie andere darüber denken...

MfG

Im Servermarkt ließe sich sowas bestimmt gut verkaufen?!

Weiß jemand ob so etwas geplant ist, oder überhaupt realisierbar? (Zwei Barcelonas in einer Cpu die über den HTT kommunizieren)

Bin mal gespannt wie andere darüber denken...

MfG

Bobo_Oberon

Grand Admiral Special

- Mitglied seit

- 18.01.2007

- Beiträge

- 5.045

- Renomée

- 190

Mit dem aktuellen K10 wäre das ein Albtraum für AMD.

Wenn AMD schon nicht genügend K10 derzeit liefern kann, wie soll es dann um die Lieferbarkeit des hypothetischen 2x Quadcore bestellt sein?

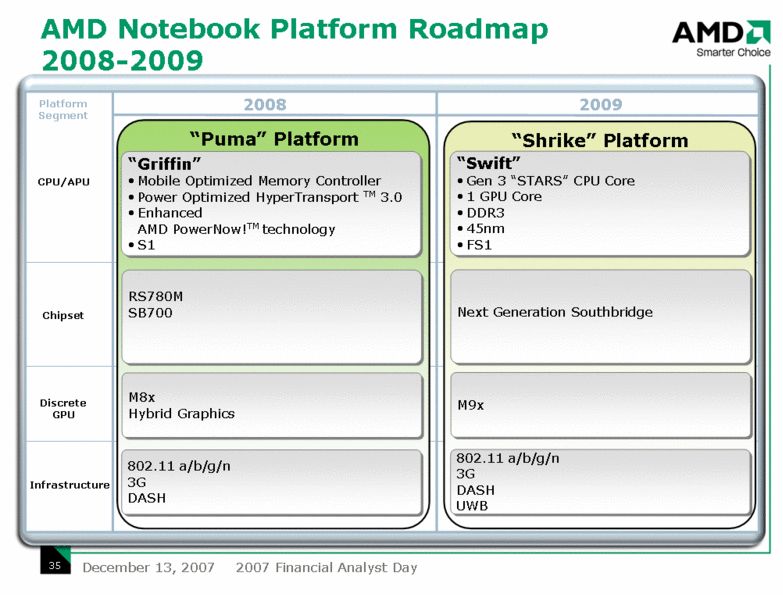

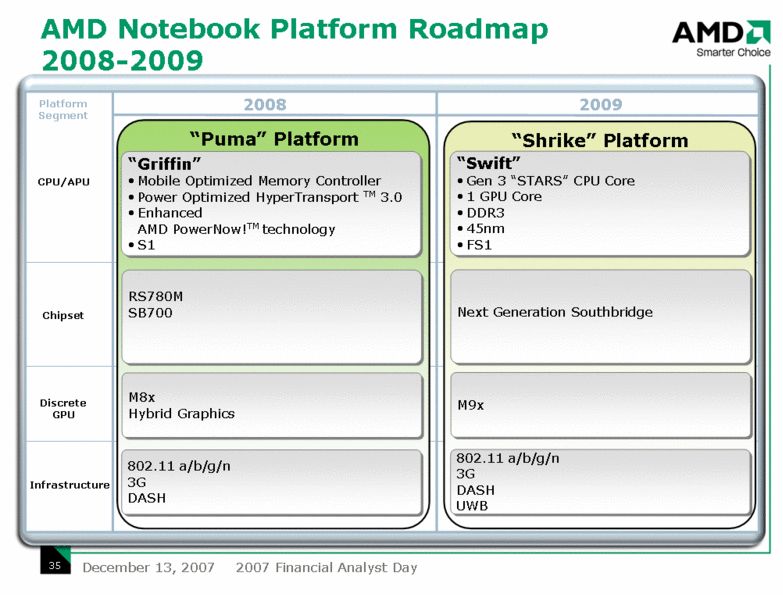

Für 2009 hingegen ist dagegen ein nativer Octacore geplant, was mit 45 nm auch realistisch zu schaffen ist.

MFG Bobo(2007)

Wenn AMD schon nicht genügend K10 derzeit liefern kann, wie soll es dann um die Lieferbarkeit des hypothetischen 2x Quadcore bestellt sein?

Für 2009 hingegen ist dagegen ein nativer Octacore geplant, was mit 45 nm auch realistisch zu schaffen ist.

MFG Bobo(2007)

Desertdelphin

Grand Admiral Special

- Mitglied seit

- 23.10.2002

- Beiträge

- 4.395

- Renomée

- 185

stromverbrauch?

Matzelinho

Vice Admiral Special

- Mitglied seit

- 22.06.2006

- Beiträge

- 584

- Renomée

- 4

- Standort

- Münsterland

- Mein Laptop

- ASUS X50Z (Athlon X2 QL-60 | HD3200 | 3GB | 320GB HDD)

- Details zu meinem Desktop

- Prozessor

- Intel Xeon X3350 | 3,6GHz | 1,24V

- Mainboard

- ASUS P5Q | 450MHz FSB

- Kühlung

- Thermalright Ultra-120 eXtreme | Scythe S-Flex 1200rpm

- Speicher

- Corsair 4GB DDR2-800 DHX Kit | 900MHz

- Grafikprozessor

- Gainward Radeon HD4850 1024MB "Golden Sample"

- Display

- Samsung SyncMaster 245B plus 24"

- HDD

- Samsung 2x200GB | WD 640GB | SATA2

- Optisches Laufwerk

- LG DVD-Brenner | LG-DVD Laufwerk | SATA

- Soundkarte

- HD-Sound Onboard

- Gehäuse

- CoolerMaster Centurion 5

- Netzteil

- Corsair VX 450W (80+)

- Betriebssystem

- Windows 7 Ultimate

- Webbrowser

- Firefox

stromverbrauch?

Ok, daran hatte ich nocht nicht wirklich gedacht, aber mit einer weiterentwickelten C´nQ Technik ließe der sich bestimmt senken. Dem Takt wären natürlich grenzen gesetzt...

Wan_Mateng

Admiral Special

Da ich leider jetzt nicht die Roadmap von AMD im Kopf habe kann ich dir zumindest sagen

das Intel mit dem Nehalem einen nativen Octacore auf den Markt bringen wird, was aber auch erst 2009 stattfinden wird da der native Quad erst Ende 2008 kommt.

mfg

das Intel mit dem Nehalem einen nativen Octacore auf den Markt bringen wird, was aber auch erst 2009 stattfinden wird da der native Quad erst Ende 2008 kommt.

mfg

Eye-Q

Grand Admiral Special

- Mitglied seit

- 01.10.2003

- Beiträge

- 7.214

- Renomée

- 425

- Standort

- Hamburch

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 5 5600G

- Mainboard

- ASRock B450 Pro4

- Kühlung

- Scythe Mugen 5 Rev. B

- Speicher

- 16 GB G.Skill DDR4-3200

- Grafikprozessor

- AMD Radeon RX 6700 XT Founders Edition

- Display

- EIZO EV3237

- SSD

- Kingston A2000 M.2 PCIe 500 GB (System) + Kingston NV2 M.2 PCIe 2 TB + Crucial MX100 SATA 256 GB

- Soundkarte

- Asus Xonar DX

- Gehäuse

- Fractal Design Define C

- Netzteil

- be quiet! Pure Power 11 CM 500W

- Tastatur

- das Keyboard IV Ultimate

- Maus

- Logitech MX Master 3

- Betriebssystem

- Windows 10 Pro 64 Bit

- Webbrowser

- Vivaldi

Das war nicht auf den Idle-Verbrauch bezogen sondern auf den Verbrauch unter Last - selbst der Barcelona "HE" hat ja schon eine TDP von 68 W, da würden rechnerisch zwei Stück auf einer CPU 146 W haben, was kompletter Selbstmord ist, das können selbst Server nicht ab.Ok, daran hatte ich nocht nicht wirklich gedacht, aber mit einer weiterentwickelten C´nQ Technik ließe der sich bestimmt senken. Dem Takt wären natürlich grenzen gesetzt...

Rangoon

Commodore Special

- Mitglied seit

- 14.04.2007

- Beiträge

- 393

- Renomée

- 16

- Aktuelle Projekte

- QMC,SIMAP,Spin,Rosetta

- Lieblingsprojekt

- QMC

- Meine Systeme

- Phenom II 1090T@ 3.6GHZ, Turion X2 1.6GHz

- BOINC-Statistiken

- Mein Laptop

- FS PA 1538 (Turion X2), Acer Aspire One 522

- Details zu meinem Desktop

- Prozessor

- Ph 2 1090T BE@3.6GHz/1.325V

- Mainboard

- Gigabyte GA-MA 790FX DQ-6

- Kühlung

- EKL GroßClockner

- Speicher

- 4x2GB OCZ DDR2-1066@800

- Grafikprozessor

- Sapphire HD 5770

- Display

- 17" Röhrenmonitor Samsung TF795

- HDD

- 300GB WD Veloci Raptor, 1000GB WD Green

- Optisches Laufwerk

- DVD-ROM, DVD-Brenner

- Soundkarte

- onboard

- Gehäuse

- Irgendein NoName

- Netzteil

- Tagan TG480-U15

- Betriebssystem

- Win 7 64-bit Home Premium

- Webbrowser

- Firefox

AMD: Wieso kein Octacore?

Bevor AMD überhaupt mal an die Entwicklung eines 8-Kern-Prozessors denkt, sollten sie erstmal die IPC pro Kern hochschrauben. Das hätte erste Priorität. Im Homebereich ist ja selbst der Einsatz eines Quadcores schon relativ sinnfrei. Entscheidend ist für die allermeisten Anwendungen immer noch, was ein Kern leistet. Gerade hier muß AMD wieder Anschluß an Intel finden. Wenn das paßt, dann kann man auch mal wieder an mehr Kerne denken.

Gruß

Rangoon

MusicIsMyLife

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 22.02.2002

- Beiträge

- 15.580

- Renomée

- 2.569

- Standort

- in der Nähe von Cottbus

- Lieblingsprojekt

- Asteroids@Home

- Meine Systeme

- Alltags-PC, Test-PC (wechselnde Hardware)

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Desktopsystem

- Alltags-PC

- Mein Laptop

- HP DV7-2225sg

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 7950X

- Mainboard

- ASRock B650M PG Riptide

- Kühlung

- Watercool Heatkiller IV Pro Copper

- Speicher

- 2x 32 GB G.Skill TridentZ 5 TGB (F5-6000J3040G32X2-TZ5RS)

- Grafikprozessor

- AMD Radeon RX 6900XT

- Display

- ASUS ROG PG42UQ (3840x2160), Philips BDM4065UC (3840x2160), Samsung C27HG70 (2560x1440)

- SSD

- Micron 9300 Pro 7,68 TB (U.2), Samsung 850 Evo 4 TB (SATA)

- HDD

- keine, SSD only...

- Optisches Laufwerk

- LG CH08LS10 Blu-ray Disc-Player

- Soundkarte

- Creative SoundBlasterX AE-5 Plus

- Gehäuse

- Dimastech BenchTable EasyXL (vorübergehend)

- Netzteil

- Corsair RM850i

- Tastatur

- ASUS ROG Strix Flare

- Maus

- Steelseries Sensei 310

- Betriebssystem

- Windows 10 Professional

- Webbrowser

- Firefox

- Schau Dir das System auf sysprofile.de an

- Internetanbindung

- ▼250 MBit ▲45 MBit

Das war nicht auf den Idle-Verbrauch bezogen sondern auf den Verbrauch unter Last - selbst der Barcelona "HE" hat ja schon eine TDP von 68 W, da würden rechnerisch zwei Stück auf einer CPU 146 W haben, was kompletter Selbstmord ist, das können selbst Server nicht ab.

68 + 68 = 136

Und 136 Watt sind widerum nicht weit von dem entfernt, was zum Beispiel ein Intel Core 2 Quad B3 verbraten kann (TDP 130 Watt). Ergo würde ich das nicht unbedingt als KO-Kriterium nennen.

Vielmehr würde sich mir die Frage stellen, welche Software auf einer solchen CPU laufen soll. Momentan unterstützen nur wenige Anwendungen überhaupt DualCore-CPUs, von QuadCore-CPUs ganz zu schweigen. Wo soll da plötzlich die Software herkommen, die 8 Kerne unterstützt?

st3pp3nw0lf

Admiral Special

- Mitglied seit

- 07.01.2006

- Beiträge

- 1.049

- Renomée

- 12

- Details zu meinem Desktop

- Prozessor

- AMD pHENOM 2 940

- Mainboard

- ASUS M3A78-T

- Kühlung

- Xigmatek Red Scorpion

- Speicher

- GSkill 4GB Kit DDR2 800

- Grafikprozessor

- 2x MSI 4770 CF

- Display

- Syncmaster 2343bw 23" @ 2048*1152

- HDD

- WD640GB Caviar Blue

- Optisches Laufwerk

- Samsung SH 183 sata

- Soundkarte

- SB Audigy SE

- Gehäuse

- Thermaltake Xaser V

- Netzteil

- DAX 600

- Betriebssystem

- XP Pro SP3

- Webbrowser

- Firefox

so setzt man gerüchte in die welt

rkinet

Grand Admiral Special

, Yield rate undstromverbrauch?

Speicheranbindung

Es bilden sich ja Flaschenhälse aus und solche Designs benötigen auch viel Strom.

Intel packt in 45nm und tollen Taktraten Werte beim Quad unterhalb von 130 Watt.

Ein Oktacore in 32nm dürfte pro Core bei gleichen Takt nur die Hälfte verbrauchen, was schon extreme Anforderungen stellt.

Wobei es nicht nur um die TDP geht, sondern die Vcc sinkt was immer höhere Stromstärken im DIE verursacht bei geringerer Toleranz an die Vcc.

Es wäre daher zumindest vernünftig Okta-Core und mehr für relativ geringe Taktraten zu designen und dann für Anwendungen, die von vielen Cores Vorteile ziehen.

Das wäre dann die Leistungsregion die heutige 60-75 Watt Quad abdecken.

Ein Leistungssprung vs. zwei isolierten Quad wäre kaum feststellbar.

LinuS

Vice Admiral Special

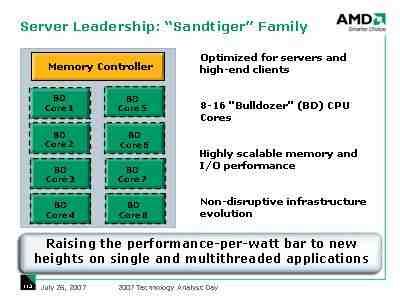

War nicht eher ein Octacore per MCM geplant? Afaik schwirrt mir da noch was von solch tollen "Werbefolien" herum, evtl sogar im Zusammenhang mit dem Shanghai.Für 2009 hingegen ist dagegen ein nativer Octacore geplant, was mit 45 nm auch realistisch zu schaffen ist.

NeuerBenutzer

Fleet Captain Special

- Mitglied seit

- 09.12.2005

- Beiträge

- 324

- Renomée

- 6

- Standort

- Saarland

- Details zu meinem Desktop

- Prozessor

- Intel Pentium 4 3000 MHz

- Mainboard

- ABIT IC7-G

- Kühlung

- Intel Boxed

- Speicher

- 2 x 512 MB PC3200 MDT

- Grafikprozessor

- ATI Radeon 9200 (Sapphire)

- Display

- Samsung SyncMaster 957p

- HDD

- Seagate 120 GB

- Optisches Laufwerk

- CD-ROM

- Soundkarte

- OnBoard

- Gehäuse

- Chenbro Big-Tower

- Netzteil

- NoName 350W

- Betriebssystem

- Microsoft Windows 2000 Professional

- Webbrowser

- SeaMonkey 1.1.11

Weiß jemand ob so etwas geplant ist, oder überhaupt realisierbar? (Zwei Barcelonas in einer Cpu die über den HTT kommunizieren)

Da AMD den Speichercontroller in der CPU hat kann es bei einem solchen Vorhaben eigentlich nur einen Weg geben:

Core 1 = RAM und HyperTransport

Core 2 = HyperTransport

Und zwischen Core 1 + Core 2 nochmal HyperTransport.

Irgendein MB-Hersteller hatte sowas auch schon einmal gebaut um Dual Sockel 940 auf normale ATX-Größe zu quetschen.

Die Frage wäre am Schluß ab wie die Geschichte dann aussieht wenn plötzlich 2, 4 oder gar 8 solcher CPUs auf einem MB werkeln sollen. Denn irgendwo fehlen ja dann die HyperTransport-Schnittstellen zu den benachbarten CPUs.

Bobo_Oberon

Grand Admiral Special

- Mitglied seit

- 18.01.2007

- Beiträge

- 5.045

- Renomée

- 190

Vermutlich wirds ein natives Quadcore-Design.

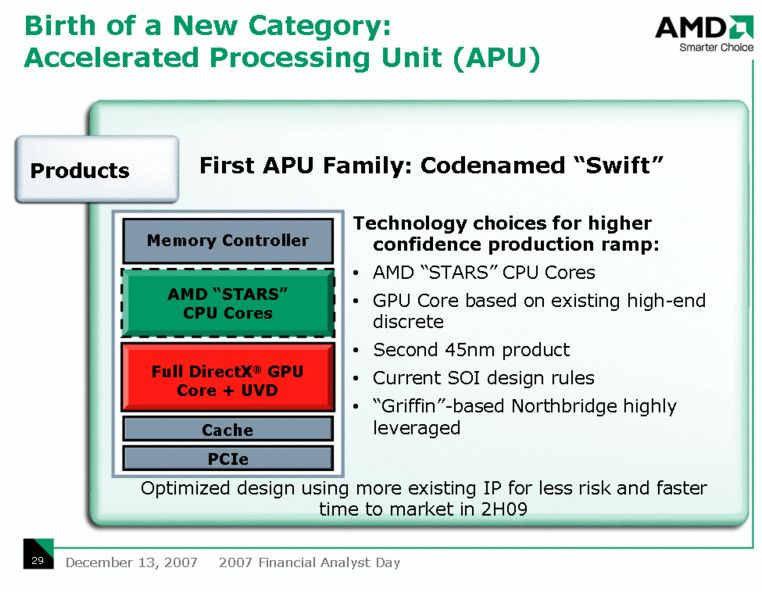

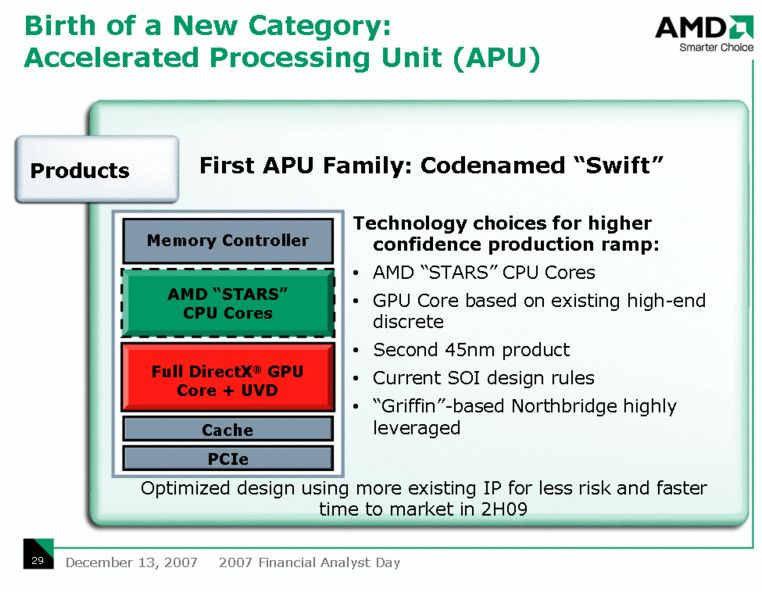

Der Fusion, eine Kombination von CPU und GPU wird vermutlich "zusammengepappt" werden:

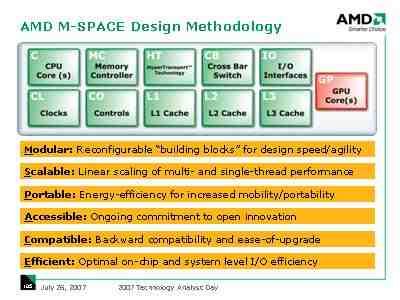

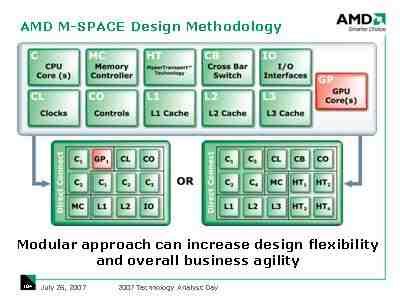

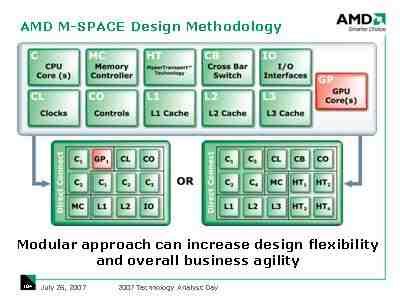

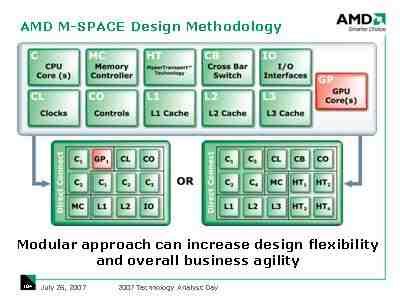

Aber ich denke, da hält sich AMD noch ne Hintertür offen, wie es gemacht werden wird:

Quelle

Octacores an sich gibt es jedoch schon länger in der Halbleiterindustrie (Sun, RMI, Cavium, ... ). Die Frage nach Software stellt sich daher nicht, jedenfalls nicht für den Server-Bereich.

MFG

rkinet

Grand Admiral Special

Das Ur-Design So. 754 sah zwei Sockets vor, die als Budget-Server je einen Speicherkanal ansteuerten.Da AMD den Speichercontroller in der CPU hat kann es bei einem solchen Vorhaben eigentlich nur einen Weg geben:

Core 1 = RAM und HyperTransport

Core 2 = HyperTransport

Und zwischen Core 1 + Core 2 nochmal HyperTransport.

Als Resteverwertung entstand der Desktop 754 mit nur einem Socket.

Die HTr Kanäle im Barcelona würden für so ein Design und je zwei weiter HTrs reichen, was dann 4 HTr Links nach außen ergäbe (wenn auch mit unterschiedlichen Latenzzeiten, abhängig ob die Daten noch über den internen HTr müssen)

Den internen HTr könnte AMD sogar auf 2* 32 Bit aufbohren, ohne groß das Design zu ändern.

Machbar wäre vieles und AMD könnte dann aus 45nm (Shanghai - Bulldozer) Quad-Core die mit geringer TDP selektieren und für diesen Quad verwenden.

Intel würde es so machen, wenn sie ähnliche Designs wie AMD im Programm hätten.

Aber AMD ist nicht Intel und man strebt nach HighTech, nicht funktionsfähiger udn erlösbringernder Standardware.

Opteron

Redaktion

☆☆☆☆☆☆

Für 2009 hingegen ist dagegen ein nativer Octacore geplant, was mit 45 nm auch realistisch zu schaffen ist.

Jo meiner Meinung ist mir auch nicht klar, ob das native oder nicht native werden soll ... es gibt da einzig und allein die Marketingfolien hier:War nicht eher ein Octacore per MCM geplant? Afaik schwirrt mir da noch was von solch tollen "Werbefolien" herum, evtl sogar im Zusammenhang mit dem Shanghai.

Und nachdem da nichts von nem L3 / SRI oder sonstwas steht, kann man in das Bild sowohl ein natives design als auch ein MCM reininterpretieren, bei dem jeweils ein Quad einen Speicherkanal bekäme.

Edit: Hmm wobei .. "memory controller" ist eigentlich eindeutig, das ist was andres als der Speicheranschluss / DRAM Controller ... hmm naja warten wirs ab

nöö siehe oben, wieso sollte das nicht möglich sein jedem einzelnem Core einen Speicherkontroller zu geben ? Bei mainboards und unterschiedliche Sockel kanns eventuel ein Platzproblem geben, weswegen es eben solche boards gab, bei denen die 2te CPU kein eigenes RAM hatte .. aber im MCM Fall ist das nur eine Frage der Verdrahtung ... sollte ziemlich egal sein.Da AMD den Speichercontroller in der CPU hat kann es bei einem solchen Vorhaben eigentlich nur einen Weg geben:

Core 1 = RAM und HyperTransport

Core 2 = HyperTransport

Und zwischen Core 1 + Core 2 nochmal HyperTransport.

Mein Tipp ... nachdem AMD so neidisch auf den Quad MCM geschaut hat, und nachdem der eigene Quadcore so kompliziert war .. denke ich, dass sie ein 2x4 MCM bauen. Mit einem DDR3 Kanal pro Kern einem L3 dahinter und als interconnect ein schneller HT3 link sollte das auch nicht sooo schlecht sein.

ciao

Alex

Zuletzt bearbeitet:

LinuS

Vice Admiral Special

Ah jetzt weiß ich, warum ich bei Shanghai schon auf Octacore und MCM kam:

http://www.fudzilla.com/index.php?option=com_content&task=view&id=553&Itemid=1

http://www.theinquirer.net/en/inquirer/news/2007/04/01/amd-travels-from-shanghai-to-montreal

http://www.heise.de/newsticker/meldung/93278

ergo evtl schon beim K10.5 ein Octacore, wenn sich da AMD nicht wieder übernimmt

ein Octacore, wenn sich da AMD nicht wieder übernimmt

Die Folie die ich meinte hat sich als Sandtiger, also genau dem was Bob beron bereits gepostet hatte, herausgestellt. Da müssen meine Synapsen wohl irgendwie falsch verdrahtet gewesen sein.

beron bereits gepostet hatte, herausgestellt. Da müssen meine Synapsen wohl irgendwie falsch verdrahtet gewesen sein.

http://www.fudzilla.com/index.php?option=com_content&task=view&id=553&Itemid=1

http://www.theinquirer.net/en/inquirer/news/2007/04/01/amd-travels-from-shanghai-to-montreal

http://www.heise.de/newsticker/meldung/93278

ergo evtl schon beim K10.5

ein Octacore, wenn sich da AMD nicht wieder übernimmt

ein Octacore, wenn sich da AMD nicht wieder übernimmt

Die Folie die ich meinte hat sich als Sandtiger, also genau dem was Bob

rkinet

Grand Admiral Special

Danke für die Folien.Ah jetzt weiß ich, warum ich bei Shanghai schon auf Octacore und MCM kam:

http://www.fudzilla.com/index.php?option=com_content&task=view&id=553&Itemid=1

http://www.theinquirer.net/en/inquirer/news/2007/04/01/amd-travels-from-shanghai-to-montreal

http://www.heise.de/newsticker/meldung/93278

ergo evtl schon beim K10.5ein Octacore, wenn sich da AMD nicht wieder übernimmt

Die Folie die ich meinte hat sich als Sandtiger, also genau dem was Bobberon bereits gepostet hatte, herausgestellt. Da müssen meine Synapsen wohl irgendwie falsch verdrahtet gewesen sein.

Dieser 'gebastelte Oktacore' könnte per viertem HTr 3.0 Link realisiert werden.

Wobei hier sogar 2* 32 Bit statt der externen 2* 16 Bit möglich wäre ohne große Mehrkosten.

Problematisch erscheint mir aber die TDP bzw. der mögliche Takt.

Wenn ich mich recht erinnere hat der So. F nur 95A, die So.AM2+ und So.AM3 gehen auf 110 A zzgl. 20A Northbridge. (http://www.planet3dnow.de/vbulletin/showpost.php?p=3415223&postcount=21)

Obiges könnte den Leistungsbedraf eines Octa-Core mittelerer Taktregion (2,5 GHz ? ) packen, bei 95A und typ. 1,15-1,2 V / 45nm eher nicht.

Zumindest bietet der 'gebastelte' Octa die Möglichkeit aus vielen Shanghai-Cores die mit guten TDP-Werten zu selektieren und so leicht 20-30% weniger TDP im Design zu haben als ein nativer Quad-Core.

Aber die Technik zeigt auch, dass AMD wieder deutlich am K10 gearbeitet hat, was wieder Bug-Risiken & Verzögerungen birgt. Auch ist die Frage, wie sich die Latenzzeit des 6M statt 2M L3 entwickelt.

Aber die Lösung ist technisch sichere als die 'Sandtiger'-Ideen, die ich eher auf Ende 2009 ansetze.

Zum Einfahren der 45nm fehlt aber ein einfaches Design - ich hoffe da immer noch auf den 2M-X3 als weitgehenden Shrink des Barcelona und Umgruppierung des L3 in die entstehende Lücke.

dekaisi

Grand Admiral Special

- Mitglied seit

- 06.11.2006

- Beiträge

- 3.929

- Renomée

- 25

- Standort

- B

- Mein Laptop

- Lenovo Y50-70,32GB Ram, Samsung 830Pro 256GB, Panel Upgrade,...

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 3950X

- Mainboard

- ROG Strix X570-E

- Kühlung

- Corsair H115i Platinium

- Speicher

- 4x G.Skill F4-3600C15-8GTZ (B-Die)

- Grafikprozessor

- MSI Trio X 3090

- Display

- Predator X27, Asus MQ270Q

- SSD

- sehr viele :D

- HDD

- viele viele und extra Platz :D

- Optisches Laufwerk

- LG Bluray BH10LS30

- Soundkarte

- Soundblaster X7, Steinberg UR-22C

- Gehäuse

- Corsair Vengeance v70 +Dämmung

- Netzteil

- Enermax Platimax D.F. 600W

- Tastatur

- Corsair RGB Platinum K95

- Maus

- Asus ROG Pugio

- Betriebssystem

- Win10 Prof Workstation

Mit dem aktuellen K10 wäre das ein Albtraum für AMD.

Wenn AMD schon nicht genügend K10 derzeit liefern kann, wie soll es dann um die Lieferbarkeit des hypothetischen 2x Quadcore bestellt sein?

Für 2009 hingegen ist dagegen ein nativer Octacore geplant, was mit 45 nm auch realistisch zu schaffen ist.

MFG Bobo(2007)

?? wo steht das?

wenn man ihre Verfügarkeit anschaut wird man auch sehen, es sind genug vorhanden.

Zudem ist noch genug Potential für Herstellung vorhanden, auch wenn ja bekanntlich FAB30 nun seine Lichter ausschaltet und FAB38 kommt.

45nm wird wohl eher das Problem sein.

Siehe der Die ist bei 65nm riesig, selbst bei 45nm ist ein Quad noch recht groß im Vergleich zu einem 65nm Dual.

Daran wird es scheitern, bzw an der dann estimmt schlechten Ausbeute.

AMD: Wieso kein Octacore

weil sie schon keinen vernünftigen quad hinbekommen ??

SPINA

Grand Admiral Special

- Mitglied seit

- 07.12.2003

- Beiträge

- 18.122

- Renomée

- 985

- Mein Laptop

- Lenovo IdeaPad Gaming 3 (15ARH05-82EY003NGE)

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- ASUS PRIME X370-PRO

- Kühlung

- AMD Wraith Prism

- Speicher

- 2x Micron 32GB PC4-25600E (MTA18ASF4G72AZ-3G2R)

- Grafikprozessor

- Sapphire Pulse Radeon RX 7600 8GB

- Display

- LG Electronics 27UD58P-B

- SSD

- Samsung 980 PRO (MZ-V8P1T0CW)

- HDD

- 2x Samsung 870 QVO (MZ-77Q2T0BW)

- Optisches Laufwerk

- HL Data Storage BH16NS55

- Gehäuse

- Lian Li PC-7NB

- Netzteil

- Seasonic PRIME Gold 650W

- Betriebssystem

- Debian 12.x (x86-64)

- Verschiedenes

- ASUS TPM-M R2.0

Da gibt es sogar eine ganze Riege an gut laufenden Quad-Core Prozessoren aus dem Hause AMD:weil sie schon keinen vernünftigen quad hinbekommen ??

http://products.amd.com/en-us/OpteronCPUFilter.aspx?f1=Third-Generation+AMD+Opteron™

Bobo_Oberon

Grand Admiral Special

- Mitglied seit

- 18.01.2007

- Beiträge

- 5.045

- Renomée

- 190

Ich bitte dich auch Ergänzungen dazu von mir BITTE zur Kenntnis zu nehmen.?? wo steht das?

MFG Bokill

dekaisi

Grand Admiral Special

- Mitglied seit

- 06.11.2006

- Beiträge

- 3.929

- Renomée

- 25

- Standort

- B

- Mein Laptop

- Lenovo Y50-70,32GB Ram, Samsung 830Pro 256GB, Panel Upgrade,...

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 3950X

- Mainboard

- ROG Strix X570-E

- Kühlung

- Corsair H115i Platinium

- Speicher

- 4x G.Skill F4-3600C15-8GTZ (B-Die)

- Grafikprozessor

- MSI Trio X 3090

- Display

- Predator X27, Asus MQ270Q

- SSD

- sehr viele :D

- HDD

- viele viele und extra Platz :D

- Optisches Laufwerk

- LG Bluray BH10LS30

- Soundkarte

- Soundblaster X7, Steinberg UR-22C

- Gehäuse

- Corsair Vengeance v70 +Dämmung

- Netzteil

- Enermax Platimax D.F. 600W

- Tastatur

- Corsair RGB Platinum K95

- Maus

- Asus ROG Pugio

- Betriebssystem

- Win10 Prof Workstation

ja ja,

ich meinte

"Mit dem aktuellen K10 wäre das ein Albtraum für AMD.

Wenn AMD schon nicht genügend K10 derzeit liefern kann, wie soll es dann um die Lieferbarkeit des hypothetischen 2x Quadcore bestellt sein?"

Die Teile laufen und für einen Normalanwender ist der Fehler völlig irrelevant.

Zudem hat AMD beim Quad keine Lieferprobleme, zumindest noch nicht gehabt

.

.Denke mit der jetzigen Designänderung, siehe TLB Bug, wird bestimmt einiges hängen, siehe Sie müssen ja bestimmt erstmal eine Verbesserung implimentieren.

Da in fast allen Shops welche Lieferbar sind und gut gekauft werden kann man diesemal nicht von Lieferproblemen sprechen, wie noch 2006 Winter bei 65nm Einführung

rkinet

Grand Admiral Special

http://www.planet3dnow.de/cgi-bin/newspub/viewnews.cgi?id=1197635692

Im Prinzip ein tolles Design, aber für 45nm wirds bei der TDP verdammt eng.

So etwas in 32nm - durchaus auf der IBM-Fab Mitte 2009 - würde Sinn machen.

Die Quad-Variante könnte ja in 45nm in DD gefertigt werden.

AMD könnte sich so bis weit in 2010/1 Zeit lassen mit 32nm als Mainstream-Prozess und trotzdem den Okta-Core mit attraktiven Parametern ferigen.

Im Prinzip ein tolles Design, aber für 45nm wirds bei der TDP verdammt eng.

So etwas in 32nm - durchaus auf der IBM-Fab Mitte 2009 - würde Sinn machen.

Die Quad-Variante könnte ja in 45nm in DD gefertigt werden.

AMD könnte sich so bis weit in 2010/1 Zeit lassen mit 32nm als Mainstream-Prozess und trotzdem den Okta-Core mit attraktiven Parametern ferigen.

cumec

Admiral Special

- Mitglied seit

- 03.05.2006

- Beiträge

- 1.305

- Renomée

- 19

- Standort

- Schüttorf / Niedersachsen

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- Simap, Spin

- Lieblingsprojekt

- Simap

- Meine Systeme

- Phenom X4 @ 3000MHz

- BOINC-Statistiken

- Folding@Home-Statistiken

- Details zu meinem Desktop

- Prozessor

- Phenom II X6 1075T @ 3900MHz

- Mainboard

- Gigabyte MA790GP-DS4H

- Kühlung

- Gelid Tranquillo

- Speicher

- 8GB PC 800

- Grafikprozessor

- Saphire HD4850 - 512mb

- Display

- ViewSonic VA2216w / Eizo Flexscan L695

- HDD

- 64GB OCZ Agility 2 / 1TB Samsung F3

- Optisches Laufwerk

- Samsung DVD-ROM 16x

- Soundkarte

- Onboard

- Gehäuse

- Chieftec Bravo BA-01

- Netzteil

- be quiet! Straight Power E5 500W

- Betriebssystem

- Win7 Professional 64bit / Ubuntu 64bit

- Webbrowser

- Fox 4

http://www.planet3dnow.de/cgi-bin/newspub/viewnews.cgi?id=1197635692

Im Prinzip ein tolles Design, aber für 45nm wirds bei der TDP verdammt eng.

So etwas in 32nm - durchaus auf der IBM-Fab Mitte 2009 - würde Sinn machen.

Die Quad-Variante könnte ja in 45nm in DD gefertigt werden.

AMD könnte sich so bis weit in 2010/1 Zeit lassen mit 32nm als Mainstream-Prozess und trotzdem den Okta-Core mit attraktiven Parametern ferigen.

Ja sicher... Sie verschieben einfach 32nm und lassen bei IBM fremdfertigen. Und selber bringen sie 32nm wenn der 22nm Prozess verfügbar ist. Sorry, aber das wäre ökonomischer sowie technischer Blödsinn...

Bobo_Oberon

Grand Admiral Special

- Mitglied seit

- 18.01.2007

- Beiträge

- 5.045

- Renomée

- 190

Als Antwort auf einen anderen (unnötigen neueren Thread).

Bislang hat jeder Athlon 64 X2 zwei Speichercontroller, das gilt auch für den K10, wenngleich der den gaged/ungaged-Modus zusätzlich kennt.

Es wäre technisch ebenso machbar, statt der "Xfire"-Bandbreite (also die gesamte Bandbreite des Speicherkontrollers über den HyperTransport-Link für einen weiter entfernten Prozessorkern), dass jeder Kern ein 64 Bit Speicherinterface freigeschaltet hat (statt des 128 Bit breiten internen Speicher-Interfaces) und in der Summe nach aussen hin ein derartiger "Quadcore" ein 128 Bit breites Speicherinterface hat.

Und selbst wenn, die Bandbreite mit dem "Swift" wird potenziell höher wegen DDR3-RAM sein.

Quelle

Ich denke, AMD hält sich hier alle Optionen offen. Gut möglich, dass die einzelnen Kernbestandteile modular sind, so dass es ein gemeinsames Speicherinterface für zwei "zusammengepappte" Quadcores gibt. Das Sandtiger-Modell vom Sommer 2007

ist in diesem Sinne durchaus noch nicht veraltet. -> Aus Raider wird Twix

ist in diesem Sinne durchaus noch nicht veraltet. -> Aus Raider wird Twix

Quelle

MFG Bobo(2007)

Bislang hat jeder Athlon 64 X2 zwei Speichercontroller, das gilt auch für den K10, wenngleich der den gaged/ungaged-Modus zusätzlich kennt.

Es wäre technisch ebenso machbar, statt der "Xfire"-Bandbreite (also die gesamte Bandbreite des Speicherkontrollers über den HyperTransport-Link für einen weiter entfernten Prozessorkern), dass jeder Kern ein 64 Bit Speicherinterface freigeschaltet hat (statt des 128 Bit breiten internen Speicher-Interfaces) und in der Summe nach aussen hin ein derartiger "Quadcore" ein 128 Bit breites Speicherinterface hat.

Und selbst wenn, die Bandbreite mit dem "Swift" wird potenziell höher wegen DDR3-RAM sein.

Quelle

Ich denke, AMD hält sich hier alle Optionen offen. Gut möglich, dass die einzelnen Kernbestandteile modular sind, so dass es ein gemeinsames Speicherinterface für zwei "zusammengepappte" Quadcores gibt. Das Sandtiger-Modell vom Sommer 2007

Quelle

MFG Bobo(2007)

Zuletzt bearbeitet:

Ähnliche Themen

- Antworten

- 0

- Aufrufe

- 456

- Antworten

- 4

- Aufrufe

- 5K

- Antworten

- 101

- Aufrufe

- 14K

- Antworten

- 0

- Aufrufe

- 52K

- Antworten

- 22

- Aufrufe

- 9K