App installieren

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: This feature may not be available in some browsers.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

AMD Zen - 14nm, 8 Kerne, 95W TDP & DDR4?

- Ersteller UNRUHEHERD

- Erstellt am

BoMbY

Grand Admiral Special

- Mitglied seit

- 22.11.2001

- Beiträge

- 7.468

- Renomée

- 293

- Standort

- Aachen

- Details zu meinem Desktop

- Prozessor

- Ryzen 3700X

- Mainboard

- Gigabyte X570 Aorus Elite

- Kühlung

- Noctua NH-U12A

- Speicher

- 2x16 GB, G.Skill F4-3200C14D-32GVK @ 3600 16-16-16-32-48-1T

- Grafikprozessor

- RX 5700 XTX

- Display

- Samsung CHG70, 32", 2560x1440@144Hz, FreeSync2

- SSD

- AORUS NVMe Gen4 SSD 2TB, Samsung 960 EVO 1TB, Samsung 840 EVO 1TB, Samsung 850 EVO 512GB

- Optisches Laufwerk

- Sony BD-5300S-0B (eSATA)

- Gehäuse

- Phanteks Evolv ATX

- Netzteil

- Enermax Platimax D.F. 750W

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox

Schon mal was von Sockel 1156, 1150 der 1151 gehört oder gelesen?

Und zum Preis: So teuer ist ein Celeron G3900 nun auch wieder nicht.

Ah ja?

Welcher AM1 Kabini kann denn ECC?

Lesen und verstehen ist nicht so Deine Stärke, oder?

WindHund

Grand Admiral Special

- Mitglied seit

- 30.01.2008

- Beiträge

- 12.225

- Renomée

- 536

- Standort

- Im wilden Süden (0711)

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- NumberFields@home

- Lieblingsprojekt

- none, try all

- Meine Systeme

- RYZEN R9 3900XT @ ASRock Taichi X570 & ASUS RX Vega64

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5950X

- Mainboard

- ASRock 570X Taichi P5.05 Certified

- Kühlung

- AlphaCool Eisblock XPX, 366x40mm Radiator 6l Brutto m³

- Speicher

- 2x 16 GiB DDR4-3600 CL26 Kingston (Dual Rank, unbuffered ECC)

- Grafikprozessor

- 1x ASRock Radeon RX 6950XT Formula OC 16GByte GDDR6 VRAM

- Display

- SAMSUNG Neo QLED QN92BA 43" up to 4K@144Hz FreeSync PP HDR10+

- SSD

- WD_Black SN850 PCI-Express 4.0 NVME

- HDD

- 3 Stück

- Optisches Laufwerk

- 1x HL-DT-ST BD-RE BH10LS30 SATA2

- Soundkarte

- HD Audio (onboard)

- Gehäuse

- SF-2000 Big Tower

- Netzteil

- Corsair RM1000X (80+ Gold)

- Tastatur

- Habe ich

- Maus

- Han I

- Betriebssystem

- Windows 10 x64 Professional (up to date!)

- Webbrowser

- @Chrome.Google & Edge Chrome

Gerade weil ECC Zusätzliche Leiterbahnen benötigt auf dem Mainboard, finde ich es gut das es getrennt wird (Desktop/Workstation)Ja, stimmt. Wie konnte ich nur die Möglichkeit von C232-Chipsatz mit Xeon E3 außer Acht lassen ... Wobei Xeon jetzt nicht unbedingt als Desktop-CPU zählt bei Intel, und wenn der was schneller sein soll, dann darfst Du auch ordentlich bezahlen, selbst für einen Vierkerner.

Aus dem BKDG Seite 189:Ohne ECC findet man die Fehler quasi nicht, und wenn ECC zuschlägt gibt es normalerweise eine "Maschinen Prüfungs Ausnahme"

Insgesamt habe ich 4 zusätzliche Speicher Chips (zwei auf jedem DRAM Riegel)In certain configurations, the ECC provides single DRAM device data correction, known as “chipkill” functionality; all single symbol errors caused by a failed DRAM device are corrected. Chipkill recovery is only

possible when indicated by D18F3x44[ChipKillEccCap] and all bits within a symbol are sourced from a single

DRAM device.

Zuletzt bearbeitet:

bschicht86

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 14.12.2006

- Beiträge

- 4.249

- Renomée

- 228

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- 2950X

- Mainboard

- X399 Taichi

- Kühlung

- Heatkiller IV Pure Chopper

- Speicher

- 64GB 3466 CL16

- Grafikprozessor

- 2x Vega 64 @Heatkiller

- Display

- Asus VG248QE

- SSD

- PM981, SM951, ein paar MX500 (~5,3TB)

- HDD

- -

- Optisches Laufwerk

- 1x BH16NS55 mit UHD-BD-Mod

- Soundkarte

- Audigy X-Fi Titanium Fatal1ty Pro

- Gehäuse

- Chieftec

- Netzteil

- Antec HCP-850 Platinum

- Betriebssystem

- Win7 x64, Win10 x64

- Webbrowser

- Firefox

- Verschiedenes

- LS120 mit umgebastelten USB -> IDE (Format wie die gängigen SATA -> IDE)

Insgesamt habe ich 4 zusätzliche Speicher Chips (zwei auf jeder DRAM Seite)

Meinst du insgesamt? Oder reg. ECC? Weil bei normalen ECC-Riegeln wären das höchstens 2 Zusatz-Chips bei insgesamt 18 Chips.

WindHund

Grand Admiral Special

- Mitglied seit

- 30.01.2008

- Beiträge

- 12.225

- Renomée

- 536

- Standort

- Im wilden Süden (0711)

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- NumberFields@home

- Lieblingsprojekt

- none, try all

- Meine Systeme

- RYZEN R9 3900XT @ ASRock Taichi X570 & ASUS RX Vega64

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5950X

- Mainboard

- ASRock 570X Taichi P5.05 Certified

- Kühlung

- AlphaCool Eisblock XPX, 366x40mm Radiator 6l Brutto m³

- Speicher

- 2x 16 GiB DDR4-3600 CL26 Kingston (Dual Rank, unbuffered ECC)

- Grafikprozessor

- 1x ASRock Radeon RX 6950XT Formula OC 16GByte GDDR6 VRAM

- Display

- SAMSUNG Neo QLED QN92BA 43" up to 4K@144Hz FreeSync PP HDR10+

- SSD

- WD_Black SN850 PCI-Express 4.0 NVME

- HDD

- 3 Stück

- Optisches Laufwerk

- 1x HL-DT-ST BD-RE BH10LS30 SATA2

- Soundkarte

- HD Audio (onboard)

- Gehäuse

- SF-2000 Big Tower

- Netzteil

- Corsair RM1000X (80+ Gold)

- Tastatur

- Habe ich

- Maus

- Han I

- Betriebssystem

- Windows 10 x64 Professional (up to date!)

- Webbrowser

- @Chrome.Google & Edge Chrome

Insgesamt, pro Riegel zwei oder pro Seite ein zusätzlicher Chip: 1024M x 72 (2 ranks)Meinst du insgesamt? Oder reg. ECC? Weil bei normalen ECC-Riegeln wären das höchstens 2 Zusatz-Chips bei insgesamt 18 Chips.

1 zusätzliches Bit pro 8 Bits, das macht den Kohl nicht fett.Gerade weil ECC Zusätzliche Leiterbahnen benötigt auf dem Mainboard, finde ich es gut das es getrennt wird (Desktop/Workstation)

Ja, es wird korrigiert. Es gibt dann einen Eintrag im Syslog welcher Riegel das war, wenn die Maschine richtig konfiguriert wurde. Ohne ECC merkt man es möglicherweise nicht oder zu spät!Aus dem BKDG Seite 189:

In certain configurations, the ECC provides single DRAM device data correction, known as “chipkill” functionality; all single symbol errors caused by a failed DRAM device are corrected. Chipkill recovery is only

possible when indicated by D18F3x44[ChipKillEccCap] and all bits within a symbol are sourced from a single

DRAM device.

Stefan Payne

Grand Admiral Special

1150 mit Core i3 zum Beispiel.Welche Desktop-Plattform von Intel kann denn ECC?

Oder 1151 mit Celeron zum Beispiel.[3DC]Payne;5095639 schrieb:1150 mit Core i3 zum Beispiel.

Aber lesen und verstehen ist nicht so meine Stärke...

amdfanuwe

Grand Admiral Special

- Mitglied seit

- 24.06.2010

- Beiträge

- 2.372

- Renomée

- 34

- Details zu meinem Desktop

- Prozessor

- 4200+

- Mainboard

- M3A-H/HDMI

- Kühlung

- ein ziemlich dicker

- Speicher

- 2GB

- Grafikprozessor

- onboard

- Display

- Samsung 20"

- HDD

- WD 1,5TB

- Netzteil

- Extern 100W

- Betriebssystem

- XP, AndLinux

- Webbrowser

- Firefox

- Verschiedenes

- Kaum hörbar

Mit welchem Board?

BoMbY

Grand Admiral Special

- Mitglied seit

- 22.11.2001

- Beiträge

- 7.468

- Renomée

- 293

- Standort

- Aachen

- Details zu meinem Desktop

- Prozessor

- Ryzen 3700X

- Mainboard

- Gigabyte X570 Aorus Elite

- Kühlung

- Noctua NH-U12A

- Speicher

- 2x16 GB, G.Skill F4-3200C14D-32GVK @ 3600 16-16-16-32-48-1T

- Grafikprozessor

- RX 5700 XTX

- Display

- Samsung CHG70, 32", 2560x1440@144Hz, FreeSync2

- SSD

- AORUS NVMe Gen4 SSD 2TB, Samsung 960 EVO 1TB, Samsung 840 EVO 1TB, Samsung 850 EVO 512GB

- Optisches Laufwerk

- Sony BD-5300S-0B (eSATA)

- Gehäuse

- Phanteks Evolv ATX

- Netzteil

- Enermax Platimax D.F. 750W

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox

Oder 1151 mit Celeron zum Beispiel.

Aber lesen und verstehen ist nicht so meine Stärke...

Nein, ist es nicht. Denn ich sagte Desktop. Mir ist kein aktueller Chipsatz von Intel bekannt, welcher ECC kann und als Desktop deklariert wird. Ebenso ist mir keine aktuelle CPU von Intel bekannt, welche ECC unterstützt und als Desktop deklariert wird.

Ebenso sagte ich nicht, dass AM1 ECC unterstützt. Ich sage, dass Kabini ECC unterstützt - und das tut er sehr wohl - auf FT3, und eben nicht auf AM1.

IT-Extremist

Gesperrt

- Mitglied seit

- 09.12.2015

- Beiträge

- 225

- Renomée

- 1

Z. B.Mit welchem Board?

Gigabyte GA-X150M-PRO ECC.

--- Update ---

Lesen und verstehen ist nicht so deine Stärke

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 14.348

- Renomée

- 1.975

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 3950X

- Mainboard

- MSI MPG X570 GAMING PRO CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 4x 16 GB G.Skill Trident Z RGB, DDR4-3200, CL14

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Intel 600p 1TB

- HDD

- Western Digital WD Red 2 & 3TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

Das lustige an der Sache ist doch das Modelle wie der Core™ i7-6700K keinen ECC Support mehr besitzen und deshalb die Frage wieviel davon durch das Mainboard übrig bleibt durchaus berechtigt ist.

BoMbY

Grand Admiral Special

- Mitglied seit

- 22.11.2001

- Beiträge

- 7.468

- Renomée

- 293

- Standort

- Aachen

- Details zu meinem Desktop

- Prozessor

- Ryzen 3700X

- Mainboard

- Gigabyte X570 Aorus Elite

- Kühlung

- Noctua NH-U12A

- Speicher

- 2x16 GB, G.Skill F4-3200C14D-32GVK @ 3600 16-16-16-32-48-1T

- Grafikprozessor

- RX 5700 XTX

- Display

- Samsung CHG70, 32", 2560x1440@144Hz, FreeSync2

- SSD

- AORUS NVMe Gen4 SSD 2TB, Samsung 960 EVO 1TB, Samsung 840 EVO 1TB, Samsung 850 EVO 512GB

- Optisches Laufwerk

- Sony BD-5300S-0B (eSATA)

- Gehäuse

- Phanteks Evolv ATX

- Netzteil

- Enermax Platimax D.F. 750W

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox

Z. B.

Gigabyte GA-X150M-PRO ECC.

--- Update ---

Lesen und verstehen ist nicht so deine Stärkedenn laut BoMbY brauchst du bei Intel für ECC mindestens 2011-3.

Auf den Rest gehst Du natürlich nicht ein ... abgesehen davon, woher soll man wissen, dass es irgendwelche 2-Kern CPUs mit ECC gibt, während alle normalen Desktop-CPUs das nicht unterstützen? Und Du brauchst immer noch einen Server/Workstation Chipsatz.

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 14.348

- Renomée

- 1.975

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 3950X

- Mainboard

- MSI MPG X570 GAMING PRO CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 4x 16 GB G.Skill Trident Z RGB, DDR4-3200, CL14

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Intel 600p 1TB

- HDD

- Western Digital WD Red 2 & 3TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

Das ist ja der Witz an der Sache. Das besagte Gigabyte GA-X150M-PRO ECC steht bei Geizhals bei den Xeon Boards und das dürfte auch der Grund sein warum die i5 und i7 Modelle es auf einmal nicht mehr beherrschen. Die Kundschaft soll dann gefälligst die Xeons kaufen.

Dresdenboy

Redaktion

☆☆☆☆☆☆

Ist es OK, dass ich wegen Fußball nur mal Copy Paste?

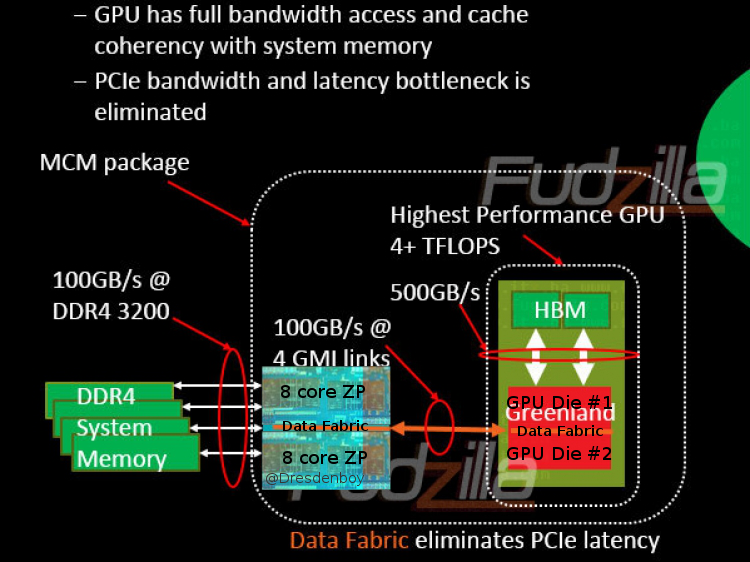

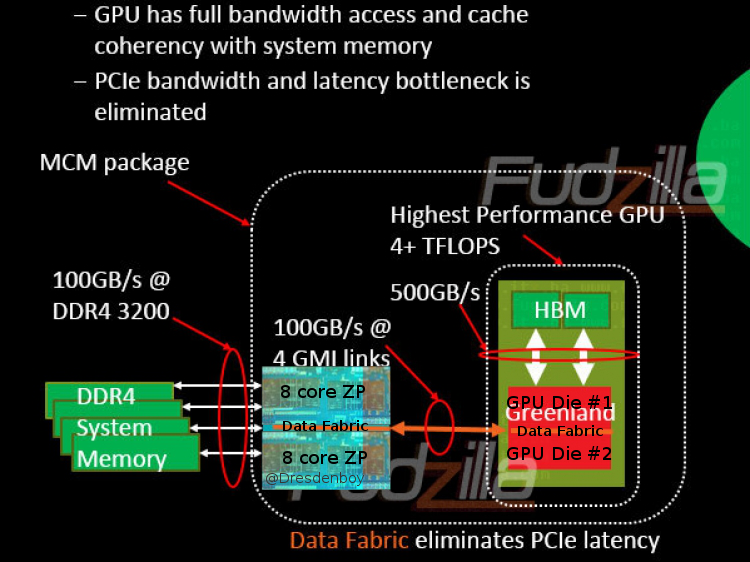

A thought about the 8C Zeppelin die:

I reported about the "Zeppelin" CPU first, in combination with the 32C limit per socket. This and the Fudzilla slide led to assumptions that 32C would be 2 Zeppelins -> 16C/ZP assumed with 4 DDR channels per die.

SR die leaked and had 8C + 2x DDR4 PHY. Then Lisa held the "ZP" ES into the cameras. 8C SR called "ZP" -> cognitive dissonance.

Looking at the Fudzilla slide again I found the riddle's solution: The blue Zeppelin box are actually 2 boxes divided by an orange line, which stands for the data fabric. The same for the Greenland GPU. So that are 2 ZP dies! And 2 GPU dies (possibly some small Vega die with 1 HBM2 PHY).

A thought about the 8C Zeppelin die:

I reported about the "Zeppelin" CPU first, in combination with the 32C limit per socket. This and the Fudzilla slide led to assumptions that 32C would be 2 Zeppelins -> 16C/ZP assumed with 4 DDR channels per die.

SR die leaked and had 8C + 2x DDR4 PHY. Then Lisa held the "ZP" ES into the cameras. 8C SR called "ZP" -> cognitive dissonance.

Looking at the Fudzilla slide again I found the riddle's solution: The blue Zeppelin box are actually 2 boxes divided by an orange line, which stands for the data fabric. The same for the Greenland GPU. So that are 2 ZP dies! And 2 GPU dies (possibly some small Vega die with 1 HBM2 PHY).

amdfanuwe

Grand Admiral Special

- Mitglied seit

- 24.06.2010

- Beiträge

- 2.372

- Renomée

- 34

- Details zu meinem Desktop

- Prozessor

- 4200+

- Mainboard

- M3A-H/HDMI

- Kühlung

- ein ziemlich dicker

- Speicher

- 2GB

- Grafikprozessor

- onboard

- Display

- Samsung 20"

- HDD

- WD 1,5TB

- Netzteil

- Extern 100W

- Betriebssystem

- XP, AndLinux

- Webbrowser

- Firefox

- Verschiedenes

- Kaum hörbar

4+ Teraflops, da sollte 2*P11 ja schon mehr bringen. Wenn das Vega sein soll, macht es da nicht mehr Sinn diesen zwischen P10 und P11 anzusiedeln?

Oder gibt es den später noch mit einer 8Core ZEN APU mit 1* HBM2? Also die Hälfte des obigen Bildes. Dürfte dann so <=1024 Shader haben.

Macht aber irgenwie keinen Sinn. Für aktuelle Tätigkeiten außer Zocken reicht eine native 4Core ZEN APU.

Zocken und VR fängt mit P10 erst an Spaß zu machen.

Das system auf obigem Bild ist wohl mehr für Workstations bzw. Server (Numbercruncher) gedacht.

Da wäre es Sinnvoller gleich den 16Core Server ZEN zu verwenden. Über die Data Fabric kann dann wahlweise auf einem Träger ein 32 Core SOC oder ein 16 Core + Greenland realisiert werden. Um die TDP nicht zu hoch zu treiben, dürfte Greenland etwas kleiner als P10 ausfallen.

Oder sind 4 Teraflops double precision gedacht? Dann könnte es Vega 10 sein, nur frage ich mich da, wie die TDP des Chips aussehen wird.

140W dürfte ja schon 16C ZEN alleine brauchen, wenn man den was aufdreht und 4 Teraflop double dürfte auch mit VEGA kaum unter 100W verschlingen.

Oder gibt es den später noch mit einer 8Core ZEN APU mit 1* HBM2? Also die Hälfte des obigen Bildes. Dürfte dann so <=1024 Shader haben.

Macht aber irgenwie keinen Sinn. Für aktuelle Tätigkeiten außer Zocken reicht eine native 4Core ZEN APU.

Zocken und VR fängt mit P10 erst an Spaß zu machen.

Das system auf obigem Bild ist wohl mehr für Workstations bzw. Server (Numbercruncher) gedacht.

Da wäre es Sinnvoller gleich den 16Core Server ZEN zu verwenden. Über die Data Fabric kann dann wahlweise auf einem Träger ein 32 Core SOC oder ein 16 Core + Greenland realisiert werden. Um die TDP nicht zu hoch zu treiben, dürfte Greenland etwas kleiner als P10 ausfallen.

Oder sind 4 Teraflops double precision gedacht? Dann könnte es Vega 10 sein, nur frage ich mich da, wie die TDP des Chips aussehen wird.

140W dürfte ja schon 16C ZEN alleine brauchen, wenn man den was aufdreht und 4 Teraflop double dürfte auch mit VEGA kaum unter 100W verschlingen.

Dresdenboy

Redaktion

☆☆☆☆☆☆

Ich denke mal, es wird ein Vega-Ableger einfach schon wegen HBM-Anbindung u. double precision performance. Apropos: Da steht auch nicht, ob DP oder SP TFLOPS. Erstere interessieren in dem Markt eher.4+ Teraflops, da sollte 2*P11 ja schon mehr bringen. Wenn das Vega sein soll, macht es da nicht mehr Sinn diesen zwischen P10 und P11 anzusiedeln?

Oder gibt es den später noch mit einer 8Core ZEN APU mit 1* HBM2? Also die Hälfte des obigen Bildes. Dürfte dann so <=1024 Shader haben.

Macht aber irgenwie keinen Sinn. Für aktuelle Tätigkeiten außer Zocken reicht eine native 4Core ZEN APU.

Zocken und VR fängt mit P10 erst an Spaß zu machen.

Das system auf obigem Bild ist wohl mehr für Workstations bzw. Server (Numbercruncher) gedacht.

Da wäre es Sinnvoller gleich den 16Core Server ZEN zu verwenden. Über die Data Fabric kann dann wahlweise auf einem Träger ein 32 Core SOC oder ein 16 Core + Greenland realisiert werden. Um die TDP nicht zu hoch zu treiben, dürfte Greenland etwas kleiner als P10 ausfallen.

Oder sind 4 Teraflops double precision gedacht? Dann könnte es Vega 10 sein, nur frage ich mich da, wie die TDP des Chips aussehen wird.

140W dürfte ja schon 16C ZEN alleine brauchen, wenn man den was aufdreht und 4 Teraflop double dürfte auch mit VEGA kaum unter 100W verschlingen.

Aber wir haben hier ja auch schon bzgl. Interposer/MCM spekuliert, ob es nicht einfach mehr von den 8C Dies sind. Dann passt es auch mit den Mem Channels, spart Entwicklungs-/Herstellungs-Kosten, erlaubt besseres Binning...

Opteron

Redaktion

☆☆☆☆☆☆

@Dresdenboy:

Ja das Bildchen mit Zeppelin und der Name hatten mich auch gestört. 2 Dies könnten es natürlich sein, wobei dann wieder die Frage aufkommt, ob die Cern Info nicht doch falsch war und AMD nur 8core-Dies fabriziert. Entweder das, oder der 16core kommt in Intelmanier erst 1 Jahr später. Würde schon allein aufgrund der Prozessqualität Sinn machen. Außerdem kann man dann Intel-untypisch auch gleich Zen_v2-Cores verbauen.

@amdfanuwe: TDP ist kein Problem, für so nen Serverchip muss man sich dann halt nur jeweils die allerbesten Dies aussuchen. Von Bulldozer gabs z.B. auch low-power Opterons mit 25W. Mit Zen dürfte das Dank 14nm Finfet und der besseren Architektur mit all den Sensoren noch besser funktionieren, sieht man ja auch schon an der Excavator-Architektur was man da am Core selbst noch alles rausholen konnte. Stell Dir sowas mal mit ner noch sparsameren Architektur vor, die Zen zweifelsohne werden wird ...

Ja das Bildchen mit Zeppelin und der Name hatten mich auch gestört. 2 Dies könnten es natürlich sein, wobei dann wieder die Frage aufkommt, ob die Cern Info nicht doch falsch war und AMD nur 8core-Dies fabriziert. Entweder das, oder der 16core kommt in Intelmanier erst 1 Jahr später. Würde schon allein aufgrund der Prozessqualität Sinn machen. Außerdem kann man dann Intel-untypisch auch gleich Zen_v2-Cores verbauen.

@amdfanuwe: TDP ist kein Problem, für so nen Serverchip muss man sich dann halt nur jeweils die allerbesten Dies aussuchen. Von Bulldozer gabs z.B. auch low-power Opterons mit 25W. Mit Zen dürfte das Dank 14nm Finfet und der besseren Architektur mit all den Sensoren noch besser funktionieren, sieht man ja auch schon an der Excavator-Architektur was man da am Core selbst noch alles rausholen konnte. Stell Dir sowas mal mit ner noch sparsameren Architektur vor, die Zen zweifelsohne werden wird ...

OBrian

Moderation MBDB, ,

- Mitglied seit

- 16.10.2000

- Beiträge

- 17.033

- Renomée

- 267

- Standort

- NRW

- Details zu meinem Desktop

- Prozessor

- Phenom II X4 940 BE, C2-Stepping (undervolted)

- Mainboard

- Gigabyte GA-MA69G-S3H (BIOS F7)

- Kühlung

- Noctua NH-U12F

- Speicher

- 4 GB DDR2-800 ADATA/OCZ

- Grafikprozessor

- Radeon HD 5850

- Display

- NEC MultiSync 24WMGX³

- SSD

- Samsung 840 Evo 256 GB

- HDD

- WD Caviar Green 2 TB (WD20EARX)

- Optisches Laufwerk

- Samsung SH-S183L

- Soundkarte

- Creative X-Fi EM mit YouP-PAX-Treibern, Headset: Sennheiser PC350

- Gehäuse

- Coolermaster Stacker, 120mm-Lüfter ersetzt durch Scythe S-Flex, zusätzliche Staubfilter

- Netzteil

- BeQuiet 500W PCGH-Edition

- Betriebssystem

- Windows 7 x64

- Webbrowser

- Firefox

- Verschiedenes

- Tastatur: Zowie Celeritas Caseking-Mod (weiße Tasten)

Zwei 8er könnte man zusammenkleben, aber wenn man einen nativen 16c macht, kann man da auch gleich L3-Cache mit draufbauen, das ist evtl. sinnvoller. So eine Wahnsinns-Diefläche ergibt das ja auch noch nicht. Da könnte man auch weitere Serverfeatures gleich mit draufpacken, z.B. dickes I/O, irgendwelche Managementgeschichten usw.

Bei zwei eingezeichneten HBM-Stacks, was ja wohl HBM2 sein wird, wenn der Chip erst in noch nicht mal absehbarer Zukunft kommen soll, ergibt sich eine Bandbreite, die ungefähr im Bereich von Fiji liegt. Also kann man wohl auch davon ausgehen, daß es ungefähr auch ein ähnlich starker Chip sein wird. Fiji ließ sich auf 175 W drücken (Nano), ersetzt man die GPU durch eine gleichstarke in 14FF, dann ergibt das ungefähr die halbe Abwärme. Also sagen wir mal, mit etwa 80-100 W käme man wohl hin.

Insgesamt mit 16c-CPU sind es also ca. 150-200 W wenigstens, noch weniger wäre wohl nicht so effektiv. So eine TDP ist aber problemlos machbar, auch mehr, man muß es nur spezifizieren. Wichtig ist im Großrechner letztlich ja nur, möglichst viele TFLOPS pro Watt zu erzielen, ob ich dann einen Sockel mit 300 W oder vier mit je 75 W habe, ist egal.

Bei zwei eingezeichneten HBM-Stacks, was ja wohl HBM2 sein wird, wenn der Chip erst in noch nicht mal absehbarer Zukunft kommen soll, ergibt sich eine Bandbreite, die ungefähr im Bereich von Fiji liegt. Also kann man wohl auch davon ausgehen, daß es ungefähr auch ein ähnlich starker Chip sein wird. Fiji ließ sich auf 175 W drücken (Nano), ersetzt man die GPU durch eine gleichstarke in 14FF, dann ergibt das ungefähr die halbe Abwärme. Also sagen wir mal, mit etwa 80-100 W käme man wohl hin.

Insgesamt mit 16c-CPU sind es also ca. 150-200 W wenigstens, noch weniger wäre wohl nicht so effektiv. So eine TDP ist aber problemlos machbar, auch mehr, man muß es nur spezifizieren. Wichtig ist im Großrechner letztlich ja nur, möglichst viele TFLOPS pro Watt zu erzielen, ob ich dann einen Sockel mit 300 W oder vier mit je 75 W habe, ist egal.

amdfanuwe

Grand Admiral Special

- Mitglied seit

- 24.06.2010

- Beiträge

- 2.372

- Renomée

- 34

- Details zu meinem Desktop

- Prozessor

- 4200+

- Mainboard

- M3A-H/HDMI

- Kühlung

- ein ziemlich dicker

- Speicher

- 2GB

- Grafikprozessor

- onboard

- Display

- Samsung 20"

- HDD

- WD 1,5TB

- Netzteil

- Extern 100W

- Betriebssystem

- XP, AndLinux

- Webbrowser

- Firefox

- Verschiedenes

- Kaum hörbar

auch weitere Serverfeatures gleich mit draufpacken, z.B.

Data Fabric.

Und Greenland/Vega auch mit Data Fabric dürfte vornehmlich für den Serverbereich gedacht sein. Dann würde AMD mit obigem MCM den Servermarkt angreifen, in dem aktuell noch dicke diskrete GPUs verbaut werden.

Mal gespannt, ob Polaris ähnlich Maxwell rein auf Gaming setzt.

Dann sähe das AMD Portfolio 2017 wohl so aus:

Bei Bedarf extra Die: ZEN APU 2 Core für Embedded, Kiosk, Thin Clients, günstige Notebooks...

Low End Desktop, Notebooks: ZEN APU 4Core, Athlon 4Core + Polaris

Desktop Zocker: ZEN 8Core + Polaris/Vega dGPU

Server ZEN 16Core + Greenland MCM

Server ZEN 2*16Core MCM + Vega dGPU

Auf Fuddi wird über einen 32 Core Zen berichtet/spekuliert.

http://www.fudzilla.com/news/processors/40888-amd-naples-zen-has-32-cores

Wenn es stimmt was dort steht ist das doch mal ein interessantes Teil. 8 Speicherkanäle, 64 MB L3 cache, 128 Lanes für PCIe, support up to 32 SATA, support for 16x10GbE ..

http://www.fudzilla.com/news/processors/40888-amd-naples-zen-has-32-cores

Wenn es stimmt was dort steht ist das doch mal ein interessantes Teil. 8 Speicherkanäle, 64 MB L3 cache, 128 Lanes für PCIe, support up to 32 SATA, support for 16x10GbE ..

Stefan Payne

Grand Admiral Special

...und mehrere Tausend Euronen pro Package

Crashtest

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 11.11.2008

- Beiträge

- 9.275

- Renomée

- 1.413

- Standort

- Leipzig

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- Collatz, yoyo, radac

- Lieblingsprojekt

- yoyo

- Meine Systeme

- Ryzen: 2x1600, 5x1700, 1x2700,1x3600, 1x5600X; EPYC 7V12 und Kleinzeuch

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Lenovo IdeaPad 5 14ALC05

- Details zu meinem Desktop

- Prozessor

- Ryzen 7950X / Ryzen 4750G

- Mainboard

- ASRock B650M PGRT / X570D4U

- Kühlung

- be quiet! Dark Rock Pro4 / Pure Rock Slim 2

- Speicher

- 64GB DDR5-5600 G Skill F5-5600J3036D16G / 32 GB DDR4-3200 ECC

- Grafikprozessor

- Raphael IGP / ASpeed AST-2500

- Display

- 27" Samsung LF27T450F

- SSD

- KINGSTON SNVS2000G

- HDD

- - / 8x Seagate IronWolf Pro 20TB

- Optisches Laufwerk

- 1x B.Ray - LG BD-RE BH16NS55

- Soundkarte

- onboard HD?

- Gehäuse

- zu kleines für die GPU

- Netzteil

- be quiet! Pure Power 11 400W / dito

- Tastatur

- CHERRY SECURE BOARD 1.0

- Maus

- Logitech RX250

- Betriebssystem

- Windows 10 19045.3996 / Server 20348.2227

- Webbrowser

- Edge 120.0.2210.121

- Verschiedenes

- U320 SCSI-Controller !!!!

- Internetanbindung

- ▼1000 MBit ▲82 MBit

Ich erwarte ein CPU-Preis des 32C/64T Opterons im Bereich 3000 bis 6000 Euro - Intel Xeon E5-2699 v4 kostet auch rd 4200 Euro bei gerade mal 22C/44T

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Also die Marketingvideos für Zen sehen mal gut aus - Doom auf Zen im AMD Testlab:

http://www.pcgameshardware.de/AMD-Zen-Codename-261795/Videos/Doom-Summit-Ridge-1198481/

http://www.pcgameshardware.de/AMD-Zen-Codename-261795/Videos/Doom-Summit-Ridge-1198481/

Ähnliche Themen

- Antworten

- 94

- Aufrufe

- 8K

- Antworten

- 14

- Aufrufe

- 936

- Antworten

- 102

- Aufrufe

- 11K

- Antworten

- 3

- Aufrufe

- 2K