App installieren

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: This feature may not be available in some browsers.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

AMD Zen - 14nm, 8 Kerne, 95W TDP & DDR4?

- Ersteller UNRUHEHERD

- Erstellt am

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 14.324

- Renomée

- 1.971

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 3950X

- Mainboard

- MSI MPG X570 GAMING PRO CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 4x 16 GB G.Skill Trident Z RGB, DDR4-3200, CL14

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Intel 600p 1TB

- HDD

- Western Digital WD Red 2 & 3TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

Hast du dir mal überlegt wie du dann was kühlen willst?

Der Bereich der micro Bumps ist bei meiner Fury vergossen, vermutlich wegen Korrosionsschutz und um mechanische Kräfte besser zu verteilen.

Übertrage das man auf deine Idee einer Stapelei und verrate mir wie man diese Huckel Landschaft dann noch vernünftig kühlen soll ohne eine extra Wurst nach der anderen zu machen, welche den Herstellungspreis noch weiter nach oben schrauben.

Was möglich ist ist nicht auch zwangsläufig sinnvoll oder rentabel.

Der Bereich der micro Bumps ist bei meiner Fury vergossen, vermutlich wegen Korrosionsschutz und um mechanische Kräfte besser zu verteilen.

Übertrage das man auf deine Idee einer Stapelei und verrate mir wie man diese Huckel Landschaft dann noch vernünftig kühlen soll ohne eine extra Wurst nach der anderen zu machen, welche den Herstellungspreis noch weiter nach oben schrauben.

Was möglich ist ist nicht auch zwangsläufig sinnvoll oder rentabel.

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Die Die Slices haben eine Schichthöhe von 0,2 mm. Grafische Abildungen stellen das grober dar.

Ich hätte jetzt gedacht Standardwafer wären etwas dicker (~300 µm), aber OK. Der CPU-/GPU-Dies wären also 200 µm hoch, die Flash-Stapel bei 48 Chips ohne Füllmaterial zwischen den Wafern 9,6 mm hoch. D.h. du brauchst 9,4 mm Füllmaterial über der GPU. Alternativ kann man die Flash-Dies auf ~4,2 µm abdünnen. Beides ist Blödsinn.

Und es hat auch absolut nichts mit Zen zu tun, macht das in eurem Interposer-Whatsoever-Thread aus. Hier geht es um die Zen-Architektur.

Und es hat auch absolut nichts mit Zen zu tun, macht das in eurem Interposer-Whatsoever-Thread aus. Hier geht es um die Zen-Architektur.

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Es geht um falsche Einschätzungen und Zen wird durchaus auf einem Interposer erscheinen. Wenn Fehlinformationen verbreitet werden wirkt sich das direkt auf mögliche Produkte aus.

Ebenso wie du erneut eine Behauptung aufstellst die nicht haltbar ist

Figure 2. 3D-IC with TSVs and inter-layer cooling channels that is enclosed in a sealed manifold.

Wenn Leute immer erzählen was geht und was nicht - da hast sogar eine Wasser(Fuild)kühlung.

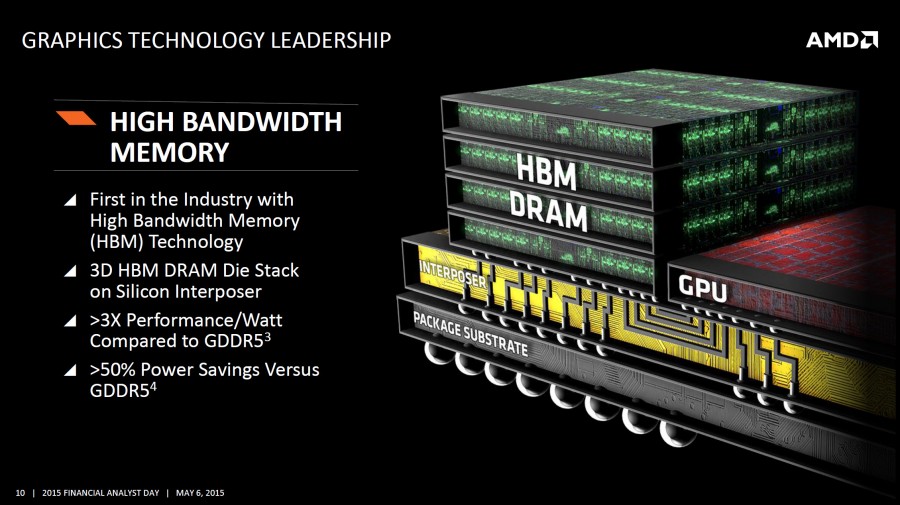

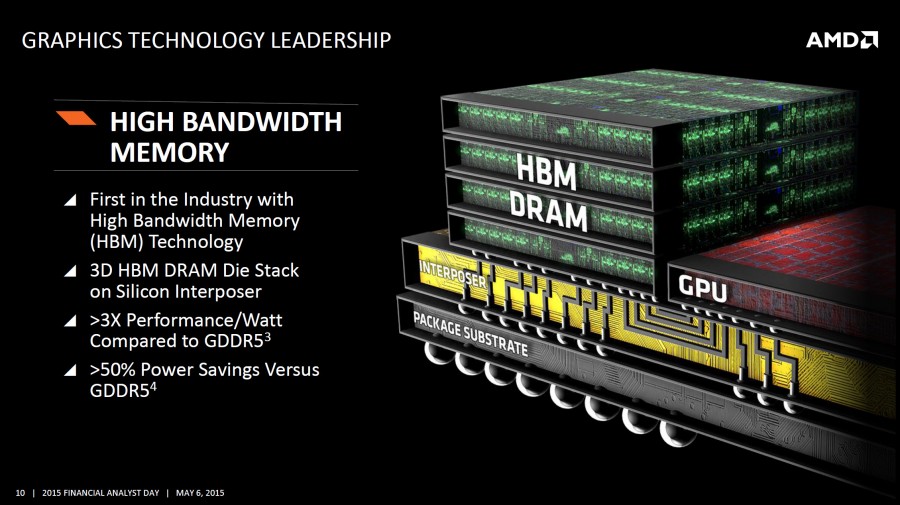

Vielleicht schaut man auch mal genauer auf eine AMD-Folie:

Ebenso wie du erneut eine Behauptung aufstellst die nicht haltbar ist

http://esl.epfl.ch/page-42448-en.htmlD.h. du brauchst 9,4 mm Füllmaterial über der GPU. Alternativ kann man die Flash-Dies auf ~4,2 µm abdünnen. Beides ist Blödsinn.

3D-stack enclosed in sealed manifold with inter-layer cooling manufactured in CMOSAIC

Figure 2. 3D-IC with TSVs and inter-layer cooling channels that is enclosed in a sealed manifold.

Wenn Leute immer erzählen was geht und was nicht - da hast sogar eine Wasser(Fuild)kühlung.

Vielleicht schaut man auch mal genauer auf eine AMD-Folie:

Zuletzt bearbeitet:

cyrusNGC_224

Grand Admiral Special

- Mitglied seit

- 01.05.2014

- Beiträge

- 5.924

- Renomée

- 117

- Aktuelle Projekte

- POGS, Asteroids, Milkyway, SETI, Einstein, Enigma, Constellation, Cosmology

- Lieblingsprojekt

- POGS, Asteroids, Milkyway

- Meine Systeme

- X6 PII 1090T, A10-7850K, 6x Athlon 5350, i7-3632QM, C2D 6400, AMD X4 PII 810, 6x Odroid U3

- BOINC-Statistiken

Allerhöchstens wäre das etwas für den HPC Markt. Für einfache Server oder gar Desktop unpraktibel und wahrscheinlich extrem teuer.

Schon die Fury X mit WaKü war nur etwas für ganz wenige.

Klar, WaKü ist besser, aber auch teurer und unflexibler.

Schon die Fury X mit WaKü war nur etwas für ganz wenige.

Klar, WaKü ist besser, aber auch teurer und unflexibler.

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Wo eine Wakü drauf passt, lässt sich bei weniger TDP wie z.B lediglich 95W stattdessen jedderzeit ein Luftkühler montieren. Es geht ja lediglich um die Befürchtung die "Stufen" beim Die-Stcking könnten da Probleme machen. Dem ist nicht so.

Edit: Es spricht nichts gegen eine Vapor-Chamber die Unebenheiten ausgleicht oder eben leitendes Füllmaterial, falls nötig.

Edit: Es spricht nichts gegen eine Vapor-Chamber die Unebenheiten ausgleicht oder eben leitendes Füllmaterial, falls nötig.

Zuletzt bearbeitet:

NOFX

Grand Admiral Special

- Mitglied seit

- 02.09.2002

- Beiträge

- 4.532

- Renomée

- 287

- Standort

- Brühl

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- Spinhenge

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 5 1600 @Stock

- Mainboard

- ASUS B350M-A

- Kühlung

- Boxed-Kühler

- Speicher

- 2x 8 G.Skill RipJaws 4 rot DDR4-2800 DIMM

- Grafikprozessor

- PowerColor Radeon RX 480 Red Dragon 8GB

- Display

- LG 34UM-68 (FreeSync)

- SSD

- PowerColor Radeon RX 480 Red Dragon 8GB

- HDD

- 1x 1,5TB Seagate S-ATA

- Optisches Laufwerk

- DVD-Brenner

- Soundkarte

- onBoard

- Gehäuse

- Thermaltake Versa H15

- Netzteil

- Cougar SX 460

- Betriebssystem

- Windows 10 Pro x64

- Webbrowser

- Google Chrome

Abgesehen von GPUs und den mobilen ablegern kommen die APUs/CPUs ja eh mit Heatspreader. Da ergibt sich die Frage dann eh nicht, außer des geht wirklich um mehrere Millimeter. Da HBM doch bereits gestapelt ist und trotzdem auf annähernd gleicher Höhe landet wie die Fury-Chips, sollte das kein Problem sein.

Stimmt, man könnte den Kühler von unten mit einem entsprechenden Höhenprofil versehen (und hoffen, dass er wirklich nur auf der CPU-/GPU aufliegt). Die Flash-Zellen werden dann jedoch immer noch warm und halten nicht lange.

ONH

Grand Admiral Special

Oder man verwendet eine board&sip mit Loch und bringt die SSD unten am Interposer an mit separate kühler an. Intel hat doch mal für den Mobilbereich ein ähnliches Produkt geplant um die Dicke zu verringern.

http://www.computerbase.de/bildstrecke/59173/15/

Im Mobilbereich wäre die Anzahl der benötigten Pin ja überschaubar, bliebe nur Strom, 1-2 USB-C, 1x dp/hdmi, x8 pcie übrig. Bei den nicht mobilen Produkten sind der nicht besonders sinnvoll. Wobei das wieder wenig mit Zen zu tun hat.

http://www.computerbase.de/bildstrecke/59173/15/

Im Mobilbereich wäre die Anzahl der benötigten Pin ja überschaubar, bliebe nur Strom, 1-2 USB-C, 1x dp/hdmi, x8 pcie übrig. Bei den nicht mobilen Produkten sind der nicht besonders sinnvoll. Wobei das wieder wenig mit Zen zu tun hat.

Zuletzt bearbeitet:

IT-Extremist

Gesperrt

- Mitglied seit

- 09.12.2015

- Beiträge

- 225

- Renomée

- 1

Wer stapelt so viele Dies?die Flash-Stapel bei 48 Chips ohne Füllmaterial zwischen den Wafern 9,6 mm hoch.

--- Update ---

Zen auf einem Interposer?Es geht um falsche Einschätzungen und Zen wird durchaus auf einem Interposer erscheinen.

Gibt es dazu auch eine Quelle?

Bis jetzt gehen die Gerüchte für den EHP von einer GPU+HBM auf einem Interposer aus, das ganze auf dem Package.

Wird ein MCM auf das eine Zen-Die + der Interposer mit GPU+HBM kommt, aber Zen soll NICHT auf den Interposer kommen.

amdfanuwe

Grand Admiral Special

- Mitglied seit

- 24.06.2010

- Beiträge

- 2.372

- Renomée

- 34

- Details zu meinem Desktop

- Prozessor

- 4200+

- Mainboard

- M3A-H/HDMI

- Kühlung

- ein ziemlich dicker

- Speicher

- 2GB

- Grafikprozessor

- onboard

- Display

- Samsung 20"

- HDD

- WD 1,5TB

- Netzteil

- Extern 100W

- Betriebssystem

- XP, AndLinux

- Webbrowser

- Firefox

- Verschiedenes

- Kaum hörbar

Streng genommen ist der MCM Träger auch ein Interposer. Nur eben nicht aus Silizium. Silizium Interposer sind wohl nur nötig, wenn wirklich einige tausend Leitungen verbunden werden müssen oder gar noch einfache Logik mit integriert wird ( aktive Interposer ).

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 14.324

- Renomée

- 1.971

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 3950X

- Mainboard

- MSI MPG X570 GAMING PRO CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 4x 16 GB G.Skill Trident Z RGB, DDR4-3200, CL14

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Intel 600p 1TB

- HDD

- Western Digital WD Red 2 & 3TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

Der MCM Träger ist das Package Substrat vom obrigen Bild, der Interposer hat damit recht wenig zu tuen.

Streng genommen war das also quatsch.

--- Update ---

@Complicated

ah ja, ne Flüssigkeitskühlung wo ne Pumpe die Flüssigkeit zwischen den Bumps durch pressen soll und wo die Kühlflüssigkeit nicht leitend sein darf und auch die Signale nicht beeinflussen darf. Da der Platz nur gering ist würde es auch nur für low Power Prodkte reichen und dann noch in einem System für Endverbraucher? Bei was für einem Preis landen wir dann?

Ich wiederhole mich nur ungern..

Streng genommen war das also quatsch.

--- Update ---

@Complicated

ah ja, ne Flüssigkeitskühlung wo ne Pumpe die Flüssigkeit zwischen den Bumps durch pressen soll und wo die Kühlflüssigkeit nicht leitend sein darf und auch die Signale nicht beeinflussen darf. Da der Platz nur gering ist würde es auch nur für low Power Prodkte reichen und dann noch in einem System für Endverbraucher? Bei was für einem Preis landen wir dann?

Ich wiederhole mich nur ungern..

Was möglich ist ist nicht auch zwangsläufig sinnvoll oder rentabel.

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Komm schon:

Wo eine Wakü drauf passt, lässt sich bei weniger TDP wie z.B lediglich 95W stattdessen jedderzeit ein Luftkühler montieren.

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 14.324

- Renomée

- 1.971

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 3950X

- Mainboard

- MSI MPG X570 GAMING PRO CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 4x 16 GB G.Skill Trident Z RGB, DDR4-3200, CL14

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Intel 600p 1TB

- HDD

- Western Digital WD Red 2 & 3TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

Der Aufbau auf dem Bild aus deinem Beitrag #1629 setzt einen funktionierenden Kreislauf voraus der alle Chips umspült und genau das ist das Problem mit deiner Luftkühlung.

Die Verlußtleistung des gesammt Chips ist relativ egal da du die Wärme aller Teile abführen mußt. Genau das ist ja das Problem bei diesen Stapeln, weshalb die lediglich für Produkte mit sehr wenig Verlußtleistung sinnvoll sind. Die Chips in der Mitte dürften am heißesten werden da zusätzlich zu ihrer eigenen Abwärme auch noch die der umgebenen Chips abbekommen und um etwas kühlen zu können benötigst du eine gewisse Temperaturdifferenz.

Die Verlußtleistung des gesammt Chips ist relativ egal da du die Wärme aller Teile abführen mußt. Genau das ist ja das Problem bei diesen Stapeln, weshalb die lediglich für Produkte mit sehr wenig Verlußtleistung sinnvoll sind. Die Chips in der Mitte dürften am heißesten werden da zusätzlich zu ihrer eigenen Abwärme auch noch die der umgebenen Chips abbekommen und um etwas kühlen zu können benötigst du eine gewisse Temperaturdifferenz.

Opteron

Redaktion

☆☆☆☆☆☆

Zen mit L0-Cache und µOp-Puffer | Planet 3DNow!

http://www.planet3dnow.de/cms/22728-zen-mit-l0-cache-und-µop-puffer/

http://www.planet3dnow.de/cms/22728-zen-mit-l0-cache-und-µop-puffer/

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Das entspricht nicht den Tatsachen wie aus dem HBM Whitepaper zu entnehmen ist. Die Wärme Abfuhr der inneren Chips ist durch die TSVs enorm.Die Chips in der Mitte dürften am heißesten werden da zusätzlich zu ihrer eigenen Abwärme auch noch die der umgebenen Chips abbekommen und um etwas kühlen zu können benötigst du eine gewisse Temperaturdifferenz.

hot

Admiral Special

- Mitglied seit

- 21.09.2002

- Beiträge

- 1.187

- Renomée

- 15

- Details zu meinem Desktop

- Prozessor

- AMD Phenom 9500

- Mainboard

- Asrock AOD790GX/128

- Kühlung

- Scythe Mugen

- Speicher

- 2x Kingston DDR2 1066 CL7 1,9V

- Grafikprozessor

- Leadtek Geforce 260 Extreme+

- Display

- Samsung 2432BW

- HDD

- Samsung HD403LJ, Samung SP1614C

- Optisches Laufwerk

- LG HL55B

- Soundkarte

- Realtek ALC890

- Gehäuse

- Zirco AX

- Netzteil

- Coba Nitrox 600W Rev.2

- Betriebssystem

- Vista x64 HP

- Webbrowser

- Firefox

Die machen doch kein MCM mehr, wenn die Interposer haben, so ein Quatsch...

Grad im Serverbereich gibts richtiges Geld für gute Lösungen. Interposer werden ganz einfach Standard bei AMD werden mittelfristig.

Grad im Serverbereich gibts richtiges Geld für gute Lösungen. Interposer werden ganz einfach Standard bei AMD werden mittelfristig.

Zuletzt bearbeitet:

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 14.324

- Renomée

- 1.971

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 3950X

- Mainboard

- MSI MPG X570 GAMING PRO CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 4x 16 GB G.Skill Trident Z RGB, DDR4-3200, CL14

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Intel 600p 1TB

- HDD

- Western Digital WD Red 2 & 3TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

Das entspricht nicht den Tatsachen wie aus dem HBM Whitepaper zu entnehmen ist. Die Wärme Abfuhr der inneren Chips ist durch die TSVs enorm.

Der HBM Speicher dürfte aber auch keine sonderlich große Verlußtleistung haben, wodurch auch nicht großartig was abgeführt werden muss.

Siehe die Fiji Chips der Fury Karten, wenn ich mich recht erinnere hat da der Speicher keinen Kontakt zum Kühler.

--- Update ---

Die machen doch kein MCM mehr, wenn die Interposer haben, so ein Quatsch...

Grad im Serverbereich gibts richtiges Geld für gute Lösungen. Interposer werden ganz einfach Standard bei AMD werden mittelfristig.

Darauf würde ich nicht wetten denn schließlich ist AMD ein gewinnorientiertes Unternehmen.

Wenn ein MCM Design ausreicht und billiger in der Herstellung ist dann wird man auch darauf zurück greifen allerdings kann ich mir vor allem für komplexe Designs eine Mischform vorstellen bei denen beide Technologieen zum Einsatz kommen.

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Dort wird aber die TSV-Technik ausführlich erklärt und beschrieben. Diese Speicher sind darauf ausgelegt auf dem GPU-Die in richtigem 3D-Stacking verbaut zu werden, was eben diese Wärmebfuhr benötigt, um die unterliegenden CPUs/GPUs kühlen zu können. Der Temperaturuntertschied innerhalb des Chips liegt bei 2,5 °C bei 4 Layern, mindesten 10µm SI-Substrat Dicke, 9,3% Microbumpfläche auf dem Chip, Microbumpbreite 10µm, TSV-Breite 5 µm, 2% TSV-Fläche im Chip.

Diese Faktoren sind variabel und bei Verbesserung der thermischen Leistung kostet es halt mehr Chipfläche - hier gilt es den wirtschaftlichen Sweetspot zu treffen, was die eigentliche Herausforderung ist. Technisch sehe ich weniger Probleme.

Siehe Seite 28: http://www.sematech.org/meetings/archives/3d/8334/pres/Fukushima.pdf

Diese Faktoren sind variabel und bei Verbesserung der thermischen Leistung kostet es halt mehr Chipfläche - hier gilt es den wirtschaftlichen Sweetspot zu treffen, was die eigentliche Herausforderung ist. Technisch sehe ich weniger Probleme.

Siehe Seite 28: http://www.sematech.org/meetings/archives/3d/8334/pres/Fukushima.pdf

Und das gilt wohlgemerkt für echtes 3D-Stacking.

We evaluated thermal characteristics of 3D LSI by simulation and experiments. We confirmed,

1) The maximum temperature rise in chip can be suppressed by increasing the ratio of total TSV area and microbumparea to a chip area.

2) Too thin Si substrate results in the increase of the maximum temperature rise.

3) The maximum temperature of 3D chip can be lowered by reducing TSV pitch.

4) Heat transfer rate should be increased to decrease the maximum temperature of 3D chip.

hot

Admiral Special

- Mitglied seit

- 21.09.2002

- Beiträge

- 1.187

- Renomée

- 15

- Details zu meinem Desktop

- Prozessor

- AMD Phenom 9500

- Mainboard

- Asrock AOD790GX/128

- Kühlung

- Scythe Mugen

- Speicher

- 2x Kingston DDR2 1066 CL7 1,9V

- Grafikprozessor

- Leadtek Geforce 260 Extreme+

- Display

- Samsung 2432BW

- HDD

- Samsung HD403LJ, Samung SP1614C

- Optisches Laufwerk

- LG HL55B

- Soundkarte

- Realtek ALC890

- Gehäuse

- Zirco AX

- Netzteil

- Coba Nitrox 600W Rev.2

- Betriebssystem

- Vista x64 HP

- Webbrowser

- Firefox

Exakt. Gewinnorientierung und Kostenreduktion ist das Zauberwort. Du musst aber die mittel/langfristigen Kostenstrukturen sehen, nicht das jetzt Interposer noch teuer sind. Da sind gerade aktive Interposer sehr sehr spannend.

Zuletzt bearbeitet:

Stefan Payne

Grand Admiral Special

MCM kann man mit dem Package machen oder mit Interposern, das ändert nichts an dem Zustand, dass beides MCM sind, wie das letztendlich realisiert wird, ist absolut irrelevant.Die machen doch kein MCM mehr, wenn die Interposer haben, so ein Quatsch...

Grad im Serverbereich gibts richtiges Geld für gute Lösungen. Interposer werden ganz einfach Standard bei AMD werden mittelfristig.

Es heißt nur, dass mehrere Chips auf einem Package drauf sind, nicht mehr, nicht weniger.

Sogesehen ist auch AMDs Fiji ein MCM Chip...

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Es ist ein SiP, hatte wir doch schon

http://www.planet3dnow.de/vbulletin...-AM4-Version?p=5070468&viewfull=1#post5070468

http://www.planet3dnow.de/vbulletin...-AM4-Version?p=5070468&viewfull=1#post5070468

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 14.324

- Renomée

- 1.971

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 3950X

- Mainboard

- MSI MPG X570 GAMING PRO CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 4x 16 GB G.Skill Trident Z RGB, DDR4-3200, CL14

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Intel 600p 1TB

- HDD

- Western Digital WD Red 2 & 3TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

[3DC]Payne;5074334 schrieb:MCM kann man mit dem Package machen oder mit Interposern, das ändert nichts an dem Zustand, dass beides MCM sind, wie das letztendlich realisiert wird, ist absolut irrelevant.

Es heißt nur, dass mehrere Chips auf einem Package drauf sind, nicht mehr, nicht weniger.

Sogesehen ist auch AMDs Fiji ein MCM Chip...

Ich glaube du verwechselst da was.

Package = Chip Gehäuse bzw. dessen Träger Substrat

Der Interposer hat mit dem Package nichts am Hut, kommt aber ins Package rein.

OBrian

Moderation MBDB, ,

- Mitglied seit

- 16.10.2000

- Beiträge

- 17.033

- Renomée

- 267

- Standort

- NRW

- Details zu meinem Desktop

- Prozessor

- Phenom II X4 940 BE, C2-Stepping (undervolted)

- Mainboard

- Gigabyte GA-MA69G-S3H (BIOS F7)

- Kühlung

- Noctua NH-U12F

- Speicher

- 4 GB DDR2-800 ADATA/OCZ

- Grafikprozessor

- Radeon HD 5850

- Display

- NEC MultiSync 24WMGX³

- SSD

- Samsung 840 Evo 256 GB

- HDD

- WD Caviar Green 2 TB (WD20EARX)

- Optisches Laufwerk

- Samsung SH-S183L

- Soundkarte

- Creative X-Fi EM mit YouP-PAX-Treibern, Headset: Sennheiser PC350

- Gehäuse

- Coolermaster Stacker, 120mm-Lüfter ersetzt durch Scythe S-Flex, zusätzliche Staubfilter

- Netzteil

- BeQuiet 500W PCGH-Edition

- Betriebssystem

- Windows 7 x64

- Webbrowser

- Firefox

- Verschiedenes

- Tastatur: Zowie Celeritas Caseking-Mod (weiße Tasten)

ja, MCM versteht man im Allgemeinen eher als mehrere Dies in einem Package (G34-CPUs o.ä.), obwohl man natürlich strenggenommen "multi chip module" auch zu sowas wie Fiji sagen könnte, wo nur ein Die im Package ist und mehrere kleine Dies auf dem großen. Nur wird das mißverständlich, wenn jeder seine eigene Definition verwendet. Wenn Ihr Euch uneins seid, dann vermeidet den Begriff MCM doch einfach komplett. Sobald es Produkte gibt, wo in einem Package zwei oder mehr Interposer-Dies drin sind, die wiederum jeweils mehrere kleine Dies tragen, wird es spannend, was Ihr dann sagen wollt. Es kann gut sein, daß diese Riesen-CPU mit 32 Kernen genau sowas ist...

ja, man könnte z.B. überlegen, die Strukturen, die sich sowieso schlecht shrinken lassen und die somit nur viel wertvolle Diefläche bei den teuren High-End-Prozessen verballern, so weit wie möglich/sinnvoll auf den Interposer auszulagern. Memory Controller evtl., dann muß man sich natürlich überlegen, wie man einen guten Interconnect baut, aber grundsätzlich ginge das sicherlich ganz gut. Und diverser Chipsatz-Krempel.Exakt. Gewinnorientierung und Kostenreduktion ist das Zauberwort. Du musst aber die mittel/langfristigen Kostenstrukturen sehen, nicht das jetzt Interposer noch teuer sind. Da sind gerade aktive Interposer sehr sehr spannend.

Crashtest

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 11.11.2008

- Beiträge

- 9.275

- Renomée

- 1.413

- Standort

- Leipzig

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- Collatz, yoyo, radac

- Lieblingsprojekt

- yoyo

- Meine Systeme

- Ryzen: 2x1600, 5x1700, 1x2700,1x3600, 1x5600X; EPYC 7V12 und Kleinzeuch

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Lenovo IdeaPad 5 14ALC05

- Details zu meinem Desktop

- Prozessor

- Ryzen 7950X / Ryzen 4750G

- Mainboard

- ASRock B650M PGRT / X570D4U

- Kühlung

- be quiet! Dark Rock Pro4 / Pure Rock Slim 2

- Speicher

- 64GB DDR5-5600 G Skill F5-5600J3036D16G / 32 GB DDR4-3200 ECC

- Grafikprozessor

- Raphael IGP / ASpeed AST-2500

- Display

- 27" Samsung LF27T450F

- SSD

- KINGSTON SNVS2000G

- HDD

- - / 8x Seagate IronWolf Pro 20TB

- Optisches Laufwerk

- 1x B.Ray - LG BD-RE BH16NS55

- Soundkarte

- onboard HD?

- Gehäuse

- zu kleines für die GPU

- Netzteil

- be quiet! Pure Power 11 400W / dito

- Tastatur

- CHERRY SECURE BOARD 1.0

- Maus

- Logitech RX250

- Betriebssystem

- Windows 10 19045.3996 / Server 20348.2227

- Webbrowser

- Edge 120.0.2210.121

- Verschiedenes

- U320 SCSI-Controller !!!!

- Internetanbindung

- ▼1000 MBit ▲82 MBit

Sofern der Buschfunk stimmt sind die großen neuen Server-CPU:

2x native 16Core/32Thread DIE auf einem Träger die über in den Träger integrierte Datenleitungen verbunden sind - ist so ziemlich Sockel G34 wo auch 2 DIE drauf waren (2x Hydra für 61xx Optis bzw. 2x Orochi für 62xx und 63xx) --> MCM !?

Die "kleinen" Server-CPUs sind dann nur 1x native 16Core/32Thread DIE.

Aber es kommen nach bisherigen Stand wenigstens 4 verschiedene ZEN-DIE:

native bis 8C/16T --> Billig-Desktop

native bis 16C/32T --> Billig-Server/Midrange WS/Desktop

2x 16C/32T --> HPC/Datacenter

native 4C/8T mit GPU --> Billig-APU

und die XB1 bekommt auch Shrink

2x native 16Core/32Thread DIE auf einem Träger die über in den Träger integrierte Datenleitungen verbunden sind - ist so ziemlich Sockel G34 wo auch 2 DIE drauf waren (2x Hydra für 61xx Optis bzw. 2x Orochi für 62xx und 63xx) --> MCM !?

Die "kleinen" Server-CPUs sind dann nur 1x native 16Core/32Thread DIE.

Aber es kommen nach bisherigen Stand wenigstens 4 verschiedene ZEN-DIE:

native bis 8C/16T --> Billig-Desktop

native bis 16C/32T --> Billig-Server/Midrange WS/Desktop

2x 16C/32T --> HPC/Datacenter

native 4C/8T mit GPU --> Billig-APU

und die XB1 bekommt auch Shrink

Zuletzt bearbeitet:

Ähnliche Themen

- Antworten

- 91

- Aufrufe

- 8K

- Antworten

- 14

- Aufrufe

- 930

- Antworten

- 102

- Aufrufe

- 11K

- Antworten

- 3

- Aufrufe

- 2K