App installieren

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: This feature may not be available in some browsers.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

AMD Zen - 14nm, 8 Kerne, 95W TDP & DDR4?

- Ersteller UNRUHEHERD

- Erstellt am

Das hat ja schon langsam Tradition:

TbredA -> TbredB

PhI -> PhII

Zambesi -> Vishera

Sicher, CPU Entwicklung ist alles andere als trivial.

Allerdings muss auch der Erste Schuss beim Kunden sitzen, da gibt es nicht allzu viele zweite Chancen.

AMD hatte schon so oft den Vorschuss Bonus, langsam muss wirklich mal was kommen.

Nun ja, Intel schaltet fehlerhafte Features nachträglich einfach mal ab. (TSX)

Atombossler

Admiral Special

- Mitglied seit

- 28.04.2013

- Beiträge

- 1.425

- Renomée

- 65

- Standort

- Andere Sphären

- Mein Laptop

- Thinkpad 8

- Details zu meinem Desktop

- Prozessor

- A8-7600@3.25Ghz

- Mainboard

- Asus A88X-PRO

- Kühlung

- NoFan CR80 EH

- Speicher

- 16Gb G-Skill Trident-X DDR3 2400

- Grafikprozessor

- APU

- Display

- Acer UHD 4K2K

- SSD

- Samsung 850 PRO

- HDD

- 2xSamsung 1TB HDD (2,5")

- Optisches Laufwerk

- Plexi BD-RW

- Soundkarte

- OnBoard Geraffel

- Gehäuse

- Define R2

- Netzteil

- BeQuiet

- Betriebssystem

- Win7x64-PRO

- Webbrowser

- Chrome

Ich hab ja auch gar nicht behauptet, dass es bei Anderen nicht auch zu nennenswerten Bugs kommt.

Allein es ist recht selten, weniger Performancerelevant, bzw. es werden Konsequenzen gezogen (ok. bei nVidia weniger ... ).

Das vermisse ich irgendwie bei AMD.

Nach dem X-ten verbockten Release sollte man doch da mal was dran ändern, oder nicht?

Auch der Polaris Release war alles andere als gut.

Im Gedächtnis bleibt nur der Spec. Bruch ...

Erst die Radeon-Pro WX Serie macht jetzt eine doch recht gute Figur, damit hätten Sie im Desktop viel besser Punkten können.

Von dem viel beworbenen HEVC Hardware Encoding ist weit und breit nichts zu sehen ...

Wenn das mal kein Bumerang gibt.

Von wegen zugesicherte Leistungen und so ...

Allein es ist recht selten, weniger Performancerelevant, bzw. es werden Konsequenzen gezogen (ok. bei nVidia weniger ... ).

Das vermisse ich irgendwie bei AMD.

Nach dem X-ten verbockten Release sollte man doch da mal was dran ändern, oder nicht?

Auch der Polaris Release war alles andere als gut.

Im Gedächtnis bleibt nur der Spec. Bruch ...

Erst die Radeon-Pro WX Serie macht jetzt eine doch recht gute Figur, damit hätten Sie im Desktop viel besser Punkten können.

Von dem viel beworbenen HEVC Hardware Encoding ist weit und breit nichts zu sehen ...

Wenn das mal kein Bumerang gibt.

Von wegen zugesicherte Leistungen und so ...

derDruide

Grand Admiral Special

- Mitglied seit

- 09.08.2004

- Beiträge

- 2.714

- Renomée

- 430

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 3900X

- Mainboard

- Asus Strix B450-F Gaming

- Kühlung

- Noctua NH-C14

- Speicher

- 32 GB DDR4-3200 CL14 FlareX

- Grafikprozessor

- Radeon RX 590

- Display

- 31.5" Eizo FlexScan EV3285

- SSD

- Corsair MP510 2 TB, Samsung 970 Evo 512 GB

- HDD

- Seagate Ironwulf 6 TB

- Optisches Laufwerk

- Plextor PX-880SA

- Soundkarte

- Creative SoundblasterX AE-7

- Gehäuse

- Antec P280

- Netzteil

- be quiet! Straight Power E9 400W

- Maus

- Logitech Trackman Marble (Trackball)

- Betriebssystem

- openSUSE 15.2

- Webbrowser

- Firefox

- Internetanbindung

- ▼50 MBit ▲10 MBit

Auch der Polaris Release war alles andere als gut.

Im Gedächtnis bleibt nur der Spec. Bruch ...

Och büdde, ganz bestimmt nicht.

tomturbo

Technische Administration, Dinosaurier

- Mitglied seit

- 30.11.2005

- Beiträge

- 9.455

- Renomée

- 665

- Standort

- Österreich

- Aktuelle Projekte

- Universe@HOME, Asteroids@HOME

- Lieblingsprojekt

- SETI@HOME

- Meine Systeme

- Xeon E3-1245V6; Raspberry Pi 4; Ryzen 1700X; EPIC 7351

- BOINC-Statistiken

- Mein Laptop

- Microsoft Surface Pro 4

- Details zu meinem Desktop

- Prozessor

- R7 5800X

- Mainboard

- Asus ROG STRIX B550-A GAMING

- Kühlung

- Alpenfön Ben Nevis Rev B

- Speicher

- 2x32GB Mushkin, D464GB 3200-22 Essentials

- Grafikprozessor

- Sapphire Radeon RX 460 2GB

- Display

- BenQ PD3220U, 31.5" 4K

- SSD

- 1x HP SSD EX950 1TB, 1x SAMSUNG SSD 830 Series 256 GB, 1x Crucial_CT256MX100SSD1

- HDD

- Toshiba X300 5TB

- Optisches Laufwerk

- Samsung Brenner

- Soundkarte

- onboard

- Gehäuse

- Fractal Design Define R4

- Netzteil

- XFX 550W

- Tastatur

- Trust ASTA mechanical

- Maus

- irgend eine silent Maus

- Betriebssystem

- Arch Linux, Windows VM

- Webbrowser

- Firefox + Chromium + Konqueror

- Internetanbindung

-

▼300

▲50

Warum soll Polaris kein Hevc decodieren können?

Bei meinem HTPC mit 460er klappt es jedenfalls.

Bei meinem HTPC mit 460er klappt es jedenfalls.

BoMbY

Grand Admiral Special

- Mitglied seit

- 22.11.2001

- Beiträge

- 7.468

- Renomée

- 293

- Standort

- Aachen

- Details zu meinem Desktop

- Prozessor

- Ryzen 3700X

- Mainboard

- Gigabyte X570 Aorus Elite

- Kühlung

- Noctua NH-U12A

- Speicher

- 2x16 GB, G.Skill F4-3200C14D-32GVK @ 3600 16-16-16-32-48-1T

- Grafikprozessor

- RX 5700 XTX

- Display

- Samsung CHG70, 32", 2560x1440@144Hz, FreeSync2

- SSD

- AORUS NVMe Gen4 SSD 2TB, Samsung 960 EVO 1TB, Samsung 840 EVO 1TB, Samsung 850 EVO 512GB

- Optisches Laufwerk

- Sony BD-5300S-0B (eSATA)

- Gehäuse

- Phanteks Evolv ATX

- Netzteil

- Enermax Platimax D.F. 750W

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox

Encoding <> Decoding. Der H.265 Encoding Teil fehlt immer noch in den SDKs (jedenfalls in den öffentlich zugänglichen).

Alyva

Vice Admiral Special

- Mitglied seit

- 12.01.2008

- Beiträge

- 712

- Renomée

- 6

- Details zu meinem Desktop

- Prozessor

- AMD Athlon 64 3500+ Newcastle

- Mainboard

- K8N SLI Platinum

- Kühlung

- Boxed Variante

- Speicher

- MDT 2* 1 GB PC400 CL2

- Grafikprozessor

- Geforce 6800 GT Ultra

- Display

- 17" AOC 1280*1024

- HDD

- WD 360 GD / ST3200822A

- Optisches Laufwerk

- Toshiba DVD-Rom SD-M1912

- Soundkarte

- Soundblaster Audigy

- Netzteil

- 380 Watt

- Betriebssystem

- Windows XP

- Webbrowser

- Maxthon

Laut diesem Herrn hier mangelt es wohl eher an der Software:

https://www.reddit.com/r/Amd/comments/4yjaya/here_are_some_sample_hevc_encodes_using_polaris/

https://www.reddit.com/r/Amd/comments/4yjaya/here_are_some_sample_hevc_encodes_using_polaris/

tomturbo

Technische Administration, Dinosaurier

- Mitglied seit

- 30.11.2005

- Beiträge

- 9.455

- Renomée

- 665

- Standort

- Österreich

- Aktuelle Projekte

- Universe@HOME, Asteroids@HOME

- Lieblingsprojekt

- SETI@HOME

- Meine Systeme

- Xeon E3-1245V6; Raspberry Pi 4; Ryzen 1700X; EPIC 7351

- BOINC-Statistiken

- Mein Laptop

- Microsoft Surface Pro 4

- Details zu meinem Desktop

- Prozessor

- R7 5800X

- Mainboard

- Asus ROG STRIX B550-A GAMING

- Kühlung

- Alpenfön Ben Nevis Rev B

- Speicher

- 2x32GB Mushkin, D464GB 3200-22 Essentials

- Grafikprozessor

- Sapphire Radeon RX 460 2GB

- Display

- BenQ PD3220U, 31.5" 4K

- SSD

- 1x HP SSD EX950 1TB, 1x SAMSUNG SSD 830 Series 256 GB, 1x Crucial_CT256MX100SSD1

- HDD

- Toshiba X300 5TB

- Optisches Laufwerk

- Samsung Brenner

- Soundkarte

- onboard

- Gehäuse

- Fractal Design Define R4

- Netzteil

- XFX 550W

- Tastatur

- Trust ASTA mechanical

- Maus

- irgend eine silent Maus

- Betriebssystem

- Arch Linux, Windows VM

- Webbrowser

- Firefox + Chromium + Konqueror

- Internetanbindung

-

▼300

▲50

Encoding <> Decoding. Der H.265 Encoding Teil fehlt immer noch in den SDKs (jedenfalls in den öffentlich zugänglichen).

Huch, das hatte ich glatt überlesen.

Gut HW-Encoding hat mich aufgrund der miesen Quali eh nie interessiert.

Von daher war ich auf decoding, was ja auch erst seit kurzem ordentlich funktioniert, fokusiert.

Sorry

Atombossler

Admiral Special

- Mitglied seit

- 28.04.2013

- Beiträge

- 1.425

- Renomée

- 65

- Standort

- Andere Sphären

- Mein Laptop

- Thinkpad 8

- Details zu meinem Desktop

- Prozessor

- A8-7600@3.25Ghz

- Mainboard

- Asus A88X-PRO

- Kühlung

- NoFan CR80 EH

- Speicher

- 16Gb G-Skill Trident-X DDR3 2400

- Grafikprozessor

- APU

- Display

- Acer UHD 4K2K

- SSD

- Samsung 850 PRO

- HDD

- 2xSamsung 1TB HDD (2,5")

- Optisches Laufwerk

- Plexi BD-RW

- Soundkarte

- OnBoard Geraffel

- Gehäuse

- Define R2

- Netzteil

- BeQuiet

- Betriebssystem

- Win7x64-PRO

- Webbrowser

- Chrome

Laut diesem Herrn hier mangelt es wohl eher an der Software:

https://www.reddit.com/r/Amd/comments/4yjaya/here_are_some_sample_hevc_encodes_using_polaris/

Natürlich tut es das.

Polaris hat die Funktionalität durchaus.

Nur womit nutzen/ansteuern?

Das ist es doch genau.

Da muss sich AMD über Kritik nicht wundern.

Stefan Payne

Grand Admiral Special

Wait, what?!AMD hatte schon so oft den Vorschuss Bonus, langsam muss wirklich mal was kommen.

Von wem?!

Der 'normale' User kauft doch eh Intel oder ihm wird zu Intel geraten, auch wenn totaler Unsinn...

Das wäre bitter, wenn es einen Fehler im Silizium gibt der mit Workaround zwar gefixt werden kann aber 30-40% Leistung kostet.

Alles andere lässt mich aber hoffen! Leistungstechnisch auf Augenhöhe mit Intel - gut Bandbreitenintensiv Tests noch nicht - was aber am Limit liegen dürfte...

Nur auch hier kommt der Preis von 300$ für den 8Kerner/16Threads.. Das wäre eine Bombe in meinen Augen... Damit würden sie devinitiv Marktanteile holen... Nur das Sie so ticken glaube ich nicht. Bzw. fürs Spitzenmodell das mit Haswell-E mithalten kann - wenn man dem Leak glauben mag - können Sie ruhig 600$ aufrufen und wären noch immer im Vergleich zu Intel sehr interessant...

Alles andere lässt mich aber hoffen! Leistungstechnisch auf Augenhöhe mit Intel - gut Bandbreitenintensiv Tests noch nicht - was aber am Limit liegen dürfte...

Nur auch hier kommt der Preis von 300$ für den 8Kerner/16Threads.. Das wäre eine Bombe in meinen Augen... Damit würden sie devinitiv Marktanteile holen... Nur das Sie so ticken glaube ich nicht. Bzw. fürs Spitzenmodell das mit Haswell-E mithalten kann - wenn man dem Leak glauben mag - können Sie ruhig 600$ aufrufen und wären noch immer im Vergleich zu Intel sehr interessant...

cyrusNGC_224

Grand Admiral Special

- Mitglied seit

- 01.05.2014

- Beiträge

- 5.924

- Renomée

- 117

- Aktuelle Projekte

- POGS, Asteroids, Milkyway, SETI, Einstein, Enigma, Constellation, Cosmology

- Lieblingsprojekt

- POGS, Asteroids, Milkyway

- Meine Systeme

- X6 PII 1090T, A10-7850K, 6x Athlon 5350, i7-3632QM, C2D 6400, AMD X4 PII 810, 6x Odroid U3

- BOINC-Statistiken

Ja, das sollten sie sein lassen. Dann lieber etwas länger warten (das zieht sich doch eh wieder) als so einen Quatsch releasen.Das wäre bitter, wenn es einen Fehler im Silizium gibt der mit Workaround zwar gefixt werden kann aber 30-40% Leistung kostet.

Ich denke mal, ZEN wird man erst Anfang des 2. Quartals richtig bekommen.

WindHund

Grand Admiral Special

- Mitglied seit

- 30.01.2008

- Beiträge

- 12.219

- Renomée

- 535

- Standort

- Im wilden Süden (0711)

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- NumberFields@home

- Lieblingsprojekt

- none, try all

- Meine Systeme

- RYZEN R9 3900XT @ ASRock Taichi X570 & ASUS RX Vega64

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5950X

- Mainboard

- ASRock 570X Taichi P5.05 Certified

- Kühlung

- AlphaCool Eisblock XPX, 366x40mm Radiator 6l Brutto m³

- Speicher

- 2x 16 GiB DDR4-3600 CL26 Kingston (Dual Rank, unbuffered ECC)

- Grafikprozessor

- 1x ASRock Radeon RX 6950XT Formula OC 16GByte GDDR6 VRAM

- Display

- SAMSUNG Neo QLED QN92BA 43" up to 4K@144Hz FreeSync PP HDR10+

- SSD

- WD_Black SN850 PCI-Express 4.0 NVME

- HDD

- 3 Stück

- Optisches Laufwerk

- 1x HL-DT-ST BD-RE BH10LS30 SATA2

- Soundkarte

- HD Audio (onboard)

- Gehäuse

- SF-2000 Big Tower

- Netzteil

- Corsair RM1000X (80+ Gold)

- Tastatur

- Habe ich

- Maus

- Han I

- Betriebssystem

- Windows 10 x64 Professional (up to date!)

- Webbrowser

- @Chrome.Google & Edge Chrome

Es wuerde mich eher wundern, wenn die Tradition nicht fortgesetzt wird!Das ist durchaus klar.

Damit ist der Bug aber noch immer da.

Wie gut was sein könnte, wenns denn richtig gemacht wäre, davon kann ja gerade AMD ein Lied singen.

Solln ses halt mal machen - for god sake.

Das hat ja schon langsam Tradition:

TbredA -> TbredB

PhI -> PhII

Zambesi -> Vishera

Sicher, CPU Entwicklung ist alles andere als trivial.

Allerdings muss auch der Erste Schuss beim Kunden sitzen, da gibt es nicht allzu viele zweite Chancen.

AMD hatte schon so oft den Vorschuss Bonus, langsam muss wirklich mal was kommen.

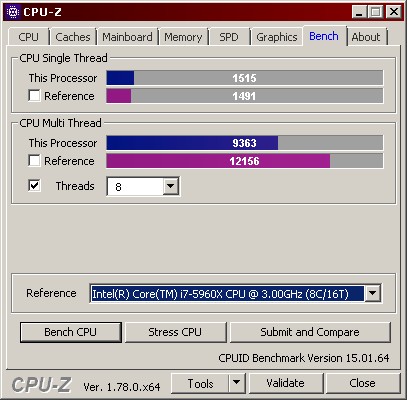

Der Fix kann alles moegliche sein, ich vermute eher sie nutzen nur ein BIOS welches sehr klein ist vom Speicherplatz her.The important thing here is that the 16Thread/8-Core CPU is minimum 5960X performance if not better actually. (Based on Cinebench R15) with the error fix disabled.

Das waere dann mit einem UEFI weniger problematisch, nur braucht das UEFI den gesamten CPUID String und nicht nur ein Test Sample String.

Beim Naples will man scheinbar fehler an der SMT implementierung gefunden haben, womoeglich noch mit Intel Code und keinen eigenstaendigen von AMD.

![Augen rollen (sarkastisch) :] :]](https://www.planet3dnow.de/vbulletin/images/smilies/rolleyes.gif)

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 14.324

- Renomée

- 1.971

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 3950X

- Mainboard

- MSI MPG X570 GAMING PRO CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 4x 16 GB G.Skill Trident Z RGB, DDR4-3200, CL14

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Intel 600p 1TB

- HDD

- Western Digital WD Red 2 & 3TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

Je nachdem wie lange das Problem bekannt ist kann die Entwicklung einer gefixten Revision bereits abgeschlossen sein und es womöglich auch schon gefixte Samples geben.

Solche oberflächlichen Einblicke mögen ja ganz nett sein aber geben keinen definitiven Stand zur Entwicklung an. Beispielsweise brauchs du zur Qualifizierung der Plattform wohl kaum einen Chip vom letzten Entwicklungsstand. Da dürfte auch ein frühes, lauffähiges Sample reichen das die Spezifikationen für die Plattform einhält.

Ich würde also nicht zu viel auf sowas geben sondern auf das fertige Produkt warten.

Solche oberflächlichen Einblicke mögen ja ganz nett sein aber geben keinen definitiven Stand zur Entwicklung an. Beispielsweise brauchs du zur Qualifizierung der Plattform wohl kaum einen Chip vom letzten Entwicklungsstand. Da dürfte auch ein frühes, lauffähiges Sample reichen das die Spezifikationen für die Plattform einhält.

Ich würde also nicht zu viel auf sowas geben sondern auf das fertige Produkt warten.

Dune

Commander

- Mitglied seit

- 11.11.2001

- Beiträge

- 163

- Renomée

- 0

- Standort

- Hamburg

- Details zu meinem Desktop

- Prozessor

- AMD Phenom II X4 965

- Mainboard

- MSI DKA 790 GX Platinum

- Kühlung

- Water /Trippelradiator

- Speicher

- 4 Gig DDR 2

- Grafikprozessor

- ATI HD 3600

- Display

- Quato 27°

- SSD

- Startplatte/Systemplatte

- Betriebssystem

- WIn 7 Home Professionel

- Webbrowser

- Firefox

- Verschiedenes

- Zweitsystem: FM 2 Asus F2A85-M; A10-6800K; 8 Gig DDR 3; WIN 7 Home Premium

Ich sehe die situation ein wenig gelassener. Sollte es wirklich einen Bug geben bezüglich des HT, so kann amd es in der ersten Charge ja abschalten. Sie hätten dann gegenüber Intel immer noch den Vorteil von 8 echten Kernen gegenüber Intel mit 4 Physischen und weiteren 4 logischen kernen. Das silizium ist ja nicht übermäsig groß und ich würde da schon 350 EUR dafür zahlen wenn sie mit der Leistung gegenüber Intel auf Augenhöhen sind. Ich denke, da würden auch viele zugreifen und mit dem erwirtschafteten Geld, kann mann immer nochmal eine neue Rev. finanzieren welche dann mit mehr leistung und 8 Physischen + 8 Logischen als Upgrade teurer angeboten werden kann. Dann käme die absolute Sperspitze eben 2-3 Monate spähter.

LG

Dune

LG

Dune

WindHund

Grand Admiral Special

- Mitglied seit

- 30.01.2008

- Beiträge

- 12.219

- Renomée

- 535

- Standort

- Im wilden Süden (0711)

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- NumberFields@home

- Lieblingsprojekt

- none, try all

- Meine Systeme

- RYZEN R9 3900XT @ ASRock Taichi X570 & ASUS RX Vega64

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5950X

- Mainboard

- ASRock 570X Taichi P5.05 Certified

- Kühlung

- AlphaCool Eisblock XPX, 366x40mm Radiator 6l Brutto m³

- Speicher

- 2x 16 GiB DDR4-3600 CL26 Kingston (Dual Rank, unbuffered ECC)

- Grafikprozessor

- 1x ASRock Radeon RX 6950XT Formula OC 16GByte GDDR6 VRAM

- Display

- SAMSUNG Neo QLED QN92BA 43" up to 4K@144Hz FreeSync PP HDR10+

- SSD

- WD_Black SN850 PCI-Express 4.0 NVME

- HDD

- 3 Stück

- Optisches Laufwerk

- 1x HL-DT-ST BD-RE BH10LS30 SATA2

- Soundkarte

- HD Audio (onboard)

- Gehäuse

- SF-2000 Big Tower

- Netzteil

- Corsair RM1000X (80+ Gold)

- Tastatur

- Habe ich

- Maus

- Han I

- Betriebssystem

- Windows 10 x64 Professional (up to date!)

- Webbrowser

- @Chrome.Google & Edge Chrome

Das meinte ich auch, es sind Samples die halbgar sind, die dürfen Fehler haben.Je nachdem wie lange das Problem bekannt ist kann die Entwicklung einer gefixten Revision bereits abgeschlossen sein und es womöglich auch schon gefixte Samples geben.

Solche oberflächlichen Einblicke mögen ja ganz nett sein aber geben keinen definitiven Stand zur Entwicklung an. Beispielsweise brauchs du zur Qualifizierung der Plattform wohl kaum einen Chip vom letzten Entwicklungsstand. Da dürfte auch ein frühes, lauffähiges Sample reichen das die Spezifikationen für die Plattform einhält.

Ich würde also nicht zu viel auf sowas geben sondern auf das fertige Produkt warten.

Welche Plattform meinst du? Die AM4 oem Mainboards?

Der cpuid String ist nur wichtig für die richtige zuweisung des fix.

ohne verliert man Leistung.

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 14.324

- Renomée

- 1.971

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 3950X

- Mainboard

- MSI MPG X570 GAMING PRO CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 4x 16 GB G.Skill Trident Z RGB, DDR4-3200, CL14

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Intel 600p 1TB

- HDD

- Western Digital WD Red 2 & 3TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

Das war bewußt allgemein geschrieben weil es nichts spezielles für die AM4 Plattform ist sondern letztendlich auf jedes neue mainboard zutrifft.

Die Entwicklung der Mainboards läuft schließlich parallel ab und die dafür nötigen Spezifikationen sind auch entsprechend zeitig verfügbar udn an diese müssen sich letztendlich CPU und Mainboard halten.

Wenn man mal genauer darüber nachdenkt wäre es auch ziemlich unsinnig auf den fertig entwickelten und bereinigten Prozessor zu warten denn dann würde der erstmal ohne Mainboard da stehen. Wer kauf einen Prozessor ohne ein Mainboard zu bekommen in dem er ihn betreiben kann?

Dann lieber die erforderlichen Spezifikationen im Vorfeld festlegen und das Bugfixing parallel laufen lassen.

Der TLB Bug des ersten Phenoms war ja letztendlich auch nur so ein Debakel weil er bereits auf dem Markt war. Wäre er vorher aufgefallen dann hätte man den Prozessor wohl eher verschoben, gleich mit der bereinigten Version gestartet und der Endkunde hätte davon abgesehen vom späteren Release nichts mitbekommen.

Die Entwicklung der Mainboards läuft schließlich parallel ab und die dafür nötigen Spezifikationen sind auch entsprechend zeitig verfügbar udn an diese müssen sich letztendlich CPU und Mainboard halten.

Wenn man mal genauer darüber nachdenkt wäre es auch ziemlich unsinnig auf den fertig entwickelten und bereinigten Prozessor zu warten denn dann würde der erstmal ohne Mainboard da stehen. Wer kauf einen Prozessor ohne ein Mainboard zu bekommen in dem er ihn betreiben kann?

Dann lieber die erforderlichen Spezifikationen im Vorfeld festlegen und das Bugfixing parallel laufen lassen.

Der TLB Bug des ersten Phenoms war ja letztendlich auch nur so ein Debakel weil er bereits auf dem Markt war. Wäre er vorher aufgefallen dann hätte man den Prozessor wohl eher verschoben, gleich mit der bereinigten Version gestartet und der Endkunde hätte davon abgesehen vom späteren Release nichts mitbekommen.

Zuletzt bearbeitet:

derDruide

Grand Admiral Special

- Mitglied seit

- 09.08.2004

- Beiträge

- 2.714

- Renomée

- 430

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 3900X

- Mainboard

- Asus Strix B450-F Gaming

- Kühlung

- Noctua NH-C14

- Speicher

- 32 GB DDR4-3200 CL14 FlareX

- Grafikprozessor

- Radeon RX 590

- Display

- 31.5" Eizo FlexScan EV3285

- SSD

- Corsair MP510 2 TB, Samsung 970 Evo 512 GB

- HDD

- Seagate Ironwulf 6 TB

- Optisches Laufwerk

- Plextor PX-880SA

- Soundkarte

- Creative SoundblasterX AE-7

- Gehäuse

- Antec P280

- Netzteil

- be quiet! Straight Power E9 400W

- Maus

- Logitech Trackman Marble (Trackball)

- Betriebssystem

- openSUSE 15.2

- Webbrowser

- Firefox

- Internetanbindung

- ▼50 MBit ▲10 MBit

Der TLB Bug des ersten Phenoms war ja letztendlich auch nur so ein Debakel weil er bereits auf dem Markt war. Wäre er vorher aufgefallen dann hätte man den Prozessor wohl eher verschoben, gleich mit der bereinigten Version gestartet und der Endkunde hätte davon abgesehen vom späteren Release nichts mitbekommen.

Ein guter Punkt, meistens wurden die beiden Fälle hier einfach in einen Topf geworfen.

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 14.324

- Renomée

- 1.971

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 3950X

- Mainboard

- MSI MPG X570 GAMING PRO CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 4x 16 GB G.Skill Trident Z RGB, DDR4-3200, CL14

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Intel 600p 1TB

- HDD

- Western Digital WD Red 2 & 3TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

Mal abgesehen davon halte ich den damaligen Affentanz um den Bug für den Desktop Bereich ohnehin für überzogen denn ich hatte selbst einen davon, bewußt darauf geachtet das der Fix nicht aktiv wird und die Kiste lief dennoch anstandslos. Abstürze die in der Zeit auftraten waren eher auf Probleme mit der jeweiligen Software oder diverser Treiber zurück zu führen, traten auch bei andern Prozessoren auf und verschwanden mit den Software und Treiber Updates.

BoMbY

Grand Admiral Special

- Mitglied seit

- 22.11.2001

- Beiträge

- 7.468

- Renomée

- 293

- Standort

- Aachen

- Details zu meinem Desktop

- Prozessor

- Ryzen 3700X

- Mainboard

- Gigabyte X570 Aorus Elite

- Kühlung

- Noctua NH-U12A

- Speicher

- 2x16 GB, G.Skill F4-3200C14D-32GVK @ 3600 16-16-16-32-48-1T

- Grafikprozessor

- RX 5700 XTX

- Display

- Samsung CHG70, 32", 2560x1440@144Hz, FreeSync2

- SSD

- AORUS NVMe Gen4 SSD 2TB, Samsung 960 EVO 1TB, Samsung 840 EVO 1TB, Samsung 850 EVO 512GB

- Optisches Laufwerk

- Sony BD-5300S-0B (eSATA)

- Gehäuse

- Phanteks Evolv ATX

- Netzteil

- Enermax Platimax D.F. 750W

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox

Nicht wirklich spannend auf den ersten Blick:

Dürfte eher für die Server-Zens mit mehreren Modulen interessant sein? Das heißt die Memory Controller pro Summit Ridge Modul mit ihren jeweils zwei Kanälen arbeiten prinzipiell erstmal vollkommen unabhängig voneinander?

Edit: Das könnte auch einige der Erkennungs- und Performanceprobleme erklären. Ich schätze das ist so in der Software bisher nicht wirklich vorgesehen, dass hier quasi bis zu vier getrennte CPUs auf einem Sockel sitzen. Im Prinzip muss das OS die bei Dual-Sockel Systemen nicht behandeln wie 2x32 sondern als 8x8, damit der Speicher optimal zugewiesen werden kann, und man sollte natürlich auf jeden Channel mind. ein Speichermodul haben.

[tip:ras/core] x86/mce/AMD: Add system physical address translation for AMD Fam17h

x86/mce/AMD: Add system physical address translation for AMD Fam17h

The Unified Memory Controllers (UMCs) on Fam17h log a normalized address

in their MCA_ADDR registers. We need to convert that normalized address

to a system phyisical address in order to support a few facilities:

1) To offline poisoned pages in DRAM proactively in the deferred error

handler.

2) To print sysaddr and page info for DRAM ECC errors in EDAC.

Dürfte eher für die Server-Zens mit mehreren Modulen interessant sein? Das heißt die Memory Controller pro Summit Ridge Modul mit ihren jeweils zwei Kanälen arbeiten prinzipiell erstmal vollkommen unabhängig voneinander?

Edit: Das könnte auch einige der Erkennungs- und Performanceprobleme erklären. Ich schätze das ist so in der Software bisher nicht wirklich vorgesehen, dass hier quasi bis zu vier getrennte CPUs auf einem Sockel sitzen. Im Prinzip muss das OS die bei Dual-Sockel Systemen nicht behandeln wie 2x32 sondern als 8x8, damit der Speicher optimal zugewiesen werden kann, und man sollte natürlich auf jeden Channel mind. ein Speichermodul haben.

Zuletzt bearbeitet:

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 14.324

- Renomée

- 1.971

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 3950X

- Mainboard

- MSI MPG X570 GAMING PRO CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 4x 16 GB G.Skill Trident Z RGB, DDR4-3200, CL14

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Intel 600p 1TB

- HDD

- Western Digital WD Red 2 & 3TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

Wäre das dann nicht sowas wie der ganged / unganged Mode der beim Phenom eingeführt wurde?

Damit konnte man ja einstellen ob die 2 Speicherkanäle nur zusammen oder auch unabhängig von einander agieren können.

Bei einem Programm war es natürlich von Vorteil wenn die Kanäle gebündelt sind aber sobald Multithreading / -tasking ernsthaft ins Spiel kam war es günstiger wenn die Kerne gleichzeitig auf jeweils einen Kanal zugreifen können anstatt sich in der Warteschlange anstellen zu müssen.

Damit konnte man ja einstellen ob die 2 Speicherkanäle nur zusammen oder auch unabhängig von einander agieren können.

Bei einem Programm war es natürlich von Vorteil wenn die Kanäle gebündelt sind aber sobald Multithreading / -tasking ernsthaft ins Spiel kam war es günstiger wenn die Kerne gleichzeitig auf jeweils einen Kanal zugreifen können anstatt sich in der Warteschlange anstellen zu müssen.

Ge0rgy

Grand Admiral Special

- Mitglied seit

- 14.07.2006

- Beiträge

- 4.322

- Renomée

- 82

- Mein Laptop

- Lenovo Thinkpad X60s

- Details zu meinem Desktop

- Prozessor

- Phenom II 955 BE

- Mainboard

- DFI LanParty DK 790FXB-M3H5

- Kühlung

- Noctua NH-U12P

- Speicher

- 4GB OCZ Platinum DDR1600 7-7-7 @ 1333 6-6-6

- Grafikprozessor

- Radeon 4850 1GB

- HDD

- Western Digital Caviar Black 1TB

- Netzteil

- Enermax Modu 525W

- Betriebssystem

- Linux, Vista x64

- Webbrowser

- Firefox 3.5

Alles in allem klingt das Posting von dem angeblichen "insider" doch recht positiv. Dass Engineering-Samples noch Bugs haben ist ja nun mal nicht so eine furchtbar ungewöhnliche Neuigkeit. Genau deshalb ist das Ding noch nicht auf dem Markt sondern noch in der Evaluierung.

Warum ier schonwieder der TLB Bug beschworen wird (und kein Wort über den Fdiv-Bug der Pentiums aus dem Blauen Lager, der es auch in Release-Prozessoren geschafft hat) ist mir schleierhaft.

@Atombossler

du kloppst ganz schön große Worte für jemanden der noch keine eigene CPU vorweisen kann.

Hast du eigentlich schonmal, sagen wir, einen 16 Bit Addierer zusammengebaut? - z.b. Auf einem ButterBoard mit TTL-Bausteinen?

Oder wenigstens einen Treiber geschrieben für einen kleinen Controllerchip, man verlangt ja schon garnicht etwas von der Komplexität eines Polaris.

Was mich betrifft bin ich höchst gespannt auf Zen. Nicht übertrieben euphorisch, aber gespannt.

Dass hier schonwieder über ungelegtei Eier geunkt wird ist allerdings typisch. Ich wette wenn Zen bei seinem Release keine 2000% Vorsprung in der Schwan.... ähm, Balkenlänge im IchmachmirmalmeinenBenchamrkweilichSoCoolbin - Shootout vorweisen kann wird schonwieder der Untergang des Abendlandes heraufbeschworen![Augen rollen (sarkastisch) :] :]](https://www.planet3dnow.de/vbulletin/images/smilies/rolleyes.gif)

~Haswell-IPC wäre schonmal ein sehr deutlicher Schritt. - Und man wird da kaum ewig stehenbleiben, Zen+ ist ja auch schonwieder schemenhaft auf der Timeline erkennbar.

Vor allem interessant wie sie diesesmal die Cache-Pipeline hingekriegt haben, das Cachedesign mit dem merkwürdigen Write-Through L1 war ja auch eine der Achillesfersen des Bulldozer-Designs.

Vielleicht ist auch gerade dort der entsprechende Bug angesiedelt. - Also im Cache-Subsystem, dort kann man schnell mal 30 oder 40% Performance vernichten wenn z.b. die Prefetcher nicht sauber arbeiten und die CPU ständig auf ihre Daten warten muss. Das ist wie bei einem Uhrwerk, wenn ein Zahnrädchen an der falschen Stelle klemmt, bringt das die ganze Maschine aus dem Tritt.

Dennoch, solange keins von den Dingern im Regal liegt mit dem erwähnten Bug ist es absolut kein Grund hier rumzumaulen. Schließlich fragt auch bei den Intelschen Engineering-Samples keiner ob die Bugfrei sind (oder verlangt das) und käme schon garkeiner auf die Idee dass deswegen die Release-CPUs Schrott sein müssten.

Fragt mal einen KFZ-Ingineur wie viele Fehler ein Prototyp einer neuen Fahrzeugklasse oftmals hat, die erst bei den Tests auffallen - sonst bräuchte man die ja nicht machen.

Womöglich ist das sogar ein Bug der nur auf Muktisockel-Konfigurationen auftritt und den Desktop nichtmal tangieren würde (aber natürlich trotzdem gefixt werden muss) - Wir wissen es einfach nicht. Aber hauptsache den Lichtbringer an die Wand gekachelt...

Grüße,

Meiner Einer

Warum ier schonwieder der TLB Bug beschworen wird (und kein Wort über den Fdiv-Bug der Pentiums aus dem Blauen Lager, der es auch in Release-Prozessoren geschafft hat) ist mir schleierhaft.

@Atombossler

du kloppst ganz schön große Worte für jemanden der noch keine eigene CPU vorweisen kann.

Hast du eigentlich schonmal, sagen wir, einen 16 Bit Addierer zusammengebaut? - z.b. Auf einem ButterBoard mit TTL-Bausteinen?

Oder wenigstens einen Treiber geschrieben für einen kleinen Controllerchip, man verlangt ja schon garnicht etwas von der Komplexität eines Polaris.

Was mich betrifft bin ich höchst gespannt auf Zen. Nicht übertrieben euphorisch, aber gespannt.

Dass hier schonwieder über ungelegtei Eier geunkt wird ist allerdings typisch. Ich wette wenn Zen bei seinem Release keine 2000% Vorsprung in der Schwan.... ähm, Balkenlänge im IchmachmirmalmeinenBenchamrkweilichSoCoolbin - Shootout vorweisen kann wird schonwieder der Untergang des Abendlandes heraufbeschworen

![Augen rollen (sarkastisch) :] :]](https://www.planet3dnow.de/vbulletin/images/smilies/rolleyes.gif)

~Haswell-IPC wäre schonmal ein sehr deutlicher Schritt. - Und man wird da kaum ewig stehenbleiben, Zen+ ist ja auch schonwieder schemenhaft auf der Timeline erkennbar.

Vor allem interessant wie sie diesesmal die Cache-Pipeline hingekriegt haben, das Cachedesign mit dem merkwürdigen Write-Through L1 war ja auch eine der Achillesfersen des Bulldozer-Designs.

Vielleicht ist auch gerade dort der entsprechende Bug angesiedelt. - Also im Cache-Subsystem, dort kann man schnell mal 30 oder 40% Performance vernichten wenn z.b. die Prefetcher nicht sauber arbeiten und die CPU ständig auf ihre Daten warten muss. Das ist wie bei einem Uhrwerk, wenn ein Zahnrädchen an der falschen Stelle klemmt, bringt das die ganze Maschine aus dem Tritt.

Dennoch, solange keins von den Dingern im Regal liegt mit dem erwähnten Bug ist es absolut kein Grund hier rumzumaulen. Schließlich fragt auch bei den Intelschen Engineering-Samples keiner ob die Bugfrei sind (oder verlangt das) und käme schon garkeiner auf die Idee dass deswegen die Release-CPUs Schrott sein müssten.

Fragt mal einen KFZ-Ingineur wie viele Fehler ein Prototyp einer neuen Fahrzeugklasse oftmals hat, die erst bei den Tests auffallen - sonst bräuchte man die ja nicht machen.

Womöglich ist das sogar ein Bug der nur auf Muktisockel-Konfigurationen auftritt und den Desktop nichtmal tangieren würde (aber natürlich trotzdem gefixt werden muss) - Wir wissen es einfach nicht. Aber hauptsache den Lichtbringer an die Wand gekachelt...

Grüße,

Meiner Einer

Mente

Grand Admiral Special

- Mitglied seit

- 23.05.2009

- Beiträge

- 3.671

- Renomée

- 135

- Aktuelle Projekte

- constalation astroids yoyo

- Lieblingsprojekt

- yoyo doking

- Meine Systeme

- Ryzen 3950x

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- AMD 5800X3D

- Mainboard

- Asus ROG Crosshair VIII Dark Hero

- Kühlung

- Headkiller IV

- Speicher

- 3800CL14 G.Skill Trident Z silber/rot DIMM Kit 32GB, DDR4-3600, CL15-15-15-35 (F4-3600C15D-16GTZ)

- Grafikprozessor

- AMD Radeon RX 6900 XT Ref. @Alphacool

- Display

- MSI Optix MAG27CQ

- SSD

- SN8502TB,MX5001TB,Vector150 480gb,Vector 180 256gb,Sandisk extreme 240gb,RD400 512gb

- HDD

- n/a

- Optisches Laufwerk

- n/a

- Soundkarte

- Soundblaster X4

- Gehäuse

- Phanteks Enthoo Pro 2 Tempered Glass

- Netzteil

- Seasonic Prime GX-850 850W

- Tastatur

- Logitech G19

- Maus

- Logitech G703

- Betriebssystem

- Win 10 pro

- Webbrowser

- IE 11 Mozilla Opera

- Verschiedenes

- Logitech PRO RENNLENKRAD DD

hm ich halte die avx Einheit meines 4790k auch für BUG behaftet, da sie die cpu ganz an ihre grenzen bringt, das dann mal 0,05volt drauf gehauen werden ist Thermal betrachtet in einigen Anwendungen sehr grenzwertig (Boinc Asteroid .... ). Und da redet auch keiner von Bug.

Interessant fand ich es schon was sie so gesehen/testet haben aber es heist immer noch warten.

Was mich ehr verwundert ist die intel Meldungen zu 2018 Cpus das gabs doch noch nie so weit vorher?

lg

Interessant fand ich es schon was sie so gesehen/testet haben aber es heist immer noch warten.

Was mich ehr verwundert ist die intel Meldungen zu 2018 Cpus das gabs doch noch nie so weit vorher?

lg

mulle

Admiral Special

- Mitglied seit

- 07.04.2013

- Beiträge

- 1.104

- Renomée

- 83

- BOINC-Statistiken

- Mein Laptop

- Asus Zenbook UX3430UA

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 1700

- Mainboard

- ASUS B350 Prime Plus

- Kühlung

- AMD Wraith Spire

- Speicher

- 4 x 8 GB Kinston HyperX Fury (HX424C15FB2K4)

- Grafikprozessor

- Sapphire HD 6450 passiv

- Display

- Eizo EV2455-BK

- SSD

- Samsung NVME 960 EVO 500 GB

- Gehäuse

- Jonsbo U4

- Netzteil

- beQuiet Pure Power 10 CM (400W 80+ Silver)

- Betriebssystem

- Windows 10 Pro

- Webbrowser

- Firefox

Der FDIV-Bug bei Intel wurde schon sehr negativ bewertet, damals.Und da redet auch keiner von Bug.

Aber seitdem war es gefühlt "schon immer" so, dass auf AMD stärker draufgedroschen wurde. Das läuft ja schon jetzt wieder, indem schon vermeintliche bzw. "gefühlte" Fehler durchsickern, auch wenn die nie so beim Kunden ankommen werden...

Aus diesem Grund dürfen sie sich beim Zen-Launch IMHO *keine* Fehler leisten. Der Polaris-Launch war diesbezüglich kein Ruhmesblatt; AMD darf keine Angriffsfläche zeigen.

Umgedeutet könnte es ja auch sein, dass mit den CPUIDs und dem BIOS ja ggf. bei manchen "Plaudertaschen" das Testsystem seitens AMD gezielt gebremst werden sollte, damit die wahre Leistung überraschend ans Licht kommt. Ggf. gibt es mehrere Bremsfeatures und entsprechende "Leaks" könnte man je nach "geleaktem" Verhalten bei AMD nachvollziehen. Aber gut, das ist ja schon gegen Ockham's Razor.

Atombossler

Admiral Special

- Mitglied seit

- 28.04.2013

- Beiträge

- 1.425

- Renomée

- 65

- Standort

- Andere Sphären

- Mein Laptop

- Thinkpad 8

- Details zu meinem Desktop

- Prozessor

- A8-7600@3.25Ghz

- Mainboard

- Asus A88X-PRO

- Kühlung

- NoFan CR80 EH

- Speicher

- 16Gb G-Skill Trident-X DDR3 2400

- Grafikprozessor

- APU

- Display

- Acer UHD 4K2K

- SSD

- Samsung 850 PRO

- HDD

- 2xSamsung 1TB HDD (2,5")

- Optisches Laufwerk

- Plexi BD-RW

- Soundkarte

- OnBoard Geraffel

- Gehäuse

- Define R2

- Netzteil

- BeQuiet

- Betriebssystem

- Win7x64-PRO

- Webbrowser

- Chrome

Es wuerde mich eher wundern, wenn die Tradition nicht fortgesetzt wird!

Der Fix kann alles moegliche sein, ich vermute eher sie nutzen nur ein BIOS welches sehr klein ist vom Speicherplatz her.The important thing here is that the 16Thread/8-Core CPU is minimum 5960X performance if not better actually. (Based on Cinebench R15) with the error fix disabled.

Das waere dann mit einem UEFI weniger problematisch, nur braucht das UEFI den gesamten CPUID String und nicht nur ein Test Sample String.

Beim Naples will man scheinbar fehler an der SMT implementierung gefunden haben, womoeglich noch mit Intel Code und keinen eigenstaendigen von AMD.![Augen rollen (sarkastisch) :] :]](https://www.planet3dnow.de/vbulletin/images/smilies/rolleyes.gif)

Na ja, genau das meinte ich ja aber. Das wird nicht reichen ...

Der Vishera ist da jetzt schon schneller im Single Core und beim Multi fehlt nicht viel und das sind 4M/8T.

40% + auf Excavator sollten anders aussehen Bug oder nicht.

--- Update ---

Alles in allem klingt das Posting von dem angeblichen "insider" doch recht positiv. Dass Engineering-Samples noch Bugs haben ist ja nun mal nicht so eine furchtbar ungewöhnliche Neuigkeit. Genau deshalb ist das Ding noch nicht auf dem Markt sondern noch in der Evaluierung.

Warum ier schonwieder der TLB Bug beschworen wird (und kein Wort über den Fdiv-Bug der Pentiums aus dem Blauen Lager, der es auch in Release-Prozessoren geschafft hat) ist mir schleierhaft.

@Atombossler

du kloppst ganz schön große Worte für jemanden der noch keine eigene CPU vorweisen kann.

Hast du eigentlich schonmal, sagen wir, einen 16 Bit Addierer zusammengebaut? - z.b. Auf einem ButterBoard mit TTL-Bausteinen?

Oder wenigstens einen Treiber geschrieben für einen kleinen Controllerchip, man verlangt ja schon garnicht etwas von der Komplexität eines Polaris.

Was mich betrifft bin ich höchst gespannt auf Zen. Nicht übertrieben euphorisch, aber gespannt.

Dass hier schonwieder über ungelegtei Eier geunkt wird ist allerdings typisch. Ich wette wenn Zen bei seinem Release keine 2000% Vorsprung in der Schwan.... ähm, Balkenlänge im IchmachmirmalmeinenBenchamrkweilichSoCoolbin - Shootout vorweisen kann wird schonwieder der Untergang des Abendlandes heraufbeschworen

~Haswell-IPC wäre schonmal ein sehr deutlicher Schritt. - Und man wird da kaum ewig stehenbleiben, Zen+ ist ja auch schonwieder schemenhaft auf der Timeline erkennbar.

Vor allem interessant wie sie diesesmal die Cache-Pipeline hingekriegt haben, das Cachedesign mit dem merkwürdigen Write-Through L1 war ja auch eine der Achillesfersen des Bulldozer-Designs.

Vielleicht ist auch gerade dort der entsprechende Bug angesiedelt. - Also im Cache-Subsystem, dort kann man schnell mal 30 oder 40% Performance vernichten wenn z.b. die Prefetcher nicht sauber arbeiten und die CPU ständig auf ihre Daten warten muss. Das ist wie bei einem Uhrwerk, wenn ein Zahnrädchen an der falschen Stelle klemmt, bringt das die ganze Maschine aus dem Tritt.

Dennoch, solange keins von den Dingern im Regal liegt mit dem erwähnten Bug ist es absolut kein Grund hier rumzumaulen. Schließlich fragt auch bei den Intelschen Engineering-Samples keiner ob die Bugfrei sind (oder verlangt das) und käme schon garkeiner auf die Idee dass deswegen die Release-CPUs Schrott sein müssten.

Fragt mal einen KFZ-Ingineur wie viele Fehler ein Prototyp einer neuen Fahrzeugklasse oftmals hat, die erst bei den Tests auffallen - sonst bräuchte man die ja nicht machen.

Womöglich ist das sogar ein Bug der nur auf Muktisockel-Konfigurationen auftritt und den Desktop nichtmal tangieren würde (aber natürlich trotzdem gefixt werden muss) - Wir wissen es einfach nicht. Aber hauptsache den Lichtbringer an die Wand gekachelt...

Grüße,

Meiner Einer

Mei, ungelegte Eier ...

... wir sind hier ja schliesslich im Speku Forum und was tut man da?

--- Update ---

Aus diesem Grund dürfen sie sich beim Zen-Launch IMHO *keine* Fehler leisten. Der Polaris-Launch war diesbezüglich kein Ruhmesblatt; AMD darf keine Angriffsfläche zeigen.

So ist es, leider bekommen Sie's aber immer wieder hin irgend etwas zu versemmeln.

Dann lass es eben einen Monat länger dauern, Weihnachten ist doch dann eh schon vorbei, kommt doch nicht drauf an.

Das Teil muss einfach rundum gut werden, die ganzen Tester machen es noch schlecht genug.

Zuletzt bearbeitet:

Beim Naples will man scheinbar fehler an der SMT implementierung gefunden haben, womoeglich noch mit Intel Code und keinen eigenstaendigen von AMD.![Augen rollen (sarkastisch) :] :]](https://www.planet3dnow.de/vbulletin/images/smilies/rolleyes.gif)

Wenn "Intel-Code" nicht läuft ist es ein Bug.

Ähnliche Themen

- Antworten

- 91

- Aufrufe

- 8K

- Antworten

- 14

- Aufrufe

- 930

- Antworten

- 102

- Aufrufe

- 11K

- Antworten

- 3

- Aufrufe

- 2K