App installieren

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: This feature may not be available in some browsers.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

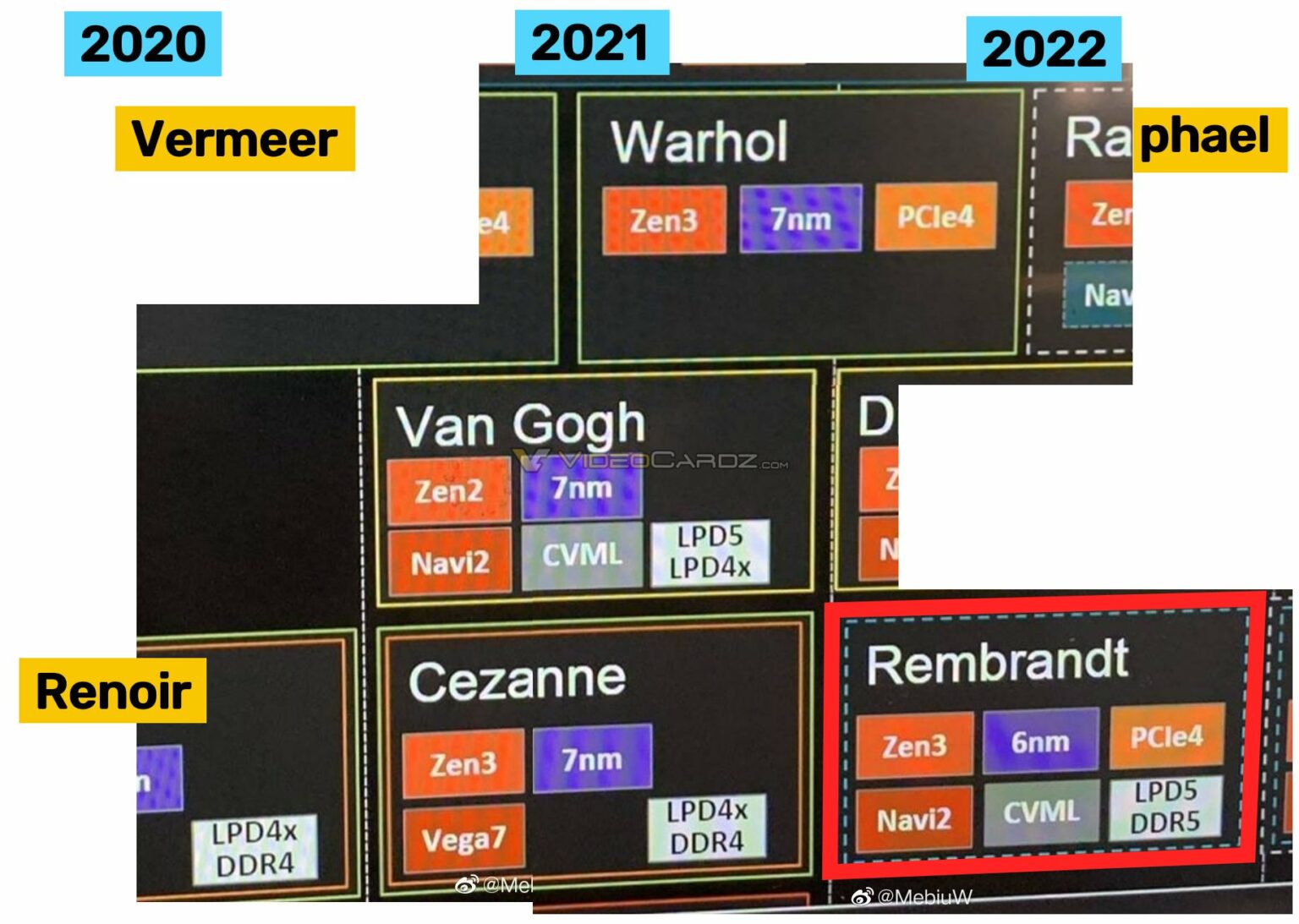

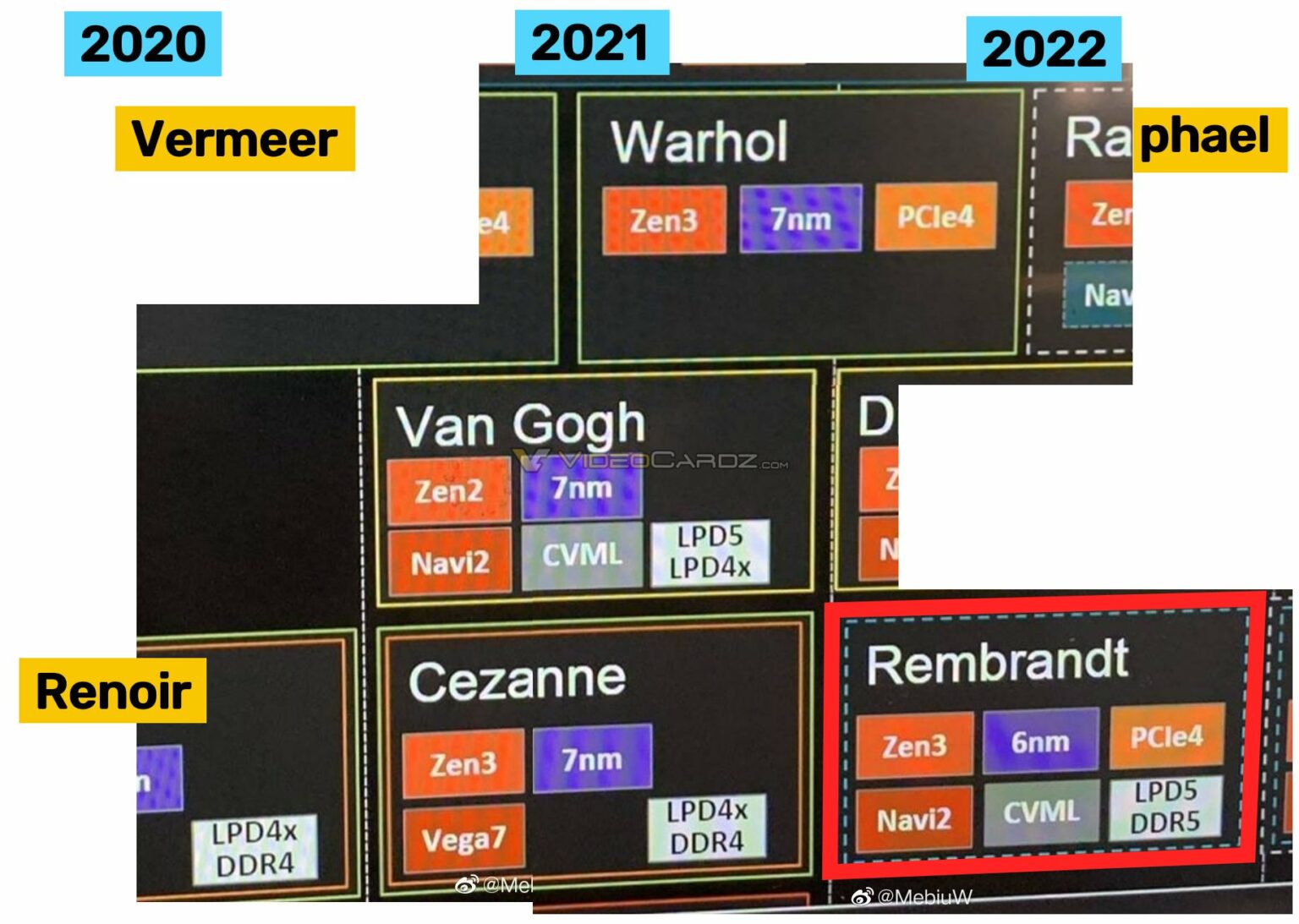

AMD - Zen 3 - 7 nm / 6 nm - Vermeer, Cezanne, Warhol, Rembrandt, Dragon Point

- Ersteller Tu334

- Erstellt am

Pinnacle Ridge

Vice Admiral Special

- Mitglied seit

- 04.03.2017

- Beiträge

- 528

- Renomée

- 7

Wenn man Ausführungseinheiten hinzufügt, wäre dann mit Zen4 nicht bald schon SMT4 zumindest im Serverbereich sinnvoll?

BavarianRealist

Grand Admiral Special

- Mitglied seit

- 06.02.2010

- Beiträge

- 3.358

- Renomée

- 80

@Zen3 / Zen3+:

Cezanne soll Zen3 enthalten, aber noch die alte Vega-GPU nutzen. Parallel soll VanGogh zwar mit dem "alten" Zen2 aber dafür mit der neuen Navi-GPU kommen. Gleichzeitig wissen wir, dass in den Konsolen-SoCs Zen2- und Navi2-GPUs in einem Silizium sind, was bedeutet, dass sie beide den gleichen 7nm-Prozess nutzen.

Von den Konsolen-SoCs wissen wir, dass sie einen "advanced" 7nm-Prozess nutzen, aber welchen? Von Zen3 wissen wir, dass es weiterhin der "alte" 7nm-HPC-Prozess ist, also vermutlich N7P. Für die Konsolen-SoCs sind dagegen die Produktionskosten sehr wichtig: der N7+ mit EUV ist 18% dichter, ist etwas effizienter und zuletzt sollen seine Produktionskosten etwas geringer sein, weil weniger Masken/Prozess-Schritte nötig sind.

@VanGogh:

VanGogh soll low-Power sein und die neue RDNA2-iGPU erhalten, ähnlich dem Aufbau der Konsolen-SoCs.. Zudem wird VanGogh auch für die Main-Stream-Notebooks dienen, die keine dedizierte GPU erhalten und zudem mit günstigeren Kühllösungen auskommen. Hieß es nicht auch, dass Zen2 der Konsulen ein paar Änderungen gegenüber Zen2 haben soll? Und er muss im selben Prozess wie RDNA2 sein, vermutlich auf 7N+ portiert worden, um auf einem Silizium mit Navi2 landen zu können. Das würde unterstellen, dass Navi2 ebenfalls bereits N7+ nutzt, was Sinn macht, weil es Diesize, Energie und Kosten spart. Und womit vermutlich erklärt wäre, warum Cezanne weiterhin mit Vega auskommen muss: weil Zen3 noch den N7P nutzt, und nicht auf die Schnelle auch noch auf N7+ portiert werden kann. Für Cezanne geht es aber um Performance, weil dieser in TDPs ab 35 Watt antreten wird.

Cezanne dürfte sich vor allem dadurch unterscheiden, dass er das Zen3-Core hat. Und nachdem er in teurere Gaming-Notebooks kommen soll, braucht er auch sonst alle aktuellen Schnittstellen-Standart, also wohl auch endlich USB4. VanGogh muss sich dagegen mit dem "alten" Zen2 zufrieden geben, weil es wohl nur diesen bereits in N7+ geben dürfte. Aber auch hier erwarte ich USB4. Und ebenso erwarte ich noch einen Chipsat für AM4, der noch USB4 erhält.

@ Cezanne:

Vergleicht man Renoir mit Matisse, dann zeigt sich, dass Renoir aufgrund der Single-Die-Lösung und die dadurch schnelleren Ramzugriffe gut für Games ist, obwohl der den viel kleineren Cache hat. Wie dürfte dann Cezanne für Games gegenüber 5800X abschneiden? Evtl. noch besser als 5950X? Nachdem sowohl Tigerlake-H als auch Rocket-Lake auch nur 8-Corer sind, könnte dann am Ende aus Cezanne der beste Gaming-Konkurrent für Rocket-Lake entstehen, zumal hier die Wäremabfuhr über das größere Single-Die besser laufen dürfte, als es die Zen3-Chiplets erlauben.

@Warhol:

Ich bezweifle, dass AMD in 2021 noch ein überarbeitetes Zen3-Chiplet oder eine Portierung von Zen3 auf N7+ bringen wid, weil einerseits ein Prozess-Sprung auf den nicht mehr ganz neuen N7+ in 2021 überflüssig sein dürfte, da es dann bereits N6 und N5 etc. geben wird. Und für N5 steht dann Zen4 an. Mit DDR5 findet sich die Performance-Krone dann auf jeden Fall auf der AM5-Plattform. Andererseits braucht AMD auch die DDR4-Plattform noch lange, vor allem für die günstigern Mainstream-Lösungen.

Warhol dürfte daher die finanle CPU für DDR4/AM4 werden. Sie dürfte sich meines Erachtens nur im I/O-Die und der TDP von Vermeer unterscheiden: AMD benötigt einerseits unbedingt das Update auf USB4 mittels finalem AM4-Chipsatz. Für eine weitere Steigerung der SC-Scores wäre wohl der einfachste Weg, höhere Takte, die wiederum am einfachsten mit höherer TDP zu erreichen sind. In Warhol muss das Zen3-Chiplet besser gekühlt werden, für höhere TDP, was auch für das I/O zutrifft. Letztlich profitieren vor allem die Schnittstellen von höherer Spannung, also die Inter-Chiplet-Kommunikation als auch der Ram-Controller. Damit sollten dann die 5Ghz ohne Probleme möglich sein und die Latenzen nochmals etwas besser ausfallen sodass dann Warhol dann oberhalb von Rocket-Lake antreten kann.

Cezanne soll Zen3 enthalten, aber noch die alte Vega-GPU nutzen. Parallel soll VanGogh zwar mit dem "alten" Zen2 aber dafür mit der neuen Navi-GPU kommen. Gleichzeitig wissen wir, dass in den Konsolen-SoCs Zen2- und Navi2-GPUs in einem Silizium sind, was bedeutet, dass sie beide den gleichen 7nm-Prozess nutzen.

Von den Konsolen-SoCs wissen wir, dass sie einen "advanced" 7nm-Prozess nutzen, aber welchen? Von Zen3 wissen wir, dass es weiterhin der "alte" 7nm-HPC-Prozess ist, also vermutlich N7P. Für die Konsolen-SoCs sind dagegen die Produktionskosten sehr wichtig: der N7+ mit EUV ist 18% dichter, ist etwas effizienter und zuletzt sollen seine Produktionskosten etwas geringer sein, weil weniger Masken/Prozess-Schritte nötig sind.

@VanGogh:

VanGogh soll low-Power sein und die neue RDNA2-iGPU erhalten, ähnlich dem Aufbau der Konsolen-SoCs.. Zudem wird VanGogh auch für die Main-Stream-Notebooks dienen, die keine dedizierte GPU erhalten und zudem mit günstigeren Kühllösungen auskommen. Hieß es nicht auch, dass Zen2 der Konsulen ein paar Änderungen gegenüber Zen2 haben soll? Und er muss im selben Prozess wie RDNA2 sein, vermutlich auf 7N+ portiert worden, um auf einem Silizium mit Navi2 landen zu können. Das würde unterstellen, dass Navi2 ebenfalls bereits N7+ nutzt, was Sinn macht, weil es Diesize, Energie und Kosten spart. Und womit vermutlich erklärt wäre, warum Cezanne weiterhin mit Vega auskommen muss: weil Zen3 noch den N7P nutzt, und nicht auf die Schnelle auch noch auf N7+ portiert werden kann. Für Cezanne geht es aber um Performance, weil dieser in TDPs ab 35 Watt antreten wird.

Cezanne dürfte sich vor allem dadurch unterscheiden, dass er das Zen3-Core hat. Und nachdem er in teurere Gaming-Notebooks kommen soll, braucht er auch sonst alle aktuellen Schnittstellen-Standart, also wohl auch endlich USB4. VanGogh muss sich dagegen mit dem "alten" Zen2 zufrieden geben, weil es wohl nur diesen bereits in N7+ geben dürfte. Aber auch hier erwarte ich USB4. Und ebenso erwarte ich noch einen Chipsat für AM4, der noch USB4 erhält.

@ Cezanne:

Vergleicht man Renoir mit Matisse, dann zeigt sich, dass Renoir aufgrund der Single-Die-Lösung und die dadurch schnelleren Ramzugriffe gut für Games ist, obwohl der den viel kleineren Cache hat. Wie dürfte dann Cezanne für Games gegenüber 5800X abschneiden? Evtl. noch besser als 5950X? Nachdem sowohl Tigerlake-H als auch Rocket-Lake auch nur 8-Corer sind, könnte dann am Ende aus Cezanne der beste Gaming-Konkurrent für Rocket-Lake entstehen, zumal hier die Wäremabfuhr über das größere Single-Die besser laufen dürfte, als es die Zen3-Chiplets erlauben.

@Warhol:

Ich bezweifle, dass AMD in 2021 noch ein überarbeitetes Zen3-Chiplet oder eine Portierung von Zen3 auf N7+ bringen wid, weil einerseits ein Prozess-Sprung auf den nicht mehr ganz neuen N7+ in 2021 überflüssig sein dürfte, da es dann bereits N6 und N5 etc. geben wird. Und für N5 steht dann Zen4 an. Mit DDR5 findet sich die Performance-Krone dann auf jeden Fall auf der AM5-Plattform. Andererseits braucht AMD auch die DDR4-Plattform noch lange, vor allem für die günstigern Mainstream-Lösungen.

Warhol dürfte daher die finanle CPU für DDR4/AM4 werden. Sie dürfte sich meines Erachtens nur im I/O-Die und der TDP von Vermeer unterscheiden: AMD benötigt einerseits unbedingt das Update auf USB4 mittels finalem AM4-Chipsatz. Für eine weitere Steigerung der SC-Scores wäre wohl der einfachste Weg, höhere Takte, die wiederum am einfachsten mit höherer TDP zu erreichen sind. In Warhol muss das Zen3-Chiplet besser gekühlt werden, für höhere TDP, was auch für das I/O zutrifft. Letztlich profitieren vor allem die Schnittstellen von höherer Spannung, also die Inter-Chiplet-Kommunikation als auch der Ram-Controller. Damit sollten dann die 5Ghz ohne Probleme möglich sein und die Latenzen nochmals etwas besser ausfallen sodass dann Warhol dann oberhalb von Rocket-Lake antreten kann.

Zuletzt bearbeitet:

- Mitglied seit

- 16.10.2000

- Beiträge

- 24.371

- Renomée

- 9.696

- Standort

- East Fishkill, Minga, Xanten

- Aktuelle Projekte

- Je nach Gusto

- Meine Systeme

- Ryzen 9 5900X, Ryzen 7 3700X

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Samsung P35 (16 Jahre alt ;) )

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5900X

- Mainboard

- ASRock B550

- Speicher

- 2x 16 GB DDR4 3200

- Grafikprozessor

- GeForce GTX 1650

- Display

- 27 Zoll Acer + 24 Zoll DELL

- SSD

- Samsung 980 Pro 256 GB

- HDD

- diverse

- Soundkarte

- Onboard

- Gehäuse

- Fractal Design R5

- Netzteil

- be quiet! Straight Power 10 CM 500W

- Tastatur

- Logitech Cordless Desktop

- Maus

- Logitech G502

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox, Vivaldi

- Internetanbindung

- ▼250 MBit ▲40 MBit

@Warhol:

Ich bezweifle, dass AMD in 2021 noch ein überarbeitetes Zen3-Chiplet oder eine Portierung von Zen3 auf N7+ bringen wid, weil einerseits ein Prozess-Sprung auf den nicht mehr ganz neuen N7+ in 2021 überflüssig sein dürfte, da es dann bereits N6 und N5 etc. geben wird. Und für N5 steht dann Zen4 an. Mit DDR5 findet sich die Performance-Krone dann auf jeden Fall auf der AM5-Plattform. Andererseits braucht AMD auch die DDR4-Plattform noch lange, vor allem für die günstigern Mainstream-Lösungen.

Das ist ja die Frage. Ich stehe ja eh diesem Zen 3+ skeptisch gegenüber, dieselben Gerüchte (allerdings ohne Codenamen) gab es ja schon bei Zen 2.

Außerdem hat AMD ja anklingen lassen, dass dies der letzte Desktop-Prozessor (ohne integrierte Grafik) für AM4 ist.

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Ich sehe auch nicht was eine Zen3+-CPU Linie bringen soll vor Zen4 in 5nm. Die APUs werden der AM4-Plattform noch eine ganze Weile Nachfolger liefern, die möglicherweise Feintunig an den Cores haben werden im Zuge der Integration. Wer möchte kann das ja gerne dann Zen3+-Kerne nennen. Aber auf Chiplets sehe ich auch keine Grund für AMD die Kosten zu investieren. Threadripper wird Zen3 bekommen und alles was sich über 299,- $ befindet wird damit im ersten Schritt ausgestattet sein. Darunter wird Zen2 noch eine Weile seine Käufer bedienen.

- Mitglied seit

- 16.10.2000

- Beiträge

- 24.371

- Renomée

- 9.696

- Standort

- East Fishkill, Minga, Xanten

- Aktuelle Projekte

- Je nach Gusto

- Meine Systeme

- Ryzen 9 5900X, Ryzen 7 3700X

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Samsung P35 (16 Jahre alt ;) )

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5900X

- Mainboard

- ASRock B550

- Speicher

- 2x 16 GB DDR4 3200

- Grafikprozessor

- GeForce GTX 1650

- Display

- 27 Zoll Acer + 24 Zoll DELL

- SSD

- Samsung 980 Pro 256 GB

- HDD

- diverse

- Soundkarte

- Onboard

- Gehäuse

- Fractal Design R5

- Netzteil

- be quiet! Straight Power 10 CM 500W

- Tastatur

- Logitech Cordless Desktop

- Maus

- Logitech G502

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox, Vivaldi

- Internetanbindung

- ▼250 MBit ▲40 MBit

Ich sehe auch nicht was eine Zen3+-CPU Linie bringen soll vor Zen4 in 5nm. Die APUs werden der AM4-Plattform noch eine ganze Weile Nachfolger liefern, die möglicherweise Feintunig an den Cores haben werden im Zuge der Integration. Wer möchte kann das ja gerne dann Zen3+-Kerne nennen.

Ich vermute, dass in den Codenamen Warhol zuviel hineininterpretiert wird.

Mit Pollock hat AMD ja für 2 SKUs auch schon einen Codenamen verwendet.

Vielleicht ist Warhol ja nur das Äquivalent zum 3000XT und den bringt man dann halt auf 5 GHz boost und hat noch mal nen Werbeeffekt.

Für Rocket Lake S wird es wohl langen.

BavarianRealist

Grand Admiral Special

- Mitglied seit

- 06.02.2010

- Beiträge

- 3.358

- Renomée

- 80

Vielleicht ist Warhol ja nur das Äquivalent zum 3000XT und den bringt man dann halt auf 5 GHz boost und hat noch mal nen Werbeeffekt.

Für Rocket Lake S wird es wohl langen.

Nachdem AMD mit Vermeer aktuell so oder so die alleinige Krone hat, wozu dann zu viel Pulver verschießen? Die 5,0Ghz hätte man sicher haben können, wenn man nur hätte wollen. Selbst der 5600X hat schon 4,6Ghz Boost. Da man keinen Druck hat, kann man von Zen3 erst mal alle guten Stücke Milan vorbehalten, wo man nicht so einfach später Schnellere nachlegen kann.

Womöglich ist Warhol nichts anderes als Vermeer mit höherer TDP und besser selektieren Zen3-Chiplets, sodass man diesen nochmals werbewirksam gegen Rocket-Lake patzieren kann.

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Ich denke AMD hat es Intel sehr schwer gemacht mit den 5 GHz noch zu punkten, wenn diese am Ende nicht schneller sind als Zen3.

Es ist sowieso absurd nach den Frequenzen zu schauen, ohne den Workload zu beachten. Eine GPU hat bei halber Frequenz deutlich mehr Rechenpower zu bieten.

Selbst Intels eigene AVX-Workloads erfordern ein reduzieren der Frequenz um mehr Rechenleitsung zu ermöglichen.

Es ist sowieso absurd nach den Frequenzen zu schauen, ohne den Workload zu beachten. Eine GPU hat bei halber Frequenz deutlich mehr Rechenpower zu bieten.

Selbst Intels eigene AVX-Workloads erfordern ein reduzieren der Frequenz um mehr Rechenleitsung zu ermöglichen.

BavarianRealist

Grand Admiral Special

- Mitglied seit

- 06.02.2010

- Beiträge

- 3.358

- Renomée

- 80

Es würde mich aber schon wundern, wenn AMD das I/O-Chiplet nicht überarbeiten würde, zumal ein neues Desing in 12nm weit billiger als eines in 7nm ist.

Aber womöglich soll das neue I/O-Chiplet ja im neuen 12LP+-Prozess von GF kommen. Und der geht halt erst im neuen Jahr in Serie. Laut GF vom 30.06.2020 heißt es "Several 12LP+ tape-outs are scheduled for the second half of 2020", worin auch das neue I/O-Chiplet bereits im Tape-Out mit dabei, aber als Silizium dann eben erste in H1/2021 verfügar sein könnte. Dann würde Warhol in H1/2021 Sinn machen...

Zudem hier vom 24.09.2020 Infos über eine Zusammenarbeit mit Synopsis, wodurch der 12LP+ Prozess nun auch USB4 und PCI5-Controller-Blocks hat. Waren nicht die X570-Chipsets und das I/O angeblich das selbe Die? Dann macht das Ganze Sinn, dass Vermeer noch das alte I/O hat und ebenso der neue 670X-Chipset noch fehlt, weil einfach die Produktion vom 12LP+ sich womöglich verzögert hat....dann kommt Warhol mit 670X eben in H1/2021? Mehr dazu hier auf pcgameshardware zum 12nm-I/O-Chiplet

Aber womöglich soll das neue I/O-Chiplet ja im neuen 12LP+-Prozess von GF kommen. Und der geht halt erst im neuen Jahr in Serie. Laut GF vom 30.06.2020 heißt es "Several 12LP+ tape-outs are scheduled for the second half of 2020", worin auch das neue I/O-Chiplet bereits im Tape-Out mit dabei, aber als Silizium dann eben erste in H1/2021 verfügar sein könnte. Dann würde Warhol in H1/2021 Sinn machen...

Zudem hier vom 24.09.2020 Infos über eine Zusammenarbeit mit Synopsis, wodurch der 12LP+ Prozess nun auch USB4 und PCI5-Controller-Blocks hat. Waren nicht die X570-Chipsets und das I/O angeblich das selbe Die? Dann macht das Ganze Sinn, dass Vermeer noch das alte I/O hat und ebenso der neue 670X-Chipset noch fehlt, weil einfach die Produktion vom 12LP+ sich womöglich verzögert hat....dann kommt Warhol mit 670X eben in H1/2021? Mehr dazu hier auf pcgameshardware zum 12nm-I/O-Chiplet

Zuletzt bearbeitet:

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Ich verstehe deinen Beitrag nicht so richtig. Die Ryzen IO-Dies für die 3xxx-Serie werden schon in 12LP von GF hergestellt und nicht in 7nm - also ist hier kein Druck etwas schnell billiger zu machen, sondern es würde die Kosten erhöhen jetzt direkt ein neues IO-für Warhol auf AM4 zu nutzen. USB4 und PCIe5 sind auf der AM4 Plattform nicht vorhanden und eine neue Mainboard-Generation noch vor Zen4 mit diesen Features würde das AM4-Versprechen der Kompatibilität erneut durch die Presse peitschen. AMD wird das auf diese Weise wohl nicht mehr machen, da es nicht sinnvoll an den Endkunden transportierbar ist, wie die Mainboardhersteller Ihre Produkte segmentieren.

Allerdings wäre es möglich, dass neue Feature des IO-Dies frei geschaltet werden, und so etwas wie ein X590, über den schon einmal spekuliert wurde erscheitn. Nur eben kein neues Design des IO-Chips. Hier wurden die deaktivierten Reserven mal thematisiert:

www.pcgameshardware.de

www.pcgameshardware.de

Edit:

1. AMD plant möglicherweise einen Consumer IO-Chip ab AM5, der sich vom Server/TRX-Chipsatz unterscheidet. Das wäre eine sinnvolle Abgrenzung ab einer mittlerweile erreichten Größenordnung. Mir würde z.B. ein Weg gefallen eine APU als IO-Chip zu nutzen und ein 8-Core Chiplet anzubinden gefallen - das könnte auch der Weg sein in Zukunft allen AM5 Boards iGPU zu bescheren. Da wären IO-Chipsätze nur noch Server/Workstastion orientiert.

2. Und beim näheren darüber nachdenken erklären sich vielleicht die seltsame kleinen Unterschiede der APUs in der Roadmap - es kommt ein IF-Connect für ein Chiplet dran und fertig Das wäre mal ein extrem eleganter Weg bis 16-Cores im Desktop.

Das wäre mal ein extrem eleganter Weg bis 16-Cores im Desktop.

Hier mal nach einer kurzen Recherche ob das passt, eine Theorie, gegen die ich bisher keine Anzeichen gefunden habe.

Wir kennen ja diese zusammen gestückelte Roadmap:

Hier ist es ja etwas rätselhaft warum bei Raphael Navi2 als iGPU mit gestrichelten Linien belegt ist, was als so etwas wie "optional" gedeutet werden könnte.

Was wenn AMD sich dachte, wir fertigen die APU in 6nm günstig und verwenden Sie dann als IO-Die für Raphael um 5nm Wafer zu sparen (es wird nur ein 5nm Chiplet benötigt für 16 Kerne). Das ganze dann bei 16-Core Desktop SKUs als Big-Little-Kerne organisiert, um Performance Unterschiede zu berücksichtigen, die aus der unterschiedlichen Fertigung entstehen. Rembrandt kann noch stärker auf Mobile optimiert werden, während das Raphael-Chiplet auch höhere Powerbudgets abrufen kann um höhere Taktraten zu erzielen. Rapahel kann zudem dann mit dem Server-IO-Die zu Threadripper und EPYC verbunden werden, ohne GPU oder mit CDNA GPU-Chiplets ausgestattet oder eben klassisch mit dGPUs zusammen in der Racks arbeiten.

Allerdings wäre es möglich, dass neue Feature des IO-Dies frei geschaltet werden, und so etwas wie ein X590, über den schon einmal spekuliert wurde erscheitn. Nur eben kein neues Design des IO-Chips. Hier wurden die deaktivierten Reserven mal thematisiert:

AMD-Zen-2-I/O-Chip unter dem Mikroskop: Die-Shots interpretiert

Nach den leistungsrelevanten I/O-Verbindungen vom CCD bis zum RAM spürt der zweite Teil unserer Ryzen-3000-I/O-Die-Shot-Analyse den externen Schnittstellen nach.

Also denke ich eher, dass diese Reserven AMD einen neuen Chip sparen, da auch keine bessere Plattform bieten kann.Und offensichtlich wurde auch die Kontrolllogik 1:1 von Epyc kopiert; das heißt: AM4-Zen-2-CPUs, X570 und TRX40 haben einen 32-Lane-PCI-Express-4.0-Controller! In den bislang verkauften Produkten sind diese offensichtlich teilweise deaktiviert und im AM4-Format lassen sie sich mangels Sockel-Kontakten auch nicht nach außen führen. Es spricht aber vieles dafür, dass AMD noch Reserven für besser ausgestattete I/O-Hub-Serien hätte, sobald man einen Bedarf für diese sieht. Wir erachten 28 Lanes (inklusive Uplink) für einen "X590" oder "TRX60" (oder "X690"?) als gut möglich; die letzten vier Serial-I/O-Links könnten im aktuell gefertigten Chip aber permanent mit SATA-Controllern verbunden sein (siehe unten).

Edit:

1. AMD plant möglicherweise einen Consumer IO-Chip ab AM5, der sich vom Server/TRX-Chipsatz unterscheidet. Das wäre eine sinnvolle Abgrenzung ab einer mittlerweile erreichten Größenordnung. Mir würde z.B. ein Weg gefallen eine APU als IO-Chip zu nutzen und ein 8-Core Chiplet anzubinden gefallen - das könnte auch der Weg sein in Zukunft allen AM5 Boards iGPU zu bescheren. Da wären IO-Chipsätze nur noch Server/Workstastion orientiert.

2. Und beim näheren darüber nachdenken erklären sich vielleicht die seltsame kleinen Unterschiede der APUs in der Roadmap - es kommt ein IF-Connect für ein Chiplet dran und fertig

Das wäre mal ein extrem eleganter Weg bis 16-Cores im Desktop.

Das wäre mal ein extrem eleganter Weg bis 16-Cores im Desktop.

Doppelposting wurde automatisch zusammengeführt:

Hier mal nach einer kurzen Recherche ob das passt, eine Theorie, gegen die ich bisher keine Anzeichen gefunden habe.

Wir kennen ja diese zusammen gestückelte Roadmap:

Hier ist es ja etwas rätselhaft warum bei Raphael Navi2 als iGPU mit gestrichelten Linien belegt ist, was als so etwas wie "optional" gedeutet werden könnte.

Was wenn AMD sich dachte, wir fertigen die APU in 6nm günstig und verwenden Sie dann als IO-Die für Raphael um 5nm Wafer zu sparen (es wird nur ein 5nm Chiplet benötigt für 16 Kerne). Das ganze dann bei 16-Core Desktop SKUs als Big-Little-Kerne organisiert, um Performance Unterschiede zu berücksichtigen, die aus der unterschiedlichen Fertigung entstehen. Rembrandt kann noch stärker auf Mobile optimiert werden, während das Raphael-Chiplet auch höhere Powerbudgets abrufen kann um höhere Taktraten zu erzielen. Rapahel kann zudem dann mit dem Server-IO-Die zu Threadripper und EPYC verbunden werden, ohne GPU oder mit CDNA GPU-Chiplets ausgestattet oder eben klassisch mit dGPUs zusammen in der Racks arbeiten.

Zuletzt bearbeitet:

Berniyh

Grand Admiral Special

- Mitglied seit

- 29.11.2005

- Beiträge

- 5.206

- Renomée

- 219

Ich denke die gestrichelten Linien heißen einfach, dass die Designphase des Chips noch nicht komplett abgeschlossen ist.

Wir wissen ja auch nicht genau von wann diese Folie ist. Mehrere Monate ist es auf jeden Fall alt. bzw. wissen wir auch noch überhaupt nicht, ob es wirklich von AMD selbst kommt und akkurat ist. Dafür spricht, dass bislang alles gepasst hat, z.B. bei Van Gogh und Cezanne.

Wir wissen ja auch nicht genau von wann diese Folie ist. Mehrere Monate ist es auf jeden Fall alt. bzw. wissen wir auch noch überhaupt nicht, ob es wirklich von AMD selbst kommt und akkurat ist. Dafür spricht, dass bislang alles gepasst hat, z.B. bei Van Gogh und Cezanne.

- Mitglied seit

- 16.10.2000

- Beiträge

- 24.371

- Renomée

- 9.696

- Standort

- East Fishkill, Minga, Xanten

- Aktuelle Projekte

- Je nach Gusto

- Meine Systeme

- Ryzen 9 5900X, Ryzen 7 3700X

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Samsung P35 (16 Jahre alt ;) )

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5900X

- Mainboard

- ASRock B550

- Speicher

- 2x 16 GB DDR4 3200

- Grafikprozessor

- GeForce GTX 1650

- Display

- 27 Zoll Acer + 24 Zoll DELL

- SSD

- Samsung 980 Pro 256 GB

- HDD

- diverse

- Soundkarte

- Onboard

- Gehäuse

- Fractal Design R5

- Netzteil

- be quiet! Straight Power 10 CM 500W

- Tastatur

- Logitech Cordless Desktop

- Maus

- Logitech G502

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox, Vivaldi

- Internetanbindung

- ▼250 MBit ▲40 MBit

Wir wissen ja auch nicht genau von wann diese Folie ist. Mehrere Monate ist es auf jeden Fall alt. bzw. wissen wir auch noch überhaupt nicht, ob es wirklich von AMD selbst kommt und akkurat ist. Dafür spricht, dass bislang alles gepasst hat, z.B. bei Van Gogh und Cezanne.

Gebe dir da Recht. Bislang steht noch aus, ob das wirklich echt ist. van Gogh und Cezanne waren als Codenammen schon bekannt.

Wenn das mit CVML bei van Gogh sich bestätigen sollte, dann haben wir nen starkes Indiz.

Berniyh

Grand Admiral Special

- Mitglied seit

- 29.11.2005

- Beiträge

- 5.206

- Renomée

- 219

Auch (LP-)DDR5 Unterstützung ist in meinen Augen schon ein gutes Indiz (das ist durch den Linux Treiber bestätigt).Wir wissen ja auch nicht genau von wann diese Folie ist. Mehrere Monate ist es auf jeden Fall alt. bzw. wissen wir auch noch überhaupt nicht, ob es wirklich von AMD selbst kommt und akkurat ist. Dafür spricht, dass bislang alles gepasst hat, z.B. bei Van Gogh und Cezanne.

Gebe dir da Recht. Bislang steht noch aus, ob das wirklich echt ist. van Gogh und Cezanne waren als Codenammen schon bekannt.

Wenn das mit CVML bei van Gogh sich bestätigen sollte, dann haben wir nen starkes Indiz.

Aber stimmt schon Zen2+RDNA2 bei Van Gogh und Zen3+Vega bei Cezanne war schon durch Komachi bekannt.

Auch Raphael mit angeblicher iGPU kam glaube ich von Komachi und ich meine Warhol war auch schon mal vorher irgendwo aufgetaucht.

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Dem stimme ich zu wenn du die um den ganzen Chip herum meinst. Ich meinte jedoch die gestrichelte Linie nur rund um das Feature "Nav..." in Raphael. Es ist unwahrscheinlich, dass die einzelnen Feature als "fertig oder nicht" gekennzeichnet sind. Und auch die Farbe ist grün anstatt rot wie bei Navi2. Es könnte auch auf Navi3-Chiplets hinweisen.Ich denke die gestrichelten Linien heißen einfach, dass die Designphase des Chips noch nicht komplett abgeschlossen ist.

Peet007

Admiral Special

- Mitglied seit

- 30.09.2006

- Beiträge

- 1.884

- Renomée

- 39

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 8700G

- Mainboard

- MSI Mortar B650

- Kühlung

- Wasser

- Speicher

- 32 GB

- Grafikprozessor

- IGP

- Display

- Philips

- Soundkarte

- onBoard

- Netzteil

- 850 Watt

- Betriebssystem

- Manjaro / Ubuntu

- Webbrowser

- Epiphany

Wenn AMD die nächsten Ryzen mit iGPU ausstattet dann sitzt sie bestimmt auf dem I/O direkt am Speicherkontroller. Für TR wäre das auch denkbar max. 8 CU nehmen nicht viel Platz weck.

Ich denke, beim IO-Die wird es auch mittelfristig darauf ankommen, welches Produktionsverfahren Globalfoundries anbieten kann. Als ehemalige AMD-Fab sollen sie ja immer noch per Verträge zur Abnahme von so und so viel GF-Dies bzw. Wafer verpflichtet sein. Nun hat sich AMD ja schon so weit rausgestolen, als dass sie GF-Dies nur noch für IO verwenden, wahrscheinlich, weil es im Vertrag nicht näher spezifiziert ist, was das Die eigentlich können muss. Im Extremfall könnten sie vermutlich auch ein deaktiviertes Die von GF drauflöten, Hauptsache sie nehmen eines je CPU ab wie vereinbartWas wenn AMD sich dachte, wir fertigen die APU in 6nm günstig und verwenden Sie dann als IO-Die für Raphael um 5nm Wafer zu sparen (es wird nur ein 5nm Chiplet benötigt für 16 Kerne).

Aber ohne den Trick wäre kein 7-nm-Ryzen möglich gewesen und solange der Vertrag noch läuft, sind sie auch an GF gebunden und in gewisser Weise davon abhängig, was GF halt im Sortiment hat als Produktionsverfahren. Bisher dürfte 12 nm ja immer noch das beste Verfahren sein, das GF auf Lager hat, oder?

Aber ohne den Trick wäre kein 7-nm-Ryzen möglich gewesen und solange der Vertrag noch läuft, sind sie auch an GF gebunden und in gewisser Weise davon abhängig, was GF halt im Sortiment hat als Produktionsverfahren. Bisher dürfte 12 nm ja immer noch das beste Verfahren sein, das GF auf Lager hat, oder?BavarianRealist

Grand Admiral Special

- Mitglied seit

- 06.02.2010

- Beiträge

- 3.358

- Renomée

- 80

Was mich etwas irritiert: dass die "Roadmap" für Anfang 2021 gleich drei verschiedene APUs zeigt: Cezanne, Van Gogh und auch noch Lucienne:

Es war nicht anders zu erwarten, weil bisher keine Laufzeiten von Tigerlake angegeben wurden: die Laufzeiten der ersten angekündigten Tiger-Lake-Notebooks sehen im Vergleich zu Renoir nicht gut aus:

Das Lenovo Thinkbook 14 G2 in identischer Ausführung:

4500U: 7,5h Laufzeit: https://geizhals.de/lenovo-thinkbook-14-g2-are-mineral-grey-20vf000age-a2389339.html?hloc=at&hloc=de

i5-1135G7: 6h Laufzeit: https://geizhals.de/lenovo-thinkbook-14-g2-itl-mineral-grey-20vd008wge-a2394694.html?hloc=at&hloc=de

Im Falle Acer 14" mit ähnlicher Ausstattung (wenn auch Swift gegen Travelmate) und gleichem Akku:

4700U: 11,5h Laufzeit: https://geizhals.de/acer-swift-3-sf...er-nx-hseeg-00n-a2334413.html?hloc=at&hloc=de

i7-1165G7: 8h Laufzeit: https://geizhals.de/acer-travelmate...rz-nx-vpkeg-003-a2394756.html?hloc=at&hloc=de

Doppelposting wurde automatisch zusammengeführt:

Es war nicht anders zu erwarten, weil bisher keine Laufzeiten von Tigerlake angegeben wurden: die Laufzeiten der ersten angekündigten Tiger-Lake-Notebooks sehen im Vergleich zu Renoir nicht gut aus:

Das Lenovo Thinkbook 14 G2 in identischer Ausführung:

4500U: 7,5h Laufzeit: https://geizhals.de/lenovo-thinkbook-14-g2-are-mineral-grey-20vf000age-a2389339.html?hloc=at&hloc=de

i5-1135G7: 6h Laufzeit: https://geizhals.de/lenovo-thinkbook-14-g2-itl-mineral-grey-20vd008wge-a2394694.html?hloc=at&hloc=de

Im Falle Acer 14" mit ähnlicher Ausstattung (wenn auch Swift gegen Travelmate) und gleichem Akku:

4700U: 11,5h Laufzeit: https://geizhals.de/acer-swift-3-sf...er-nx-hseeg-00n-a2334413.html?hloc=at&hloc=de

i7-1165G7: 8h Laufzeit: https://geizhals.de/acer-travelmate...rz-nx-vpkeg-003-a2394756.html?hloc=at&hloc=de

Zuletzt bearbeitet:

E555user

Admiral Special

- Mitglied seit

- 05.10.2015

- Beiträge

- 1.551

- Renomée

- 593

Wenn ich die Entwicklung richtig mitbekommen habe war AMD nur zur Abnahme im konkurrenzfähigen nm-Verfahren verpflichtet und da GF kein 7nm mehr anbieten wollte war man raus. Ich denke eigentlich, dass das Waver-Agreement kein Klotz am Bein mehr ist. Man nutzt GF noch so lange wie man damit auch nicht die Kapazität bei TSMC unnötig belastet, im Idealfall dauerhaft mit Chips die nicht diesen Fertigungsvorteil dringend benötigen....noch per Verträge zur Abnahme von so und so viel GF-Dies bzw. Wafer verpflichtet sein. Nun hat sich AMD ja schon so weit rausgestolen, als dass sie GF-Dies nur noch für IO verwenden, wahrscheinlich, weil es im Vertrag nicht näher spezifiziert ist, was das Die eigentlich können muss. Im Extremfall könnten sie vermutlich auch ein deaktiviertes Die von GF drauflöten, Hauptsache sie nehmen eines je CPU ab wie vereinbartAber ohne den Trick wäre kein 7-nm-Ryzen möglich gewesen...

Ach ja, hier... keine Verpflichtung für 7nm, Volumen in 12nm bis 2021, grundsätzliche Zusammenarbeit bis Q1/2024.

Meine Erklärung zu Van Gogh ist, dass es sich um ein Xbox-APU Pendant handelt. Wenn NAVI2 nur in einem anderen 7nm Verfahren vorlag sowie in diesem selben auch nur der Zen2 CCX, dann war es das schnellste diese Designs für eine APU ohne die Xbox-Anpassungen herauszubringen. Zusätzlich zu den üblichen Designs die noch ein weiteres Jahr an Vega7 festhalten. Dafür gibt es dann CVML.Was mich etwas irritiert: dass die "Roadmap" für Anfang 2021 gleich drei verschiedene APUs zeigt: Cezanne, Van Gogh und auch noch Lucienne:

ONH

Grand Admiral Special

Die farben des ramen um den Prozessor gibt wohl den Sockel an mit mehreren Ramen ist der Prozessor auf mehreren Sockel vorhanden hellgrün wird am4 sein, der orange ddr4 mobile, gelb ddr5/ddr4 mobile, blau rein ddr5 mobile, hellrosa ddr5 Desktop am5, rot chromebooks.

@pipin meiner Meinung nach hat ein redaktor auf twitter bestätigt, dass es eine Roadmap von AMD ist und die nicht gerade frisch ist, tweet bei rembrandt Ausschnitt durch @MebiuW.

@pipin meiner Meinung nach hat ein redaktor auf twitter bestätigt, dass es eine Roadmap von AMD ist und die nicht gerade frisch ist, tweet bei rembrandt Ausschnitt durch @MebiuW.

- Mitglied seit

- 16.10.2000

- Beiträge

- 24.371

- Renomée

- 9.696

- Standort

- East Fishkill, Minga, Xanten

- Aktuelle Projekte

- Je nach Gusto

- Meine Systeme

- Ryzen 9 5900X, Ryzen 7 3700X

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Samsung P35 (16 Jahre alt ;) )

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5900X

- Mainboard

- ASRock B550

- Speicher

- 2x 16 GB DDR4 3200

- Grafikprozessor

- GeForce GTX 1650

- Display

- 27 Zoll Acer + 24 Zoll DELL

- SSD

- Samsung 980 Pro 256 GB

- HDD

- diverse

- Soundkarte

- Onboard

- Gehäuse

- Fractal Design R5

- Netzteil

- be quiet! Straight Power 10 CM 500W

- Tastatur

- Logitech Cordless Desktop

- Maus

- Logitech G502

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox, Vivaldi

- Internetanbindung

- ▼250 MBit ▲40 MBit

Was mich etwas irritiert: dass die "Roadmap" für Anfang 2021 gleich drei verschiedene APUs zeigt: Cezanne, Van Gogh und auch noch Lucienne:

Die hab ich in meiner Roadmap genauso drin. Nur hatte ich van Gogh lange für 2020 stehen

van Gogh hat ja noch ne Lite Version. Aber viele vermuten, dass die CPUs für Ultra-Mobiles sind.

Ich nehme Lucienne immer noch als günstigen Dali-Nachfolger an. Die letzten Gerüchte sprechen aber davon, dass es auch Ryzen 5000er werden zusammen mit Cezanne. Das will ich aber vor allem gedanklich nicht akzeptieren, weil dann AMD wieder Architekturen mischen würde und die noch nicht mal durch Trennung in Ryzen und Athlon. Macht für mich immer noch irgendwie keinen Sinn. Aber mal sehen.

Berniyh

Grand Admiral Special

- Mitglied seit

- 29.11.2005

- Beiträge

- 5.206

- Renomée

- 219

Ah so, das meinst du. Ja, das könnte man so sehen wie du es beschrieben hast, aber es könnte auch etwas anderes bedeuten.Dem stimme ich zu wenn du die um den ganzen Chip herum meinst. Ich meinte jedoch die gestrichelte Linie nur rund um das Feature "Nav..." in Raphael. Es ist unwahrscheinlich, dass die einzelnen Feature als "fertig oder nicht" gekennzeichnet sind. Und auch die Farbe ist grün anstatt rot wie bei Navi2. Es könnte auch auf Navi3-Chiplets hinweisen.Ich denke die gestrichelten Linien heißen einfach, dass die Designphase des Chips noch nicht komplett abgeschlossen ist.

Evtl. war einfach noch nicht sicher, ob man das auch wirklich umsetzt.

Doppelposting wurde automatisch zusammengeführt:

Das ist halt das was mich daran stört: da stecken unglaublich viele Details drinnen.Die farben des ramen um den Prozessor gibt wohl den Sockel an mit mehreren Ramen ist der Prozessor auf mehreren Sockel vorhanden hellgrün wird am4 sein, der orange ddr4 mobile, gelb ddr5/ddr4 mobile, blau rein ddr5 mobile, hellrosa ddr5 Desktop am5, rot chromebooks.

Wenn, dann wäre das nur eine Roadmap die AMD ausschließlich intern verwendet und dann wäre das schon arg komisch, dass das nach außen gelangt.

s.o.: warum sollte ein Redakteur eine solche Roadmap von AMD zu sehen bekommen?@pipin meiner Meinung nach hat ein redaktor auf twitter bestätigt, dass es eine Roadmap von AMD ist und die nicht gerade frisch ist, tweet bei rembrandt Ausschnitt durch @MebiuW.

Meiner Meinung nach könnte nur AMD bestätigen (oder widerlegen), dass diese Roadmap stimmt, aber die würden das natürlich nie machen.

Navi 10 Lite und Navi 21 Lite hat man in der Form auch nicht als Produkt gesehen. Wahrscheinlich sind das wie van Gogh irgendwelche Prototypen.Die hab ich in meiner Roadmap genauso drin. Nur hatte ich van Gogh lange für 2020 stehen

van Gogh hat ja noch ne Lite Version. Aber viele vermuten, dass die CPUs für Ultra-Mobiles sind.

Ok, Navi 21 Lite war wohl die Vorlage zur XBox (vermutlich aber ohne CPU Cores).

Bei van Gogh Lite spricht auch die GPU ID 10.4.x dafür, die vermutlich kein anderer Chip haben wird. Genauso wie bei Navi 21 Lite (10.2.x).

RDNA3 ist dann ja schon 11.0.x.

Zuletzt bearbeitet:

BavarianRealist

Grand Admiral Special

- Mitglied seit

- 06.02.2010

- Beiträge

- 3.358

- Renomée

- 80

Lucienne könnte eine Long-Live- Lowend- Lowpower-Version von Renoir sein, wie Dali etc. davor. Also ein gestutzter Renoir, z.B. 4Core und nur 4Cu mit <90mm² für industrielle Anwendungen sowie Lowend- und Lowpower-Notebooks, weil billig.

- Mitglied seit

- 16.10.2000

- Beiträge

- 24.371

- Renomée

- 9.696

- Standort

- East Fishkill, Minga, Xanten

- Aktuelle Projekte

- Je nach Gusto

- Meine Systeme

- Ryzen 9 5900X, Ryzen 7 3700X

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Samsung P35 (16 Jahre alt ;) )

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5900X

- Mainboard

- ASRock B550

- Speicher

- 2x 16 GB DDR4 3200

- Grafikprozessor

- GeForce GTX 1650

- Display

- 27 Zoll Acer + 24 Zoll DELL

- SSD

- Samsung 980 Pro 256 GB

- HDD

- diverse

- Soundkarte

- Onboard

- Gehäuse

- Fractal Design R5

- Netzteil

- be quiet! Straight Power 10 CM 500W

- Tastatur

- Logitech Cordless Desktop

- Maus

- Logitech G502

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox, Vivaldi

- Internetanbindung

- ▼250 MBit ▲40 MBit

Infos zum Die-Size von Rembrandt.

Ist aber sehr früh, der sollte seinen Tape-Out noch gar nicht haben.

Ist aber sehr früh, der sollte seinen Tape-Out noch gar nicht haben.

BavarianRealist

Grand Admiral Special

- Mitglied seit

- 06.02.2010

- Beiträge

- 3.358

- Renomée

- 80

Infos zum Die-Size von Rembrandt.

Ist aber sehr früh, der sollte seinen Tape-Out noch gar nicht haben.

Ein paar Tage vorher hatte Patrick Schur folgende Info, nach der Zen3+ ein Refresh in 6nm ("6nm" ist auch ein 7nm-Prozess, aber mit mehr EUV und angeblich "kompatibel" zu N7 und N7P, was für N7+ angeblich nicht gilt):

Berniyh

Grand Admiral Special

- Mitglied seit

- 29.11.2005

- Beiträge

- 5.206

- Renomée

- 219

Es gibt schon FW Dateien zu Rembrandt, also wird der vermutlich schon seinen Tape-Out gehabt haben.Infos zum Die-Size von Rembrandt.

Ist aber sehr früh, der sollte seinen Tape-Out noch gar nicht haben.

Ähnliche Themen

- Antworten

- 439

- Aufrufe

- 38K

- Antworten

- 31

- Aufrufe

- 2K

- Antworten

- 2

- Aufrufe

- 821

- Antworten

- 3

- Aufrufe

- 3K