App installieren

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: This feature may not be available in some browsers.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

AMD - Zen 3 - 7 nm / 6 nm - Vermeer, Cezanne, Warhol, Rembrandt, Dragon Point

- Ersteller Tu334

- Erstellt am

eratte

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 11.11.2001

- Beiträge

- 21.837

- Renomée

- 2.807

- Standort

- Rheinberg / NRW

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- YoYo, Collatz

- Lieblingsprojekt

- YoYo

- Meine Systeme

- Wegen der aktuellen Lage alles aus.

- BOINC-Statistiken

- Mein Laptop

- Lenovo ThinkPad E15 Gen4 Intel / HP PAVILION 14-dk0002ng

- Details zu meinem Desktop

- Prozessor

- Ryzen R9 7950X

- Mainboard

- ASUS ROG Crosshair X670E Hero

- Kühlung

- Noctua NH-D15

- Speicher

- 2 x 32 GB G.Skill Trident Z DDR5 6000 CL30-40-40-96

- Grafikprozessor

- Sapphire Radeon RX7900XTX Gaming OC Nitro+

- Display

- 2 x ASUS XG27AQ (2560x1440@144 Hz)

- SSD

- Samsung 980 Pro 1 TB & Lexar NM790 4 TB

- Optisches Laufwerk

- USB Blu-Ray Brenner

- Soundkarte

- Onboard

- Gehäuse

- NEXT H7 Flow Schwarz

- Netzteil

- Corsair HX1000 (80+ Platinum)

- Tastatur

- ASUS ROG Strix Scope RX TKL Wireless / 2. Rechner&Server Cherry G80-3000N RGB TKL

- Maus

- ROG Gladius III Wireless / 2. Rechner&Server Sharkoon Light2 180

- Betriebssystem

- Windows 11 Pro 64

- Webbrowser

- Firefox

- Verschiedenes

- 4 x BQ Light Wings 14. 1 x NF-A14 Noctua Lüfter. Corsair HS80 Headset .

- Internetanbindung

- ▼VDSL 100 ▲VDSL 100

Ja das macht ja gerade die Runde mit IF 2000 und DDR4 4000

PS.: WCCFtech ist meist wie immer nicht die Orginalquelle.

PS.: WCCFtech ist meist wie immer nicht die Orginalquelle.

- Mitglied seit

- 16.10.2000

- Beiträge

- 24.368

- Renomée

- 9.694

- Standort

- East Fishkill, Minga, Xanten

- Aktuelle Projekte

- Je nach Gusto

- Meine Systeme

- Ryzen 9 5900X, Ryzen 7 3700X

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Samsung P35 (16 Jahre alt ;) )

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5900X

- Mainboard

- ASRock B550

- Speicher

- 2x 16 GB DDR4 3200

- Grafikprozessor

- GeForce GTX 1650

- Display

- 27 Zoll Acer + 24 Zoll DELL

- SSD

- Samsung 980 Pro 256 GB

- HDD

- diverse

- Soundkarte

- Onboard

- Gehäuse

- Fractal Design R5

- Netzteil

- be quiet! Straight Power 10 CM 500W

- Tastatur

- Logitech Cordless Desktop

- Maus

- Logitech G502

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox, Vivaldi

- Internetanbindung

- ▼250 MBit ▲40 MBit

PS.: WCCFtech ist meist wie immer nicht die Orginalquelle.

Hier kommts her:

Ryzen 5000, DDR4-4000 MHz Bellek DesteÄi Sunuyor

AMD, Zen 3 iÅlemcilerindeki mimari deÄiÅikliklerin yanı sıra bellek kanadında da iyileÅtirmeler yaptı. AMD'nin baÅtan aÅaÄı yenilediÄi Zen 3 mikro

bschicht86

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 14.12.2006

- Beiträge

- 4.249

- Renomée

- 228

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- 2950X

- Mainboard

- X399 Taichi

- Kühlung

- Heatkiller IV Pure Chopper

- Speicher

- 64GB 3466 CL16

- Grafikprozessor

- 2x Vega 64 @Heatkiller

- Display

- Asus VG248QE

- SSD

- PM981, SM951, ein paar MX500 (~5,3TB)

- HDD

- -

- Optisches Laufwerk

- 1x BH16NS55 mit UHD-BD-Mod

- Soundkarte

- Audigy X-Fi Titanium Fatal1ty Pro

- Gehäuse

- Chieftec

- Netzteil

- Antec HCP-850 Platinum

- Betriebssystem

- Win7 x64, Win10 x64

- Webbrowser

- Firefox

- Verschiedenes

- LS120 mit umgebastelten USB -> IDE (Format wie die gängigen SATA -> IDE)

Nach viel klingts aber nicht, wenn schon Zen2 gut bis 1800 kam. Würd aber auch dafür sprechen, dass der IOD kaum verbessert wurde.

Pinnacle Ridge

Vice Admiral Special

- Mitglied seit

- 04.03.2017

- Beiträge

- 528

- Renomée

- 7

Und danach limitiert wohl die IOD, weil bei Matisse geht ja auch fast so viel.Zen3 soll einen IF und DDR4 Clck 1:1 von 2GHz also DDR4 4000 bei guten Samples erlauben.

E555user

Admiral Special

- Mitglied seit

- 05.10.2015

- Beiträge

- 1.551

- Renomée

- 593

Ich denke nicht, dass der I/O Die das Limit setzt, dies wurde im FCLK stets zuerst erreicht, also dem Infinity Fabric Takt zwischen dem I/O Die und den Chiplets, sowie zwischen den CCX auf einem Chiplet. Da nun die CCX-Vermittlung weg fällt könnte das Konstrukt schon wieder etwas höher takten. Vermutlich sind aber die Hauptursachen in der Qualität der IF-Links via dem Interposer zu suchen.

Soweit ich das verfolgt habe ging es bei Zen nicht wirklich darum die Bandbreiten zu erhöhen, sondern vor allem darum die Latenzen zu verringern. Beides geht beim Takt Hand in Hand. Mehr Takt beim RAM allein reduziert aber die Latenzen zum Chiplet kaum mehr.

Soweit ich das verfolgt habe ging es bei Zen nicht wirklich darum die Bandbreiten zu erhöhen, sondern vor allem darum die Latenzen zu verringern. Beides geht beim Takt Hand in Hand. Mehr Takt beim RAM allein reduziert aber die Latenzen zum Chiplet kaum mehr.

eratte

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 11.11.2001

- Beiträge

- 21.837

- Renomée

- 2.807

- Standort

- Rheinberg / NRW

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- YoYo, Collatz

- Lieblingsprojekt

- YoYo

- Meine Systeme

- Wegen der aktuellen Lage alles aus.

- BOINC-Statistiken

- Mein Laptop

- Lenovo ThinkPad E15 Gen4 Intel / HP PAVILION 14-dk0002ng

- Details zu meinem Desktop

- Prozessor

- Ryzen R9 7950X

- Mainboard

- ASUS ROG Crosshair X670E Hero

- Kühlung

- Noctua NH-D15

- Speicher

- 2 x 32 GB G.Skill Trident Z DDR5 6000 CL30-40-40-96

- Grafikprozessor

- Sapphire Radeon RX7900XTX Gaming OC Nitro+

- Display

- 2 x ASUS XG27AQ (2560x1440@144 Hz)

- SSD

- Samsung 980 Pro 1 TB & Lexar NM790 4 TB

- Optisches Laufwerk

- USB Blu-Ray Brenner

- Soundkarte

- Onboard

- Gehäuse

- NEXT H7 Flow Schwarz

- Netzteil

- Corsair HX1000 (80+ Platinum)

- Tastatur

- ASUS ROG Strix Scope RX TKL Wireless / 2. Rechner&Server Cherry G80-3000N RGB TKL

- Maus

- ROG Gladius III Wireless / 2. Rechner&Server Sharkoon Light2 180

- Betriebssystem

- Windows 11 Pro 64

- Webbrowser

- Firefox

- Verschiedenes

- 4 x BQ Light Wings 14. 1 x NF-A14 Noctua Lüfter. Corsair HS80 Headset .

- Internetanbindung

- ▼VDSL 100 ▲VDSL 100

E555user

Admiral Special

- Mitglied seit

- 05.10.2015

- Beiträge

- 1.551

- Renomée

- 593

Papermaster schafft es doch tatsächlich mit so viel Worten so wenig handfestes zu sagen, also fast nichts.

Ich habe jetzt nur mitgenommen, dass der PHY und Elemente für Off-Chip Kommunikation am Rande des Chiplets verbesserte Latenzen ermöglicht, bei Position zwischen den CCX in der Mitte des Die hat man da längere Strecken zu Lasten der Latenz gehabt. Zu mehr konkreten Informationen soll man auf weitere Veröffentlichungen warten.

Ich habe jetzt nur mitgenommen, dass der PHY und Elemente für Off-Chip Kommunikation am Rande des Chiplets verbesserte Latenzen ermöglicht, bei Position zwischen den CCX in der Mitte des Die hat man da längere Strecken zu Lasten der Latenz gehabt. Zu mehr konkreten Informationen soll man auf weitere Veröffentlichungen warten.

- Mitglied seit

- 16.10.2000

- Beiträge

- 24.368

- Renomée

- 9.694

- Standort

- East Fishkill, Minga, Xanten

- Aktuelle Projekte

- Je nach Gusto

- Meine Systeme

- Ryzen 9 5900X, Ryzen 7 3700X

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Samsung P35 (16 Jahre alt ;) )

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5900X

- Mainboard

- ASRock B550

- Speicher

- 2x 16 GB DDR4 3200

- Grafikprozessor

- GeForce GTX 1650

- Display

- 27 Zoll Acer + 24 Zoll DELL

- SSD

- Samsung 980 Pro 256 GB

- HDD

- diverse

- Soundkarte

- Onboard

- Gehäuse

- Fractal Design R5

- Netzteil

- be quiet! Straight Power 10 CM 500W

- Tastatur

- Logitech Cordless Desktop

- Maus

- Logitech G502

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox, Vivaldi

- Internetanbindung

- ▼250 MBit ▲40 MBit

Papermaster schafft es doch tatsächlich mit so viel Worten so wenig handfestes zu sagen, also fast nichts.

Endlich jemand, der das genauso sieht. Überall wird das tolle und informative Interview gelobt. Natürlich sind die Fragen gut, aber wirklich erhellend - im Sinne von Details - empfinde ich es nicht. Die werden über Zen 3 auch nicht mehr sagen, bis die Epycs vorgestellt werden.

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Also ich seh das ebenso. Nix neues und die Hälfte der Antworten bezieht sich nicht mal auf die Frage.

eratte

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 11.11.2001

- Beiträge

- 21.837

- Renomée

- 2.807

- Standort

- Rheinberg / NRW

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- YoYo, Collatz

- Lieblingsprojekt

- YoYo

- Meine Systeme

- Wegen der aktuellen Lage alles aus.

- BOINC-Statistiken

- Mein Laptop

- Lenovo ThinkPad E15 Gen4 Intel / HP PAVILION 14-dk0002ng

- Details zu meinem Desktop

- Prozessor

- Ryzen R9 7950X

- Mainboard

- ASUS ROG Crosshair X670E Hero

- Kühlung

- Noctua NH-D15

- Speicher

- 2 x 32 GB G.Skill Trident Z DDR5 6000 CL30-40-40-96

- Grafikprozessor

- Sapphire Radeon RX7900XTX Gaming OC Nitro+

- Display

- 2 x ASUS XG27AQ (2560x1440@144 Hz)

- SSD

- Samsung 980 Pro 1 TB & Lexar NM790 4 TB

- Optisches Laufwerk

- USB Blu-Ray Brenner

- Soundkarte

- Onboard

- Gehäuse

- NEXT H7 Flow Schwarz

- Netzteil

- Corsair HX1000 (80+ Platinum)

- Tastatur

- ASUS ROG Strix Scope RX TKL Wireless / 2. Rechner&Server Cherry G80-3000N RGB TKL

- Maus

- ROG Gladius III Wireless / 2. Rechner&Server Sharkoon Light2 180

- Betriebssystem

- Windows 11 Pro 64

- Webbrowser

- Firefox

- Verschiedenes

- 4 x BQ Light Wings 14. 1 x NF-A14 Noctua Lüfter. Corsair HS80 Headset .

- Internetanbindung

- ▼VDSL 100 ▲VDSL 100

Ich frage mich was ihr da erwartet habt, da stehen ja noch einige Veranstaltungen aus da hätte es mich gewundert wenn in dem Interview viel offen gelegt wäre.

- Mitglied seit

- 16.10.2000

- Beiträge

- 24.368

- Renomée

- 9.694

- Standort

- East Fishkill, Minga, Xanten

- Aktuelle Projekte

- Je nach Gusto

- Meine Systeme

- Ryzen 9 5900X, Ryzen 7 3700X

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Samsung P35 (16 Jahre alt ;) )

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5900X

- Mainboard

- ASRock B550

- Speicher

- 2x 16 GB DDR4 3200

- Grafikprozessor

- GeForce GTX 1650

- Display

- 27 Zoll Acer + 24 Zoll DELL

- SSD

- Samsung 980 Pro 256 GB

- HDD

- diverse

- Soundkarte

- Onboard

- Gehäuse

- Fractal Design R5

- Netzteil

- be quiet! Straight Power 10 CM 500W

- Tastatur

- Logitech Cordless Desktop

- Maus

- Logitech G502

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox, Vivaldi

- Internetanbindung

- ▼250 MBit ▲40 MBit

Ich frage mich was ihr da erwartet habt, da stehen ja noch einige Veranstaltungen aus da hätte es mich gewundert wenn in dem Interview viel offen gelegt wäre.

Eigentlich nichts, aber kleine Hints wären nett gewesen. Wobei ich gerade das Video zum Interview gesehen habe und das war eigentlich besser, klar weil Bild plus Inhalt mehr transportiert.

Und AMD hat es ja bereits dröfmal gesagt, sie lassen halt nichts weltbewegendes raus, weil sie größere Sachen halt entsprechenden publik machen müssen.

Es wird aber wohl doch mehr technische Einzelheiten zum Launch am 5. geben.

Ich werde mal versuchen die entsprechenden Infos zu besorgen, damit unsere CPU-Gurus das eventuell zum 5. passend etwas aufdröseln können.

Wir haben allerdings offiziell bislang noch gar nicht die Infos vom 8. bekommen, deswegen ist das leider sehr unwahrscheinlich.

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Nichts anderes. In dieser Phase von Produktlaunches wird offiziell nichts neues in Interviews genannt. Ich bin nur verwundert was manche da Neues raus lesen.Ich frage mich was ihr da erwartet habt, da stehen ja noch einige Veranstaltungen aus da hätte es mich gewundert wenn in dem Interview viel offen gelegt wäre.

Zielgruppe sind eindeutig Investoren.

MagicEye04

Grand Admiral Special

- Mitglied seit

- 20.03.2006

- Beiträge

- 23.258

- Renomée

- 1.842

- Standort

- oops,wrong.planet..

- Aktuelle Projekte

- Seti,WCG,Einstein + was gerade Hilfe braucht

- Lieblingsprojekt

- Seti

- Meine Systeme

- R7-1700+GTX1070ti,R7-1700+RadeonVII, FX-8350+GTX1050ti, X4-5350+GT1030, X2-240e+RX460

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Dell Latitude E7240

- Details zu meinem Desktop

- Prozessor

- R9-3950X (@65W)

- Mainboard

- Asus Prime B550plus

- Kühlung

- TR Macho

- Speicher

- 2x16GiB Corsair LPX2666C16

- Grafikprozessor

- Radeon VII

- Display

- LG 32UD99-W 81,3cm

- SSD

- Crucial MX500-250GB, Samsung EVO280 256GB

- HDD

- Seagate 7200.14 2TB (per eSATAp)

- Optisches Laufwerk

- LG DVDRAM GH24NS90

- Soundkarte

- onboard

- Gehäuse

- Nanoxia Deep Silence1

- Netzteil

- BeQuiet StraightPower 11 550W

- Tastatur

- Cherry RS6000

- Maus

- Logitech RX600

- Betriebssystem

- Ubuntu

- Webbrowser

- Feuerfuchs

- Verschiedenes

- 4x Nanoxia Lüfter (120/140mm) , Festplatte in Bitumenbox

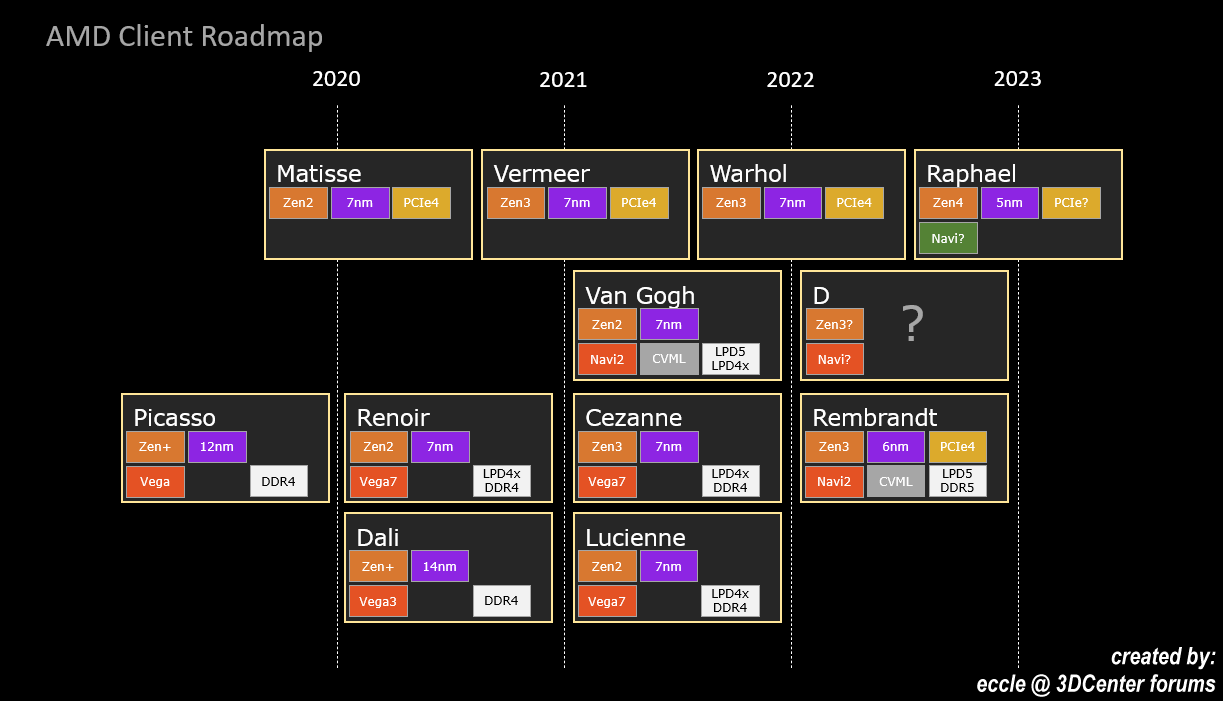

Gibt es eigentlich irgendwo eine Galerie, wo die ganzen Maler mal übersichtlich hängen?

Mit der Flut an Namen hat mich AMD irgendwie komplett abgehängt.

Mit der Flut an Namen hat mich AMD irgendwie komplett abgehängt.

Berniyh

Grand Admiral Special

- Mitglied seit

- 29.11.2005

- Beiträge

- 5.206

- Renomée

- 218

Da hast du deine Galerie:Gibt es eigentlich irgendwo eine Galerie, wo die ganzen Maler mal übersichtlich hängen?

Mit der Flut an Namen hat mich AMD irgendwie komplett abgehängt.

MusicIsMyLife

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 22.02.2002

- Beiträge

- 15.579

- Renomée

- 2.567

- Standort

- in der Nähe von Cottbus

- Lieblingsprojekt

- Asteroids@Home

- Meine Systeme

- Alltags-PC, Test-PC (wechselnde Hardware)

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Desktopsystem

- Alltags-PC

- Mein Laptop

- HP DV7-2225sg

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 7950X

- Mainboard

- ASRock B650M PG Riptide

- Kühlung

- Watercool Heatkiller IV Pro Copper

- Speicher

- 2x 32 GB G.Skill TridentZ 5 TGB (F5-6000J3040G32X2-TZ5RS)

- Grafikprozessor

- AMD Radeon RX 6900XT

- Display

- ASUS ROG PG42UQ (3840x2160), Philips BDM4065UC (3840x2160), Samsung C27HG70 (2560x1440)

- SSD

- Micron 9300 Pro 7,68 TB (U.2), Samsung 850 Evo 4 TB (SATA)

- HDD

- keine, SSD only...

- Optisches Laufwerk

- LG CH08LS10 Blu-ray Disc-Player

- Soundkarte

- Creative SoundBlasterX AE-5 Plus

- Gehäuse

- Dimastech BenchTable EasyXL (vorübergehend)

- Netzteil

- Corsair RM850i

- Tastatur

- ASUS ROG Strix Flare

- Maus

- Steelseries Sensei 310

- Betriebssystem

- Windows 10 Professional

- Webbrowser

- Firefox

- Schau Dir das System auf sysprofile.de an

- Internetanbindung

- ▼250 MBit ▲45 MBit

Was mir zu diesem Bild hier gestern noch durch den Kopf gegangen ist:

Hier wurde ja die Gaming-Leistung in 1080p von 5900X und 10900K verglichen. Mit dem - im Durchschnitt - besseren Ende für den 5900X. Dabei ist der 5900X ja wieder ein 12-Kerner, der noch immer mit dem "Problem" der zwei Chiplets zu kämpfen hat. Also zusätzliche Latenz durch die Inter-Chiplet-Kommunikation.

Beim 5800X mit nur einem 8-Kern-Chiplet als einzel-CCX müsste es theoretisch ja noch einmal einen ordentlichen Boost geben, da das Thema IF-Kommunikation in dieser Konfiguration komplett wegfällt.

Stapelt AMD hiermit also vielleicht auch bewusst tief?

Falls das schon irgendjemand zur Sprache gebracht hat - mea culpa. Ich hab das Thema hier nicht genau verfolgt.

Hier wurde ja die Gaming-Leistung in 1080p von 5900X und 10900K verglichen. Mit dem - im Durchschnitt - besseren Ende für den 5900X. Dabei ist der 5900X ja wieder ein 12-Kerner, der noch immer mit dem "Problem" der zwei Chiplets zu kämpfen hat. Also zusätzliche Latenz durch die Inter-Chiplet-Kommunikation.

Beim 5800X mit nur einem 8-Kern-Chiplet als einzel-CCX müsste es theoretisch ja noch einmal einen ordentlichen Boost geben, da das Thema IF-Kommunikation in dieser Konfiguration komplett wegfällt.

Stapelt AMD hiermit also vielleicht auch bewusst tief?

Falls das schon irgendjemand zur Sprache gebracht hat - mea culpa. Ich hab das Thema hier nicht genau verfolgt.

E555user

Admiral Special

- Mitglied seit

- 05.10.2015

- Beiträge

- 1.551

- Renomée

- 593

Stapelt AMD hiermit also vielleicht auch bewusst tief?

Ich glaube nicht, dass das noch etwas mit den Inter-Chiplet Latenzen ausmacht. Der 5900X darf mindestens auf dem besseren Chiplet höher Takten, ich hätte gedacht der Windows-Scheduler gruppiert mittlerweile zusammengehörige Threads auf dem gleichen Chiplet. Im Zweifel wird die Latenz zwischen den Chiplets gering genug sein um nicht zu grosse Einbrüche zu verursachen. Ich erwarte da nur marginale Differenzen mit Vorteilen bei mehr Kernen für Background-Tasks so dass auch der Cache im Chiplet "frei" bleibt.

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Die Verbesserung kommt schon daher, dass eben nicht mehr Of-Chip kommuniziert wird sobald außerhalb eines 4-Kern-CCX zugegriffen werden muss. Der 8-Kern-CCX wird möglicherweise auch intelligenter ausgelastet bei Spielen, dass die weiteren 4 Kerne auf dem anderen Die kaum angesprochen werden müssen. Das verhält sich dann schon fast wie ein einzelner 8-Kern-Die, der noch 4 Kerne in Reserve hat

Mente

Grand Admiral Special

- Mitglied seit

- 23.05.2009

- Beiträge

- 3.671

- Renomée

- 135

- Aktuelle Projekte

- constalation astroids yoyo

- Lieblingsprojekt

- yoyo doking

- Meine Systeme

- Ryzen 3950x

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- AMD 5800X3D

- Mainboard

- Asus ROG Crosshair VIII Dark Hero

- Kühlung

- Headkiller IV

- Speicher

- 3800CL14 G.Skill Trident Z silber/rot DIMM Kit 32GB, DDR4-3600, CL15-15-15-35 (F4-3600C15D-16GTZ)

- Grafikprozessor

- AMD Radeon RX 6900 XT Ref. @Alphacool

- Display

- MSI Optix MAG27CQ

- SSD

- SN8502TB,MX5001TB,Vector150 480gb,Vector 180 256gb,Sandisk extreme 240gb,RD400 512gb

- HDD

- n/a

- Optisches Laufwerk

- n/a

- Soundkarte

- Soundblaster X4

- Gehäuse

- Phanteks Enthoo Pro 2 Tempered Glass

- Netzteil

- Seasonic Prime GX-850 850W

- Tastatur

- Logitech G19

- Maus

- Logitech G703

- Betriebssystem

- Win 10 pro

- Webbrowser

- IE 11 Mozilla Opera

- Verschiedenes

- Logitech PRO RENNLENKRAD DD

Hi

derzeit ist es ja auch schon so das das Game unter einer gewissen Grenze auf einem CCX bleibt könnt ihr schön sehen im Monitoring, daher ist es nur bei bestimmten Games die mind. 6+ Kerne Ansprechen ein Einfluss der Latenzen zu erwarten, aber schon bei den 3000´er war der 3900x im schnitt schneller wie der 3800x.

lg

derzeit ist es ja auch schon so das das Game unter einer gewissen Grenze auf einem CCX bleibt könnt ihr schön sehen im Monitoring, daher ist es nur bei bestimmten Games die mind. 6+ Kerne Ansprechen ein Einfluss der Latenzen zu erwarten, aber schon bei den 3000´er war der 3900x im schnitt schneller wie der 3800x.

lg

Berniyh

Grand Admiral Special

- Mitglied seit

- 29.11.2005

- Beiträge

- 5.206

- Renomée

- 218

Das ist aber nur ein Teil. Gerade bei Games dürfte wesentlich ausschlaggebend sein, dass sich für Programme mit <=4 Threads der L3 Cache effektiv verdoppelt hat, da nun alle Kerne in einem CCD auf den kompletten CCD L3 Cache zugreifen können.Die Verbesserung kommt schon daher, dass eben nicht mehr Of-Chip kommuniziert wird sobald außerhalb eines 4-Kern-CCX zugegriffen werden muss. Der 8-Kern-CCX wird möglicherweise auch intelligenter ausgelastet bei Spielen, dass die weiteren 4 Kerne auf dem anderen Die kaum angesprochen werden müssen. Das verhält sich dann schon fast wie ein einzelner 8-Kern-Die, der noch 4 Kerne in Reserve hat

AMD-APUs Cezanne und Lucienne gemischt in einer Serie? - Planet 3DNow!

Auf Planet 3DNow! gibt es alle wichtigen Informationen fr AMD-User: News, Downloads, Support, Tests

www.planet3dnow.de

Mente

Grand Admiral Special

- Mitglied seit

- 23.05.2009

- Beiträge

- 3.671

- Renomée

- 135

- Aktuelle Projekte

- constalation astroids yoyo

- Lieblingsprojekt

- yoyo doking

- Meine Systeme

- Ryzen 3950x

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- AMD 5800X3D

- Mainboard

- Asus ROG Crosshair VIII Dark Hero

- Kühlung

- Headkiller IV

- Speicher

- 3800CL14 G.Skill Trident Z silber/rot DIMM Kit 32GB, DDR4-3600, CL15-15-15-35 (F4-3600C15D-16GTZ)

- Grafikprozessor

- AMD Radeon RX 6900 XT Ref. @Alphacool

- Display

- MSI Optix MAG27CQ

- SSD

- SN8502TB,MX5001TB,Vector150 480gb,Vector 180 256gb,Sandisk extreme 240gb,RD400 512gb

- HDD

- n/a

- Optisches Laufwerk

- n/a

- Soundkarte

- Soundblaster X4

- Gehäuse

- Phanteks Enthoo Pro 2 Tempered Glass

- Netzteil

- Seasonic Prime GX-850 850W

- Tastatur

- Logitech G19

- Maus

- Logitech G703

- Betriebssystem

- Win 10 pro

- Webbrowser

- IE 11 Mozilla Opera

- Verschiedenes

- Logitech PRO RENNLENKRAD DD

Hallo zusammen,

was zum schmunzeln am Freitag da baut man den Bench schon auf blau um und dann sowas

www.computerbase.de

lg

www.computerbase.de

lg

was zum schmunzeln am Freitag da baut man den Bench schon auf blau um und dann sowas

AMD Ryzen 5 5600X: Kleinste Zen-3-CPU erobert Platz 1 im PassMark

Am 5. November startet die Ryzen-5000-Serie mit vorerst vier Zen-3-CPUs. Die kleinste, der Ryzen 5 5600X, erobert Platz 1 im PassMark.

erde-m

Grand Admiral Special

- Mitglied seit

- 23.03.2002

- Beiträge

- 3.271

- Renomée

- 450

- Standort

- TF

- Mitglied der Planet 3DNow! Kavallerie!

- Lieblingsprojekt

- LHC

- Meine Systeme

- AMD Ryzen9 5950X+64 GB DDR3600+RX6900XT, AMD Epyc 7V12+256 GB ECC DDR3200+R VII, AMD Ryzen 5 2500U

- BOINC-Statistiken

- Mein Laptop

- HP Envy x360 15-bq102ng Ryzen 5 2500U

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen9 5950X

- Mainboard

- Asus Prime X470-Pro

- Kühlung

- be quiet Silent Loop 280mm

- Speicher

- 64GB (4x16GB) G.Skill TridentZ Neo F4-3600C16-64GTZNC Quad Kit

- Grafikprozessor

- AMD Radeon RX 6900XT

- Display

- Acer Pro Designer PE320QK

- SSD

- M2: 2x Samsung 970Evo Plus 1TB

- HDD

- WDC WD100EFAX

- Soundkarte

- Onboard

- Gehäuse

- Fractal Define 7 Clear Tempered Glass White

- Netzteil

- bequiet Dark Power 12 1000W

- Tastatur

- Logitech G815

- Maus

- Logitech G402

- Betriebssystem

- Linux Mint 21.2; Win10Pro-64Bit

- Webbrowser

- Firefox

- Verschiedenes

- Qnap Single-port Aquantia AQC107 10GbE

- Internetanbindung

- ▼225 MBit ▲45 MBit

Das Leben ist eine Pendeltür, manchmal schlägt es auch zurückHallo zusammen,

was zum schmunzeln am Freitag da baut man den Bench schon auf blau um und dann sowas

lg

AMD Ryzen 5 5600X: Kleinste Zen-3-CPU erobert Platz 1 im PassMark

Am 5. November startet die Ryzen-5000-Serie mit vorerst vier Zen-3-CPUs. Die kleinste, der Ryzen 5 5600X, erobert Platz 1 im PassMark.www.computerbase.de

AMD hat seine Hausaufgaben erledigt, da hilft der Umbau von Benchmarks aus Marketingründen auch nicht zwangsweise weiter.

Bin echt gespannt auf die ersten Reviews der 5000er

Ritschie

Moderator (DC)

☆☆☆☆☆☆

- Mitglied seit

- 30.12.2010

- Beiträge

- 4.596

- Renomée

- 1.310

- Standort

- /home

- Mitglied der Planet 3DNow! Kavallerie!

- Lieblingsprojekt

- SIMAP; LHC@SixTrack; Einstein@home

- Meine Systeme

- Threadripper 3970X, Threadripper 1950X, Ryzen9 3950X, Ryzen7 1700X, Ryzen3 4300GE

- Mein Laptop

- lenovo ThinkPad E595; AMD Ryzen 5 3500U

- Details zu meinem Desktop

- Prozessor

- AMD Threadripper 3970X

- Mainboard

- MSI Creator TRX40

- Kühlung

- Watercool Heatkiller IV, i-PCPS, i-KOM, Watercool HTF4 LT

- Speicher

- 4 x 16 GB G.Skill TridentZ DDR4-3200 CL14

- Grafikprozessor

- AMD Radeon RX 6700 XT

- Display

- 27" Lenovo Legion Y27q-20 WQHD FreeSync

- SSD

- Samsung SSD 970 PRO 512GB, M.2

- Gehäuse

- Cooler Master Cosmos 1000

- Netzteil

- be quiet! DARK POWER PRO P11 550W

- Tastatur

- Ducky Shine 3

- Betriebssystem

- openSUSE Leap

- Webbrowser

- Firefox

Das Leben ist eine Pendeltür, manchmal schlägt es auch zurück

Gruß

Ritschie

eratte

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 11.11.2001

- Beiträge

- 21.837

- Renomée

- 2.807

- Standort

- Rheinberg / NRW

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- YoYo, Collatz

- Lieblingsprojekt

- YoYo

- Meine Systeme

- Wegen der aktuellen Lage alles aus.

- BOINC-Statistiken

- Mein Laptop

- Lenovo ThinkPad E15 Gen4 Intel / HP PAVILION 14-dk0002ng

- Details zu meinem Desktop

- Prozessor

- Ryzen R9 7950X

- Mainboard

- ASUS ROG Crosshair X670E Hero

- Kühlung

- Noctua NH-D15

- Speicher

- 2 x 32 GB G.Skill Trident Z DDR5 6000 CL30-40-40-96

- Grafikprozessor

- Sapphire Radeon RX7900XTX Gaming OC Nitro+

- Display

- 2 x ASUS XG27AQ (2560x1440@144 Hz)

- SSD

- Samsung 980 Pro 1 TB & Lexar NM790 4 TB

- Optisches Laufwerk

- USB Blu-Ray Brenner

- Soundkarte

- Onboard

- Gehäuse

- NEXT H7 Flow Schwarz

- Netzteil

- Corsair HX1000 (80+ Platinum)

- Tastatur

- ASUS ROG Strix Scope RX TKL Wireless / 2. Rechner&Server Cherry G80-3000N RGB TKL

- Maus

- ROG Gladius III Wireless / 2. Rechner&Server Sharkoon Light2 180

- Betriebssystem

- Windows 11 Pro 64

- Webbrowser

- Firefox

- Verschiedenes

- 4 x BQ Light Wings 14. 1 x NF-A14 Noctua Lüfter. Corsair HS80 Headset .

- Internetanbindung

- ▼VDSL 100 ▲VDSL 100

Emploi

Grand Admiral Special

- Mitglied seit

- 20.10.2005

- Beiträge

- 10.675

- Renomée

- 951

- Standort

- Elbflorenz

- Aktuelle Projekte

- WCG

- Lieblingsprojekt

- LatticeProject, Virtual Prairie (ViP), World Community Grid

- Meine Systeme

- Ein Haswell, Cloudnet GO RK3188, CX-919

- BOINC-Statistiken

- Mein Desktopsystem

- Tanz der Bonbonfee

- Mein Laptop

- HP Envy x360 Ryzen 5 2500u Vega 8

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 5950X

- Mainboard

- MSI MAG B550 TOMAHAWK

- Kühlung

- Raijintek Orcus Core 360

- Speicher

- 2x32GB Thermaltake R009R432GX2-3600C18A

- Grafikprozessor

- AMD Radeon RX 6900 XT Biggest Navi21 XTX

- Display

- AORUS FV43U + Viewsonic VP2365WB

- SSD

- Kingston FYR 4TB, HP SSD EX950 2TB (HP 8088), Samsung 840 EVO 1TB

- HDD

- 2015 abgeschafft

- Optisches Laufwerk

- 2005 abgeschafft

- Soundkarte

- RealTek ALC1200

- Gehäuse

- Sharkoon REV200

- Netzteil

- Corsair AX760i Platinum

- Tastatur

- Logitech K120

- Maus

- Speedlink TARIOS / DECUS

- Betriebssystem

- Win10 Pro AMD64

- Webbrowser

- Diverse

- Verschiedenes

- TIE Studio TUR88 Supernova, X-Board V2 (nur Headshots)

- Internetanbindung

-

▼1154 Mb/s

▲54 Mb/s

Wollte ich auch gestern Posten. In den YT-Kommentaren wurde ja schon heftig spekuliert. Ob es denn nun wieder 8+4 Kombination (5900X) geben könnte oder ob die Chillets hier jetzt untereinander direkt ohne I/O-Die kommunizieren können. Aber das es auch über den I/O die jetzt deutlich schneller geht, ist eigentlich schon klar, wie der AMD Peter anschaulich erklärt. Das im "alten" Zen der L3-Zugriff eines CCX auf den anderen L3-CCX im selben Chiplet trotzdem über den I/O Die erfolgen muss war wir neu und ist ja bäh.

Zuletzt bearbeitet:

Ähnliche Themen

- Antworten

- 436

- Aufrufe

- 38K

- Antworten

- 31

- Aufrufe

- 2K

- Antworten

- 2

- Aufrufe

- 819

- Antworten

- 3

- Aufrufe

- 3K