App installieren

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: This feature may not be available in some browsers.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

AMD - Zen 4 /4c - 5 nm/4 nm - Genoa, Bergamo, Siena, Raphael, Phoenix Point

- Ersteller pipin

- Erstellt am

eratte

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 11.11.2001

- Beiträge

- 21.840

- Renomée

- 2.807

- Standort

- Rheinberg / NRW

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- YoYo, Collatz

- Lieblingsprojekt

- YoYo

- Meine Systeme

- Wegen der aktuellen Lage alles aus.

- BOINC-Statistiken

- Mein Laptop

- Lenovo ThinkPad E15 Gen4 Intel / HP PAVILION 14-dk0002ng

- Details zu meinem Desktop

- Prozessor

- Ryzen R9 7950X

- Mainboard

- ASUS ROG Crosshair X670E Hero

- Kühlung

- Noctua NH-D15

- Speicher

- 2 x 32 GB G.Skill Trident Z DDR5 6000 CL30-40-40-96

- Grafikprozessor

- Sapphire Radeon RX7900XTX Gaming OC Nitro+

- Display

- 2 x ASUS XG27AQ (2560x1440@144 Hz)

- SSD

- Samsung 980 Pro 1 TB & Lexar NM790 4 TB

- Optisches Laufwerk

- USB Blu-Ray Brenner

- Soundkarte

- Onboard

- Gehäuse

- NEXT H7 Flow Schwarz

- Netzteil

- Corsair HX1000 (80+ Platinum)

- Tastatur

- ASUS ROG Strix Scope RX TKL Wireless / 2. Rechner&Server Cherry G80-3000N RGB TKL

- Maus

- ROG Gladius III Wireless / 2. Rechner&Server Sharkoon Light2 180

- Betriebssystem

- Windows 11 Pro 64

- Webbrowser

- Firefox

- Verschiedenes

- 4 x BQ Light Wings 14. 1 x NF-A14 Noctua Lüfter. Corsair HS80 Headset .

- Internetanbindung

- ▼VDSL 100 ▲VDSL 100

eratte

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 11.11.2001

- Beiträge

- 21.840

- Renomée

- 2.807

- Standort

- Rheinberg / NRW

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- YoYo, Collatz

- Lieblingsprojekt

- YoYo

- Meine Systeme

- Wegen der aktuellen Lage alles aus.

- BOINC-Statistiken

- Mein Laptop

- Lenovo ThinkPad E15 Gen4 Intel / HP PAVILION 14-dk0002ng

- Details zu meinem Desktop

- Prozessor

- Ryzen R9 7950X

- Mainboard

- ASUS ROG Crosshair X670E Hero

- Kühlung

- Noctua NH-D15

- Speicher

- 2 x 32 GB G.Skill Trident Z DDR5 6000 CL30-40-40-96

- Grafikprozessor

- Sapphire Radeon RX7900XTX Gaming OC Nitro+

- Display

- 2 x ASUS XG27AQ (2560x1440@144 Hz)

- SSD

- Samsung 980 Pro 1 TB & Lexar NM790 4 TB

- Optisches Laufwerk

- USB Blu-Ray Brenner

- Soundkarte

- Onboard

- Gehäuse

- NEXT H7 Flow Schwarz

- Netzteil

- Corsair HX1000 (80+ Platinum)

- Tastatur

- ASUS ROG Strix Scope RX TKL Wireless / 2. Rechner&Server Cherry G80-3000N RGB TKL

- Maus

- ROG Gladius III Wireless / 2. Rechner&Server Sharkoon Light2 180

- Betriebssystem

- Windows 11 Pro 64

- Webbrowser

- Firefox

- Verschiedenes

- 4 x BQ Light Wings 14. 1 x NF-A14 Noctua Lüfter. Corsair HS80 Headset .

- Internetanbindung

- ▼VDSL 100 ▲VDSL 100

- Mitglied seit

- 16.10.2000

- Beiträge

- 24.369

- Renomée

- 9.694

- Standort

- East Fishkill, Minga, Xanten

- Aktuelle Projekte

- Je nach Gusto

- Meine Systeme

- Ryzen 9 5900X, Ryzen 7 3700X

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Samsung P35 (16 Jahre alt ;) )

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5900X

- Mainboard

- ASRock B550

- Speicher

- 2x 16 GB DDR4 3200

- Grafikprozessor

- GeForce GTX 1650

- Display

- 27 Zoll Acer + 24 Zoll DELL

- SSD

- Samsung 980 Pro 256 GB

- HDD

- diverse

- Soundkarte

- Onboard

- Gehäuse

- Fractal Design R5

- Netzteil

- be quiet! Straight Power 10 CM 500W

- Tastatur

- Logitech Cordless Desktop

- Maus

- Logitech G502

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox, Vivaldi

- Internetanbindung

- ▼250 MBit ▲40 MBit

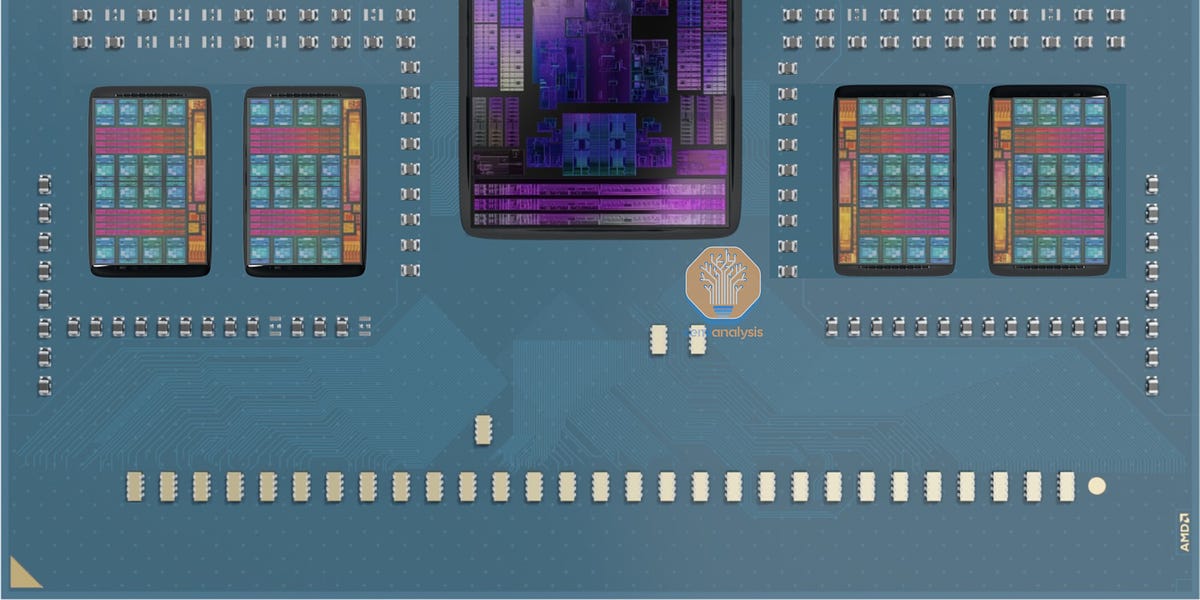

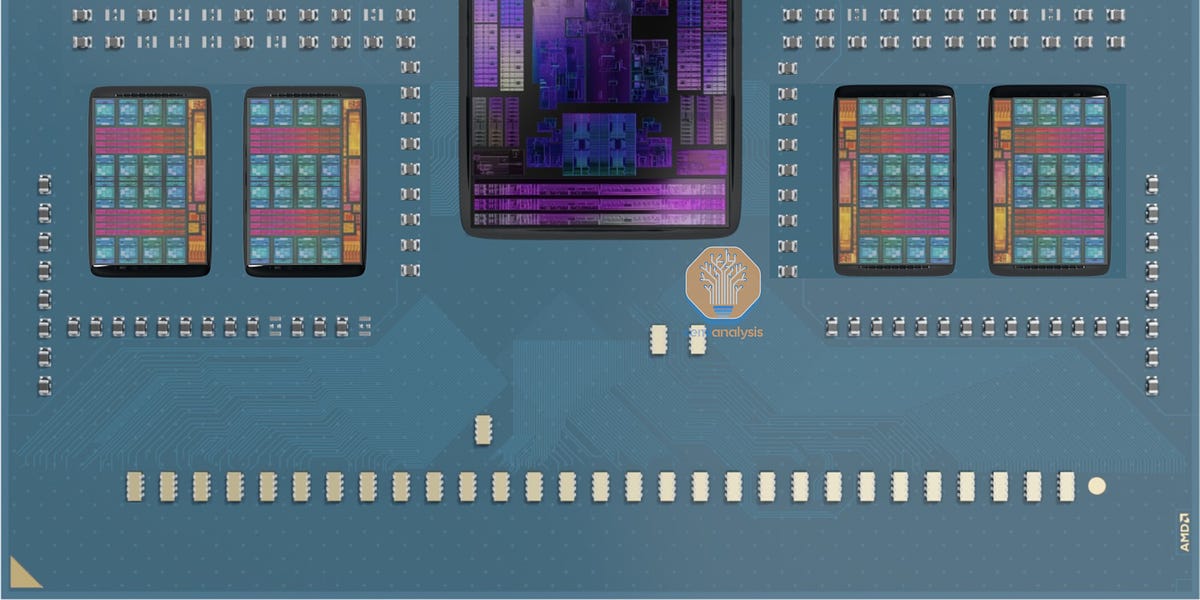

Hier mal was zu Zen 4C.

Hier beschneidet man wohl die CPU nicht einfach, sondern hat sie so umdesignt, dass man unglaubliche Die-Size-Verbesserungen erreicht.

www.semianalysis.com

www.semianalysis.com

Hier eine Kurzzusammenfassung:

Hier beschneidet man wohl die CPU nicht einfach, sondern hat sie so umdesignt, dass man unglaubliche Die-Size-Verbesserungen erreicht.

Zen 4c: AMD’s Response to Hyperscale ARM & Intel Atom

Bergamo Volumes, ASP, Performance, Hyperscale Order Shift, Die Shot, Floorplan, Physical Design, and Future Use of Dense Core Variants

However, the truly stunning thing here is the die size. 16 Zen 4c cores are barely larger than 8 Zen 4 cores. At ISSCC 2023, AMD disclosed Zen 4’s CCD to be 66.3mm². This is the design area without die seal and scribe lines at the edges. Zen 4c’s CCD design area is just 72.7mm², not even 10% bigger! Keep in mind that there are double the cores, double the L2 cache, and the same amount of L3 cache on each die. The cores must have shrunk greatly to fit even more cache per die with only a small area increase.

Hier eine Kurzzusammenfassung:

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Damit sind auch die Spekulationen vom Tisch Zen4C könnte mit 3DV Cache erscheinen. Die TSVs zu entfernen war Teil der Entschlackung, somit kein Stacking.

- Mitglied seit

- 16.10.2000

- Beiträge

- 24.369

- Renomée

- 9.694

- Standort

- East Fishkill, Minga, Xanten

- Aktuelle Projekte

- Je nach Gusto

- Meine Systeme

- Ryzen 9 5900X, Ryzen 7 3700X

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Samsung P35 (16 Jahre alt ;) )

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5900X

- Mainboard

- ASRock B550

- Speicher

- 2x 16 GB DDR4 3200

- Grafikprozessor

- GeForce GTX 1650

- Display

- 27 Zoll Acer + 24 Zoll DELL

- SSD

- Samsung 980 Pro 256 GB

- HDD

- diverse

- Soundkarte

- Onboard

- Gehäuse

- Fractal Design R5

- Netzteil

- be quiet! Straight Power 10 CM 500W

- Tastatur

- Logitech Cordless Desktop

- Maus

- Logitech G502

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox, Vivaldi

- Internetanbindung

- ▼250 MBit ▲40 MBit

Damit sind auch die Spekulationen vom Tisch Zen4C könnte mit 3DV Cache erscheinen.

Gab es die denn mal?

derDruide

Grand Admiral Special

- Mitglied seit

- 09.08.2004

- Beiträge

- 2.716

- Renomée

- 431

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 3900X

- Mainboard

- Asus Strix B450-F Gaming

- Kühlung

- Noctua NH-C14

- Speicher

- 32 GB DDR4-3200 CL14 FlareX

- Grafikprozessor

- Radeon RX 590

- Display

- 31.5" Eizo FlexScan EV3285

- SSD

- Corsair MP510 2 TB, Samsung 970 Evo 512 GB

- HDD

- Seagate Ironwulf 6 TB

- Optisches Laufwerk

- Plextor PX-880SA

- Soundkarte

- Creative SoundblasterX AE-7

- Gehäuse

- Antec P280

- Netzteil

- be quiet! Straight Power E9 400W

- Maus

- Logitech Trackman Marble (Trackball)

- Betriebssystem

- openSUSE 15.2

- Webbrowser

- Firefox

- Internetanbindung

- ▼50 MBit ▲10 MBit

Wundert mich auch. ZEN4c ist ja schon länger als kleinerer ZEN4-Kern bekannt. Mit ZEN5 und den Gerüchten über 16 und 40 CUs würde der Cache mehr Sinn machen.Gab es die denn mal?

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Ja, im 3DCenter gab es einige die für Mobile Zen4C mit 3DCache spekuliert hatten. Auch für APUs. Es wird allerdings klar, dass die schlanken Kerne in erster Linie für hohe Kernzahl pro Die optimiert sind, was im Mobile bis 16 Kernen weniger wichtig ist.

- Mitglied seit

- 16.10.2000

- Beiträge

- 24.369

- Renomée

- 9.694

- Standort

- East Fishkill, Minga, Xanten

- Aktuelle Projekte

- Je nach Gusto

- Meine Systeme

- Ryzen 9 5900X, Ryzen 7 3700X

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Samsung P35 (16 Jahre alt ;) )

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5900X

- Mainboard

- ASRock B550

- Speicher

- 2x 16 GB DDR4 3200

- Grafikprozessor

- GeForce GTX 1650

- Display

- 27 Zoll Acer + 24 Zoll DELL

- SSD

- Samsung 980 Pro 256 GB

- HDD

- diverse

- Soundkarte

- Onboard

- Gehäuse

- Fractal Design R5

- Netzteil

- be quiet! Straight Power 10 CM 500W

- Tastatur

- Logitech Cordless Desktop

- Maus

- Logitech G502

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox, Vivaldi

- Internetanbindung

- ▼250 MBit ▲40 MBit

Ja, im 3DCenter gab es einige die für Mobile Zen4C mit 3DCache spekuliert hatten. Auch für APUs. Es wird allerdings klar, dass die schlanken Kerne in erster Linie für hohe Kernzahl pro Die optimiert sind, was im Mobile bis 16 Kernen weniger wichtig ist.

Imo ist das wirklich sehr unwahrscheinlich. AMD bekommt es doch kaum hin seine "normalen" Mobile Prozessoren zu launchen.

derDruide

Grand Admiral Special

- Mitglied seit

- 09.08.2004

- Beiträge

- 2.716

- Renomée

- 431

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 3900X

- Mainboard

- Asus Strix B450-F Gaming

- Kühlung

- Noctua NH-C14

- Speicher

- 32 GB DDR4-3200 CL14 FlareX

- Grafikprozessor

- Radeon RX 590

- Display

- 31.5" Eizo FlexScan EV3285

- SSD

- Corsair MP510 2 TB, Samsung 970 Evo 512 GB

- HDD

- Seagate Ironwulf 6 TB

- Optisches Laufwerk

- Plextor PX-880SA

- Soundkarte

- Creative SoundblasterX AE-7

- Gehäuse

- Antec P280

- Netzteil

- be quiet! Straight Power E9 400W

- Maus

- Logitech Trackman Marble (Trackball)

- Betriebssystem

- openSUSE 15.2

- Webbrowser

- Firefox

- Internetanbindung

- ▼50 MBit ▲10 MBit

Ich denke mal, das hat mit dem Absturz bei der Nachfrage zu tun. Wenn du liest, wie dramatisch die Einbrüche sind, dann sind die Lager alle rappelvoll. In so einer Lage neue (zusätzliche) Geräte auf den Markt zu werfen heißt, die Lagerware endgültig abzuschreiben.

Zuletzt bearbeitet:

derDruide

Grand Admiral Special

- Mitglied seit

- 09.08.2004

- Beiträge

- 2.716

- Renomée

- 431

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 3900X

- Mainboard

- Asus Strix B450-F Gaming

- Kühlung

- Noctua NH-C14

- Speicher

- 32 GB DDR4-3200 CL14 FlareX

- Grafikprozessor

- Radeon RX 590

- Display

- 31.5" Eizo FlexScan EV3285

- SSD

- Corsair MP510 2 TB, Samsung 970 Evo 512 GB

- HDD

- Seagate Ironwulf 6 TB

- Optisches Laufwerk

- Plextor PX-880SA

- Soundkarte

- Creative SoundblasterX AE-7

- Gehäuse

- Antec P280

- Netzteil

- be quiet! Straight Power E9 400W

- Maus

- Logitech Trackman Marble (Trackball)

- Betriebssystem

- openSUSE 15.2

- Webbrowser

- Firefox

- Internetanbindung

- ▼50 MBit ▲10 MBit

Golem-Bericht zu ZEN 4c: So schrumpft AMD die Epyc-Kerne um fast die Hälfte

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 14.336

- Renomée

- 1.974

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 3950X

- Mainboard

- MSI MPG X570 GAMING PRO CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 4x 16 GB G.Skill Trident Z RGB, DDR4-3200, CL14

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Intel 600p 1TB

- HDD

- Western Digital WD Red 2 & 3TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

Eine Schlussfolgerung erscheint mir allerdings wenig sinnvoll.

Statt 12 wären wohl problemlos 8 Chiplets drin was 128 Kerne pro Prozessor bedeuten würde und wenn sogar die 12 Chiplet Variante möglich ist (müssen eben auf das Package passen) wären satte 192 Kerne drin. Das wäre ein massiver Anstieg der Kernzahl.

Warum sollte es nicht mehr Kerne pro CPU geben wenn in den einzelnen, etwas größeren Chiplets doppelt so viele Kerne stecken?Nach Einschätzung von Patel kann AMD die Kernanzahl bei Bergamo allerdings nicht weiter steigern: Auf der Platine des Package seien nicht mehr Leiter zur Anbindung an das I/O Die unterzubringen.

Doppelt so viele Kerne pro Core Complex Die (CCD) bei nicht einmal 10 Prozent mehr Chipfläche: Die Zen-4c-Kerne.....

Die Leitungen auf dem Package sind von der Anzahl der Chiplets abhängig, welche die CPU Chiplets mit dem IO Die verbinden.Die Bergamo-Dies enthalten jeweils zwei Core Complexes (CCX) mit je acht Prozessorkernen.

Statt 12 wären wohl problemlos 8 Chiplets drin was 128 Kerne pro Prozessor bedeuten würde und wenn sogar die 12 Chiplet Variante möglich ist (müssen eben auf das Package passen) wären satte 192 Kerne drin. Das wäre ein massiver Anstieg der Kernzahl.

TOMBOMBADIL

Lt. Commander

- Mitglied seit

- 28.04.2008

- Beiträge

- 143

- Renomée

- 10

- Standort

- Seligne, Frankreich

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 2700

- Mainboard

- MSI B450M PRO-VDH

- Kühlung

- Thermalright ARO-M14 Orange

- Speicher

- 64GB Corsair Vengeance LPX DDR4-3200

- Grafikprozessor

- Nvidia Geforce GTX 1070 ASUS STRIX 8GB

- Display

- 2x 1920×1080

- SSD

- 1x 1TB m.2, 2x 500GB Sata

- Gehäuse

- Fractal Design Define S

- Netzteil

- 550 Watt be quiet! Straight Power 11 Modular 80+ Gold

- Tastatur

- Cherry MX Board 1.0

- Maus

- Logitech G502

- Betriebssystem

- (K)Ubuntu 20.04 & Win10 for gaming

- Webbrowser

- Firefox

Aber 8 Chiplets für 128 C Kerne statt 96 normaler Kerner ist ja was AMD bei Bergamo macht. Aber für 12 C Kern Chiplets passt wohl irgendwas nicht.

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 14.336

- Renomée

- 1.974

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 3950X

- Mainboard

- MSI MPG X570 GAMING PRO CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 4x 16 GB G.Skill Trident Z RGB, DDR4-3200, CL14

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Intel 600p 1TB

- HDD

- Western Digital WD Red 2 & 3TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

Eben und da 128 Kerne mehr sind als 96 war die Aussage einfach nur quatsch.

Vermutlich hatte da jemand gepennt Chiplets (CCDs) mit Kernen verwechselt.

Vermutlich sind die etwas größeren CCDs für den 12er Verbund einfach zu groß um am Ende noch richtig unter den Deckel zu passen oder der Ausbau wäre vom Stromhunger her zu viel für die Spezifikationen des Sockels.

Vermutlich hatte da jemand gepennt Chiplets (CCDs) mit Kernen verwechselt.

Vermutlich sind die etwas größeren CCDs für den 12er Verbund einfach zu groß um am Ende noch richtig unter den Deckel zu passen oder der Ausbau wäre vom Stromhunger her zu viel für die Spezifikationen des Sockels.

Pinnacle Ridge

Vice Admiral Special

- Mitglied seit

- 04.03.2017

- Beiträge

- 528

- Renomée

- 7

10 würden sich vielleicht ausgehen.

Aber da wäre halt die Frage, warum genau AMD das machen sollte, wenn Intel eh schon bei 128C nicht mithalten kann.

Aber da wäre halt die Frage, warum genau AMD das machen sollte, wenn Intel eh schon bei 128C nicht mithalten kann.

TOMBOMBADIL

Lt. Commander

- Mitglied seit

- 28.04.2008

- Beiträge

- 143

- Renomée

- 10

- Standort

- Seligne, Frankreich

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 2700

- Mainboard

- MSI B450M PRO-VDH

- Kühlung

- Thermalright ARO-M14 Orange

- Speicher

- 64GB Corsair Vengeance LPX DDR4-3200

- Grafikprozessor

- Nvidia Geforce GTX 1070 ASUS STRIX 8GB

- Display

- 2x 1920×1080

- SSD

- 1x 1TB m.2, 2x 500GB Sata

- Gehäuse

- Fractal Design Define S

- Netzteil

- 550 Watt be quiet! Straight Power 11 Modular 80+ Gold

- Tastatur

- Cherry MX Board 1.0

- Maus

- Logitech G502

- Betriebssystem

- (K)Ubuntu 20.04 & Win10 for gaming

- Webbrowser

- Firefox

Ich glaube mit

ist gemeint das zwar von 96 auf 128 aber nicht weiter auf 192 kerne gesteigert werden kann. Das passt schon.... kann AMD die Kernanzahl bei Bergamo allerdings nicht weiter steigern

Captn-Future

Moderation DC, P3DN Vize-Kommandant

- Mitglied seit

- 16.08.2004

- Beiträge

- 8.430

- Renomée

- 313

- Standort

- VIP Lounge

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- QMC, Simap

- Lieblingsprojekt

- QMC

- Meine Systeme

- X4 940 BE

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- Intel Xeon E3-1230v2

- Mainboard

- GA-Z77-UD3

- Kühlung

- Thermalright Macho Rev. A

- Speicher

- 16 GB Kingston blue

- Grafikprozessor

- Gigabyte GTX 660

- Display

- HP ZR2440w 1920x1200

- SSD

- Samsung SSD 830 256 GB

- HDD

- WD Blue 1 TB

- Optisches Laufwerk

- LG GSA-H10N

- Gehäuse

- LianLi V1000 Silber

- Netzteil

- Cougar SE400

- Betriebssystem

- Windows 7

- Webbrowser

- FireFox

Wenn AMD beim EPYC 9654 12 CCXs/CCDs mit je 8 Kernen vorsieht und auf 96 Kerne kommt, warum sollte dann ein Bergamo CCX mit 16 Kernen nicht auch 12x auf den Träger und somit in den Sockel passen? 12*16 wären dann ja besagte 192 Kerne.

Oder wird das so wie bei der Vorstellung von Zen3: Selbstverständlich ist da noch Platz für ein weiteres Die!

Oder wird das so wie bei der Vorstellung von Zen3: Selbstverständlich ist da noch Platz für ein weiteres Die!

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 14.336

- Renomée

- 1.974

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 3950X

- Mainboard

- MSI MPG X570 GAMING PRO CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 4x 16 GB G.Skill Trident Z RGB, DDR4-3200, CL14

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Intel 600p 1TB

- HDD

- Western Digital WD Red 2 & 3TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

@Captn-Future

Wie gesagt, wenn es mechanisch nicht auf den 12er Träger oder unter den Spreader passt bzw. die Grenze der Strombelastbarkeit des Sockels gesprengt wird ist ein solches Produkt ganz einfach nicht umsetzbar.

Wie gesagt, wenn es mechanisch nicht auf den 12er Träger oder unter den Spreader passt bzw. die Grenze der Strombelastbarkeit des Sockels gesprengt wird ist ein solches Produkt ganz einfach nicht umsetzbar.

derDruide

Grand Admiral Special

- Mitglied seit

- 09.08.2004

- Beiträge

- 2.716

- Renomée

- 431

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 3900X

- Mainboard

- Asus Strix B450-F Gaming

- Kühlung

- Noctua NH-C14

- Speicher

- 32 GB DDR4-3200 CL14 FlareX

- Grafikprozessor

- Radeon RX 590

- Display

- 31.5" Eizo FlexScan EV3285

- SSD

- Corsair MP510 2 TB, Samsung 970 Evo 512 GB

- HDD

- Seagate Ironwulf 6 TB

- Optisches Laufwerk

- Plextor PX-880SA

- Soundkarte

- Creative SoundblasterX AE-7

- Gehäuse

- Antec P280

- Netzteil

- be quiet! Straight Power E9 400W

- Maus

- Logitech Trackman Marble (Trackball)

- Betriebssystem

- openSUSE 15.2

- Webbrowser

- Firefox

- Internetanbindung

- ▼50 MBit ▲10 MBit

Ein Ryzen 5 7500F steht kurz vor der Vorstellung, er hat 6 Kerne und 100 MHz weniger Takt als der 7600.

Die wahrscheinlichste Variante für das F-Suffix ist ein I/O-Die mit defekter Grafik, damit man in so einem Fall nicht die ganze CPU wegwerfen muss.

videocardz.com

videocardz.com

Die wahrscheinlichste Variante für das F-Suffix ist ein I/O-Die mit defekter Grafik, damit man in so einem Fall nicht die ganze CPU wegwerfen muss.

AMD Ryzen 5 7500F to launch this week, the first AM5 CPU without integrated RDNA2 graphics - VideoCardz.com

AMD Ryzen 5 7500F has no integrated graphics AMD set to launch a new 6-core CPU this week, claims Korean retailer. AMD Ryzen 5 7500F CPU, Source: 신성조 It appears AMD will soon release a new 6-core processor that may lack one of the most common features of AM5 CPUs. The Ryzen 5 7500F shall […]

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 14.336

- Renomée

- 1.974

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 3950X

- Mainboard

- MSI MPG X570 GAMING PRO CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 4x 16 GB G.Skill Trident Z RGB, DDR4-3200, CL14

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Intel 600p 1TB

- HDD

- Western Digital WD Red 2 & 3TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

Muss man doch ohnehin nicht, man bestückt die CPU einfach nicht mit so einem IO Die.

Das wäre nur sinnvoll wenn man so die teildefekten Phoenix Die verarbeiten will allerdings wäre dann fraglich ob der Chip genug PCIe Lanes besitzt.

Sollte der wirklich 38 MB L2+L3 haben dann scheidet Phoenix definitiv aus denn die haben nur 16 MB statt 32 MB L3 Cache.

Da sich die Anhängsel bisher vor allem auf die TDP Einstufung bezog rate ich einfach mal mit und tippe auf ein Stromspar Modell mit einer TDP von 45 oder 32 W.

Das wäre nur sinnvoll wenn man so die teildefekten Phoenix Die verarbeiten will allerdings wäre dann fraglich ob der Chip genug PCIe Lanes besitzt.

Doppelposting wurde automatisch zusammengeführt:

Sollte der wirklich 38 MB L2+L3 haben dann scheidet Phoenix definitiv aus denn die haben nur 16 MB statt 32 MB L3 Cache.

Doppelposting wurde automatisch zusammengeführt:

Da sich die Anhängsel bisher vor allem auf die TDP Einstufung bezog rate ich einfach mal mit und tippe auf ein Stromspar Modell mit einer TDP von 45 oder 32 W.

Zuletzt bearbeitet:

derDruide

Grand Admiral Special

- Mitglied seit

- 09.08.2004

- Beiträge

- 2.716

- Renomée

- 431

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 3900X

- Mainboard

- Asus Strix B450-F Gaming

- Kühlung

- Noctua NH-C14

- Speicher

- 32 GB DDR4-3200 CL14 FlareX

- Grafikprozessor

- Radeon RX 590

- Display

- 31.5" Eizo FlexScan EV3285

- SSD

- Corsair MP510 2 TB, Samsung 970 Evo 512 GB

- HDD

- Seagate Ironwulf 6 TB

- Optisches Laufwerk

- Plextor PX-880SA

- Soundkarte

- Creative SoundblasterX AE-7

- Gehäuse

- Antec P280

- Netzteil

- be quiet! Straight Power E9 400W

- Maus

- Logitech Trackman Marble (Trackball)

- Betriebssystem

- openSUSE 15.2

- Webbrowser

- Firefox

- Internetanbindung

- ▼50 MBit ▲10 MBit

Die iGPU liegt halt nahe, weil Intel sie auch so nennt. Eine Abweichung davon wäre schon seltsam, wir werden es diese Woche sehen.

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 14.336

- Renomée

- 1.974

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 3950X

- Mainboard

- MSI MPG X570 GAMING PRO CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 4x 16 GB G.Skill Trident Z RGB, DDR4-3200, CL14

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Intel 600p 1TB

- HDD

- Western Digital WD Red 2 & 3TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

Die Abweichung ist eher normal.

Weder das "G" für die APUs, noch das "X" bei den Modellen mit hoher TDP hat einen Bezug auf Intels Namensgebung.

Sollten das "F" Modell dennoch mit deaktivierter GPU auf den Markt kommen dann wohl nur um einen Teil des Aussschusses bei der Produktion der IO Dies zu verwerten.

Weder das "G" für die APUs, noch das "X" bei den Modellen mit hoher TDP hat einen Bezug auf Intels Namensgebung.

Sollten das "F" Modell dennoch mit deaktivierter GPU auf den Markt kommen dann wohl nur um einen Teil des Aussschusses bei der Produktion der IO Dies zu verwerten.

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Das glaube ich eher nicht:Die wahrscheinlichste Variante für das F-Suffix ist ein I/O-Die mit defekter Grafik, damit man in so einem Fall nicht die ganze CPU wegwerfen muss.

Man muss keine komplette CPU wegwerfen, wenn die iGPU des IO-Dies nicht funktioniert. Man muss einfach den IO-Die entsorgen und die CCDs auf ein funktionierendes IO drauf schnallen. Das Problem hat nur Intel mit seinen Monolithen. Daher wird AMD hier deutlich weniger Bedarf haben defekte IO-Dies wiederzuverwenden, die auf günstigen 6nm produziert werden. Ich denke die Yields des IO-Dies geben das nicht her.

Sompe hatte es ja auch schon geschrieben.

Ich glaube ebenfalls es wird eher etwas stromoptimiertes. Könnte etwas für den NAS-Markt, wie Synology und QNAP werden.

derDruide

Grand Admiral Special

- Mitglied seit

- 09.08.2004

- Beiträge

- 2.716

- Renomée

- 431

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 3900X

- Mainboard

- Asus Strix B450-F Gaming

- Kühlung

- Noctua NH-C14

- Speicher

- 32 GB DDR4-3200 CL14 FlareX

- Grafikprozessor

- Radeon RX 590

- Display

- 31.5" Eizo FlexScan EV3285

- SSD

- Corsair MP510 2 TB, Samsung 970 Evo 512 GB

- HDD

- Seagate Ironwulf 6 TB

- Optisches Laufwerk

- Plextor PX-880SA

- Soundkarte

- Creative SoundblasterX AE-7

- Gehäuse

- Antec P280

- Netzteil

- be quiet! Straight Power E9 400W

- Maus

- Logitech Trackman Marble (Trackball)

- Betriebssystem

- openSUSE 15.2

- Webbrowser

- Firefox

- Internetanbindung

- ▼50 MBit ▲10 MBit

Der Ryzen 7500F wird jetzt in Support-Listen der Mainboard-Hersteller aufgeführt. Es handelt sich um einen Ryzen 7600 mit deaktiviertem Grafikteil und etwas weniger Takt.

Zuletzt bearbeitet:

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Ok, überrascht mich.

eratte

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 11.11.2001

- Beiträge

- 21.840

- Renomée

- 2.807

- Standort

- Rheinberg / NRW

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- YoYo, Collatz

- Lieblingsprojekt

- YoYo

- Meine Systeme

- Wegen der aktuellen Lage alles aus.

- BOINC-Statistiken

- Mein Laptop

- Lenovo ThinkPad E15 Gen4 Intel / HP PAVILION 14-dk0002ng

- Details zu meinem Desktop

- Prozessor

- Ryzen R9 7950X

- Mainboard

- ASUS ROG Crosshair X670E Hero

- Kühlung

- Noctua NH-D15

- Speicher

- 2 x 32 GB G.Skill Trident Z DDR5 6000 CL30-40-40-96

- Grafikprozessor

- Sapphire Radeon RX7900XTX Gaming OC Nitro+

- Display

- 2 x ASUS XG27AQ (2560x1440@144 Hz)

- SSD

- Samsung 980 Pro 1 TB & Lexar NM790 4 TB

- Optisches Laufwerk

- USB Blu-Ray Brenner

- Soundkarte

- Onboard

- Gehäuse

- NEXT H7 Flow Schwarz

- Netzteil

- Corsair HX1000 (80+ Platinum)

- Tastatur

- ASUS ROG Strix Scope RX TKL Wireless / 2. Rechner&Server Cherry G80-3000N RGB TKL

- Maus

- ROG Gladius III Wireless / 2. Rechner&Server Sharkoon Light2 180

- Betriebssystem

- Windows 11 Pro 64

- Webbrowser

- Firefox

- Verschiedenes

- 4 x BQ Light Wings 14. 1 x NF-A14 Noctua Lüfter. Corsair HS80 Headset .

- Internetanbindung

- ▼VDSL 100 ▲VDSL 100

Die Frage ist wie viel weniger der kosten soll das man dann auf die Idee kommt den zukaufen statt einem 7600 - für 20 Euro würde ich das nicht in Erwägung ziehen.

Ähnliche Themen

- Antworten

- 3

- Aufrufe

- 957

- Antworten

- 36

- Aufrufe

- 4K

- Antworten

- 0

- Aufrufe

- 566