App installieren

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: This feature may not be available in some browsers.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

IBM Power10 Serverchip in 7nm Fertigung von Samsung

- Ersteller Complicated

- Erstellt am

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

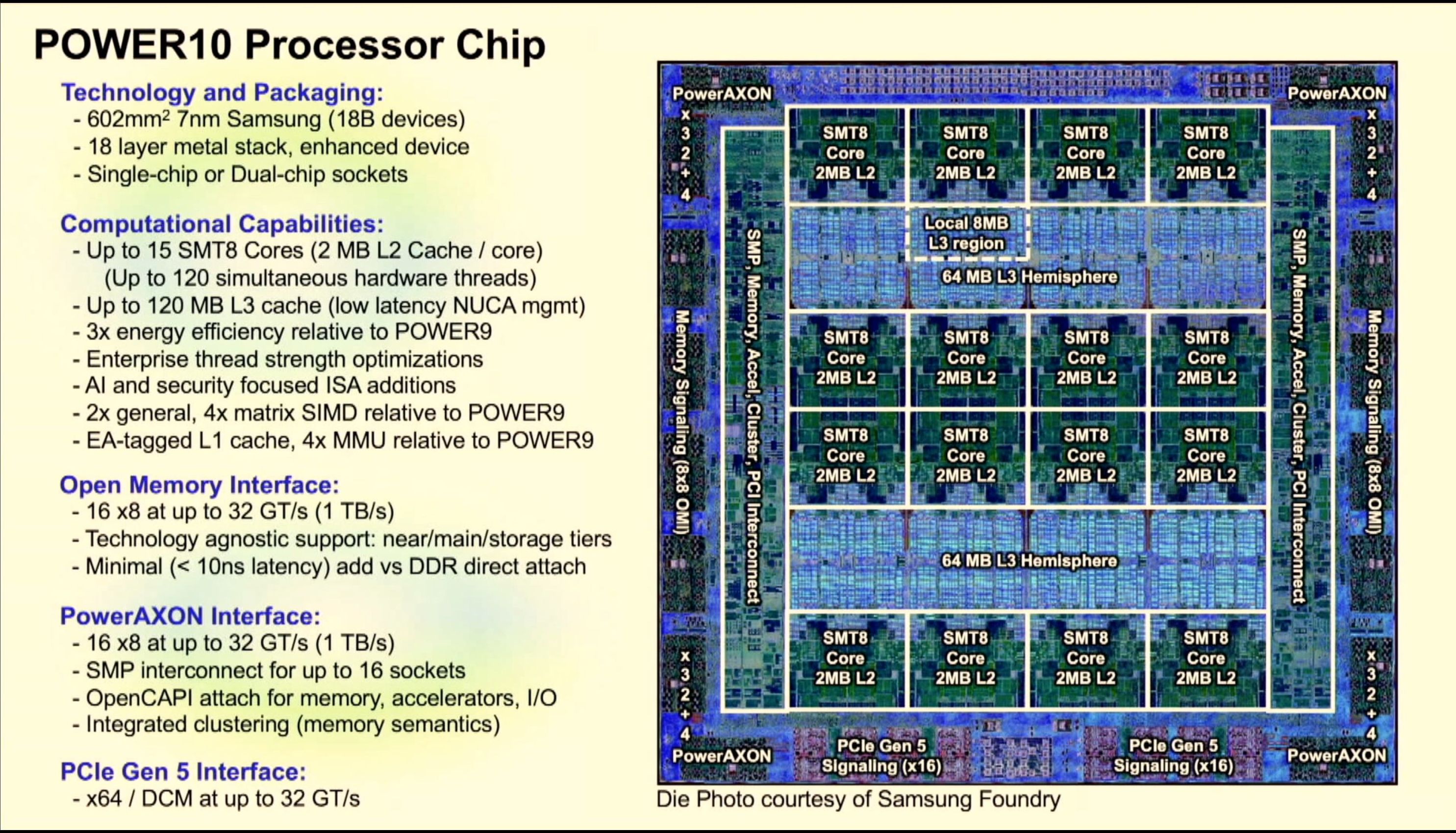

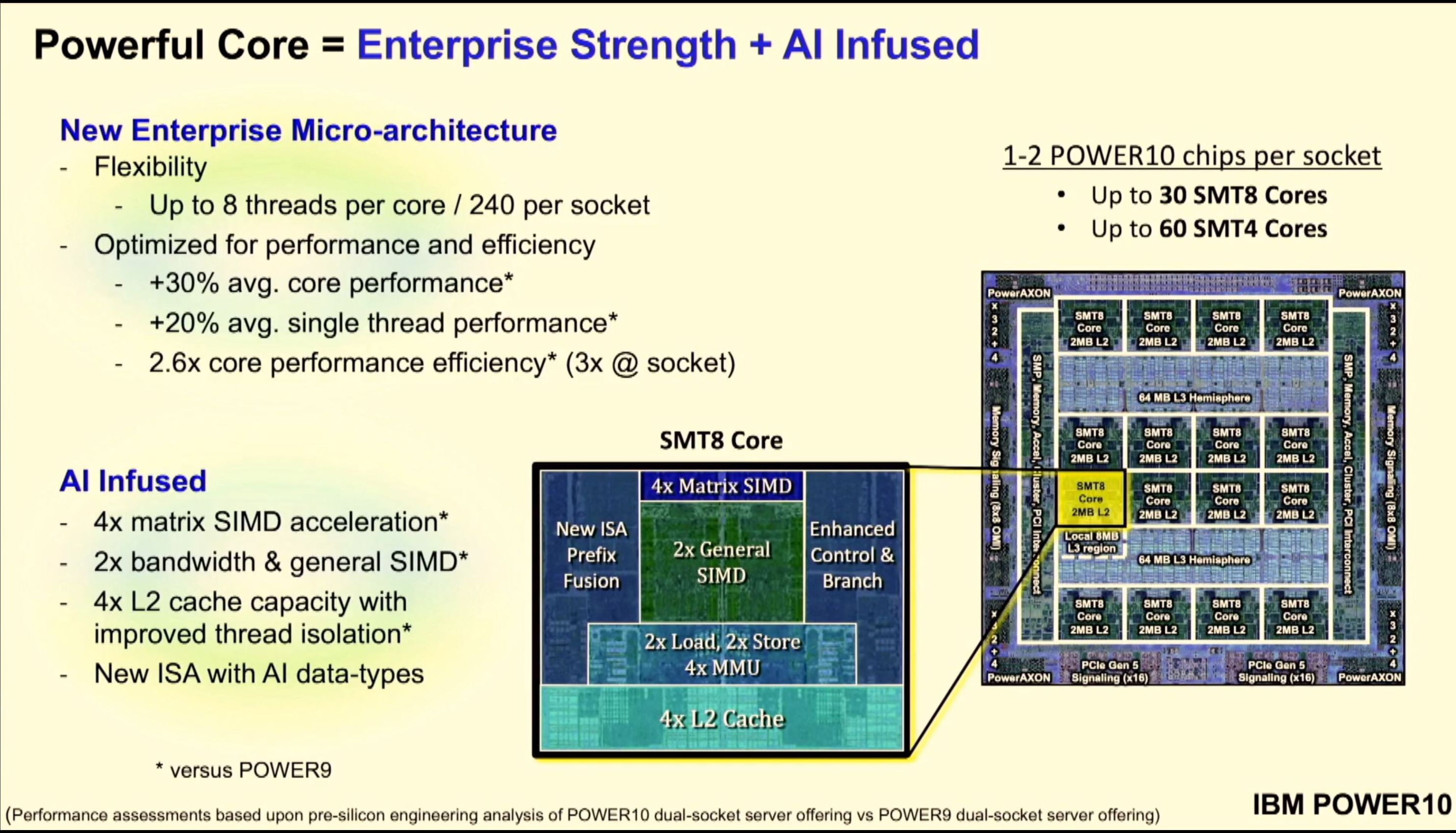

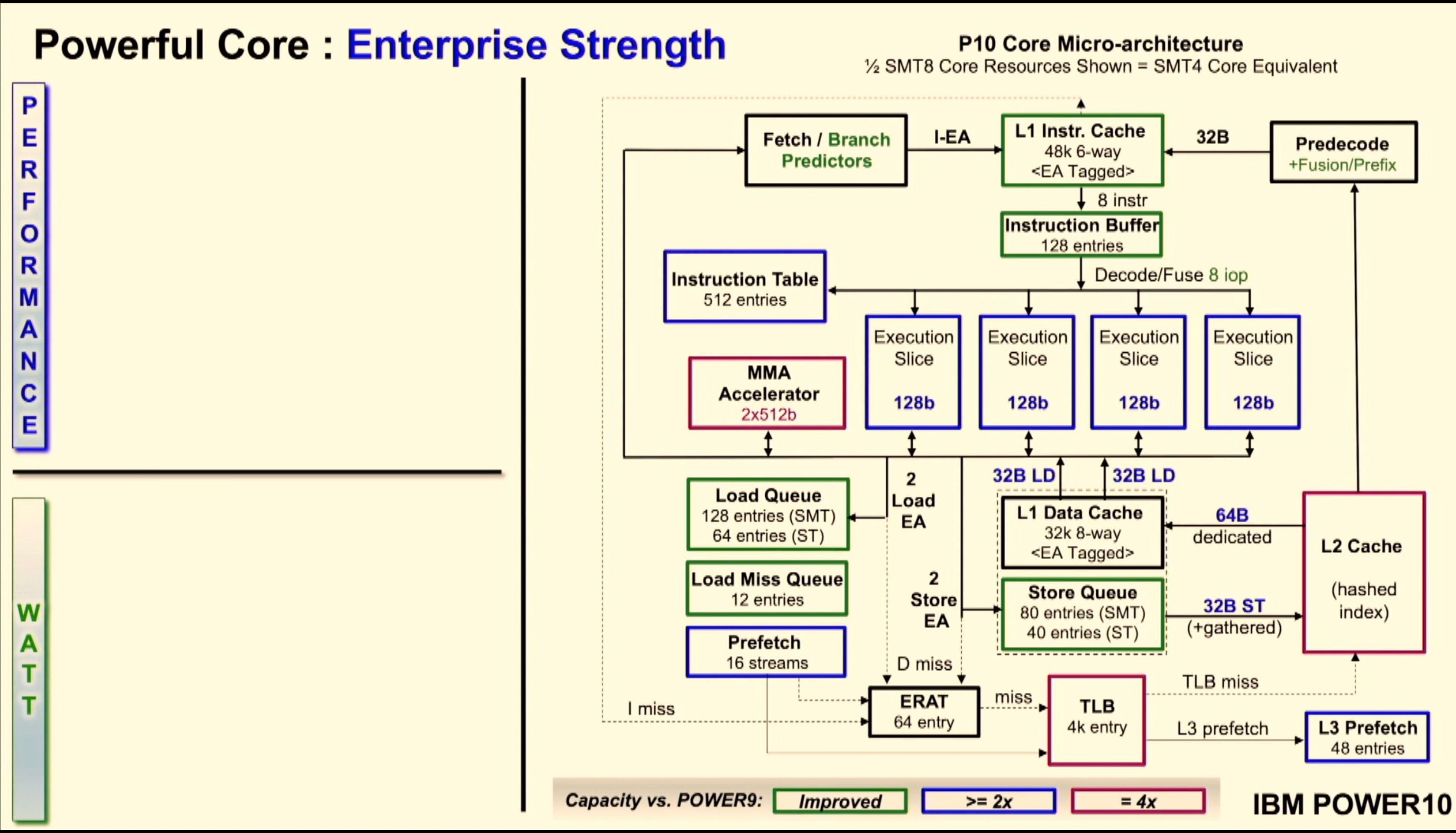

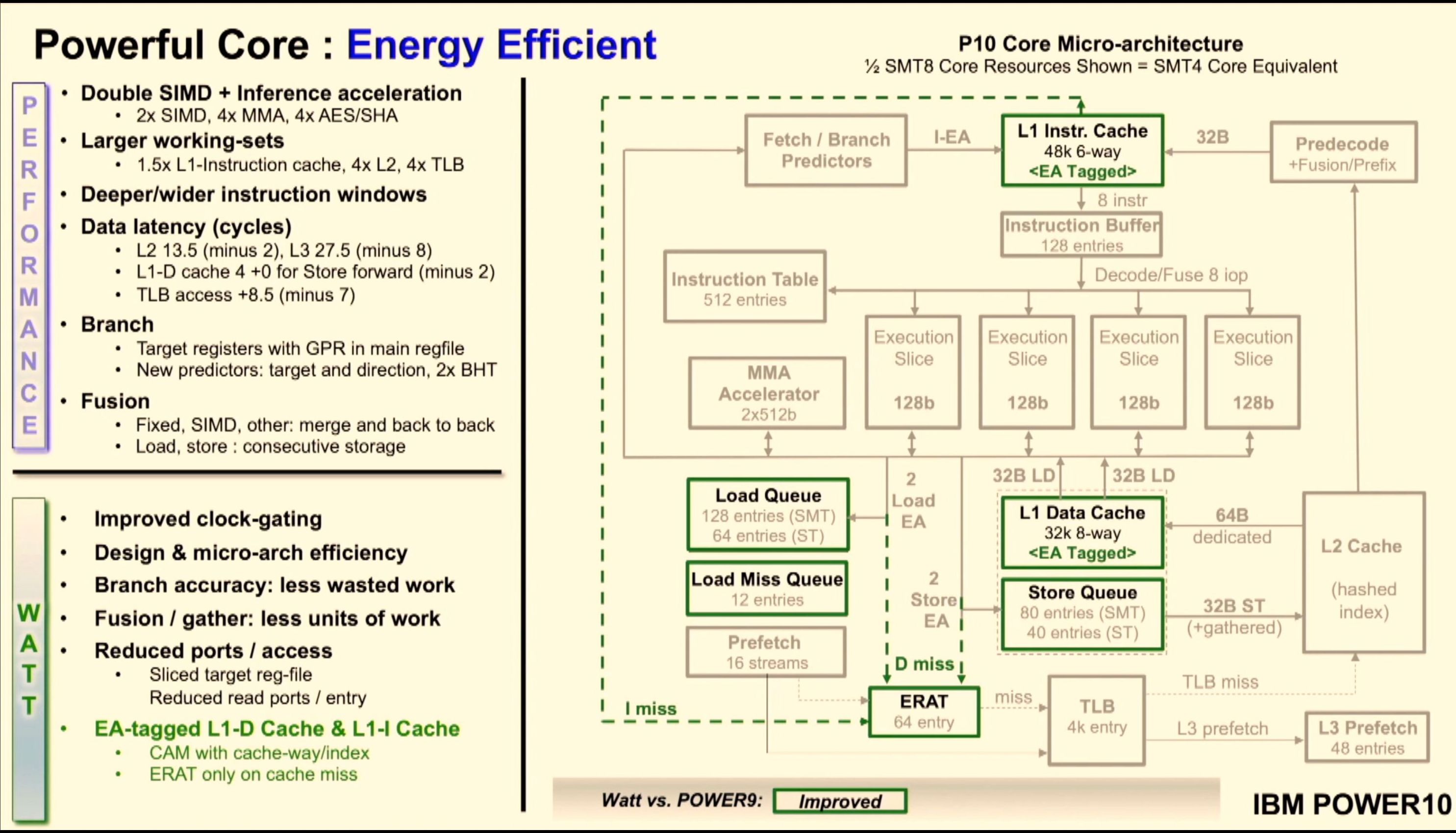

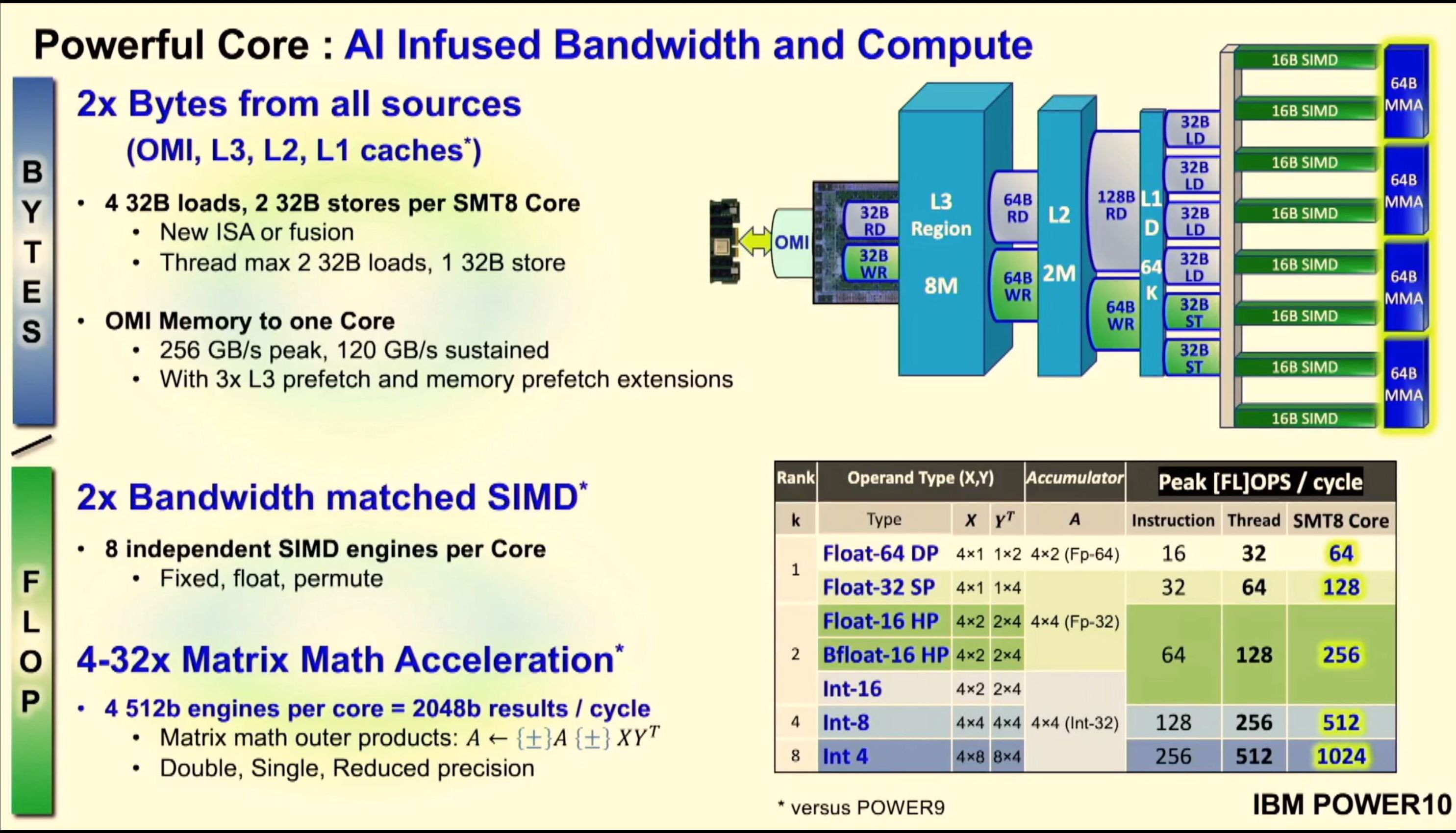

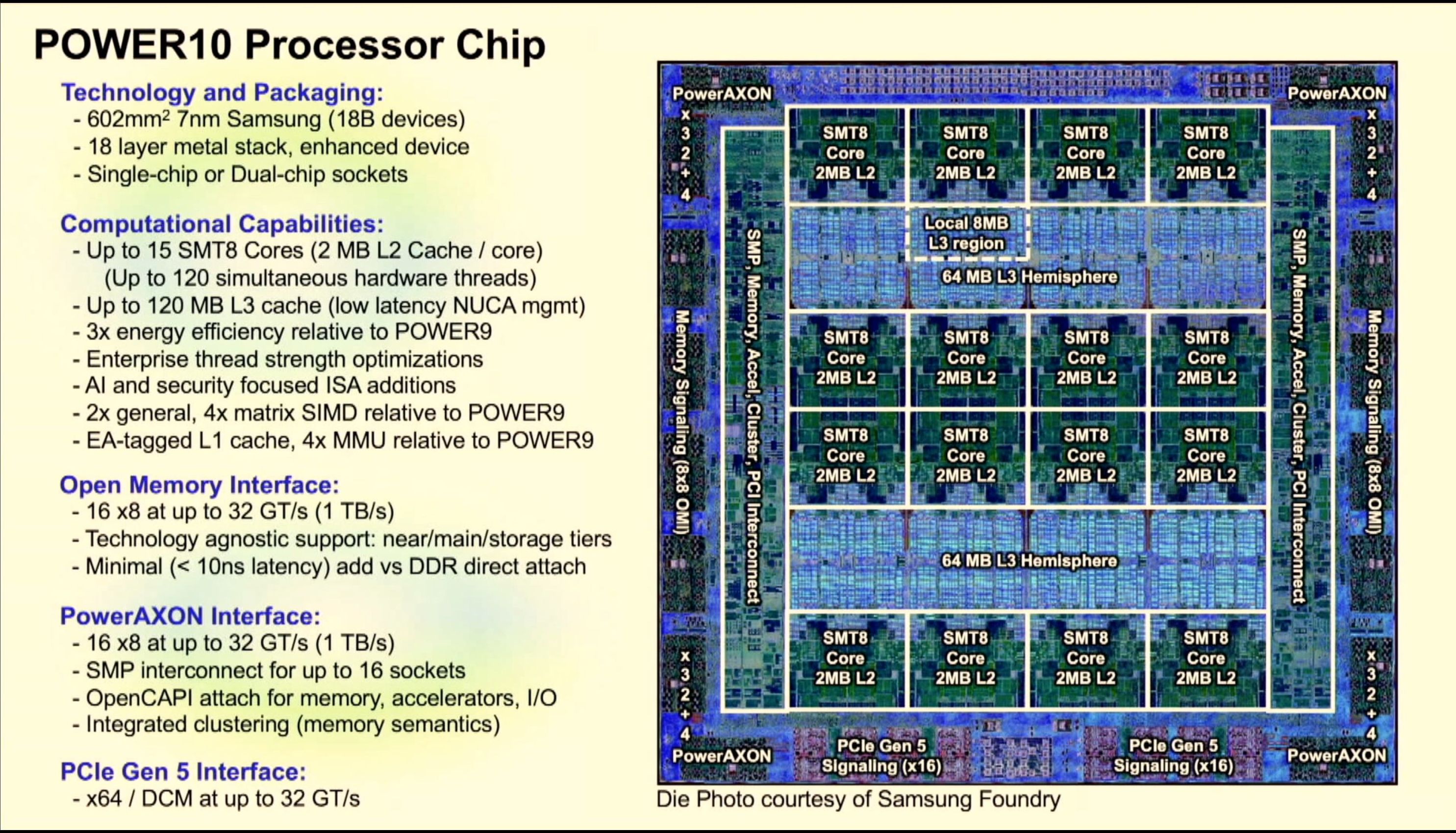

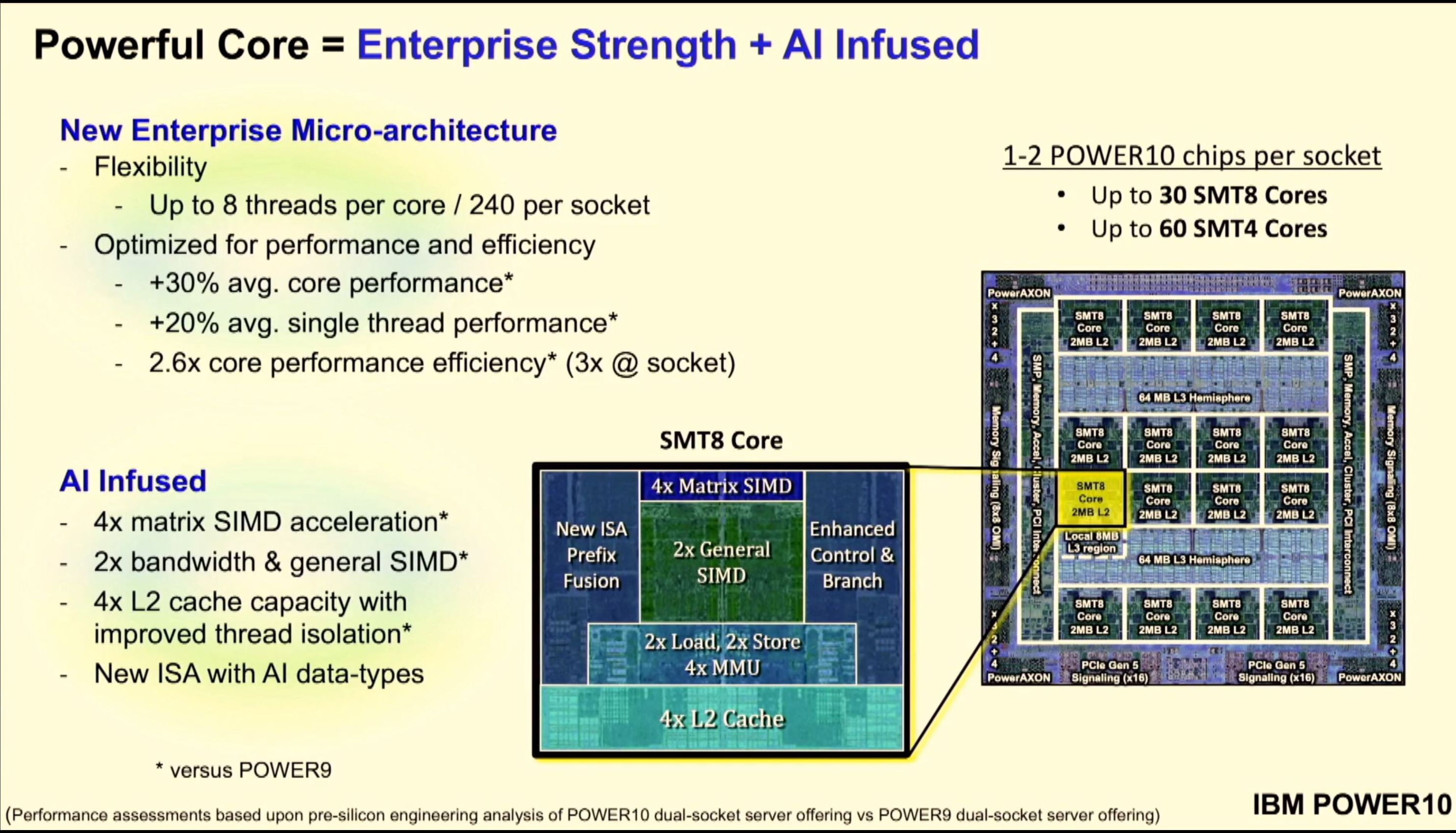

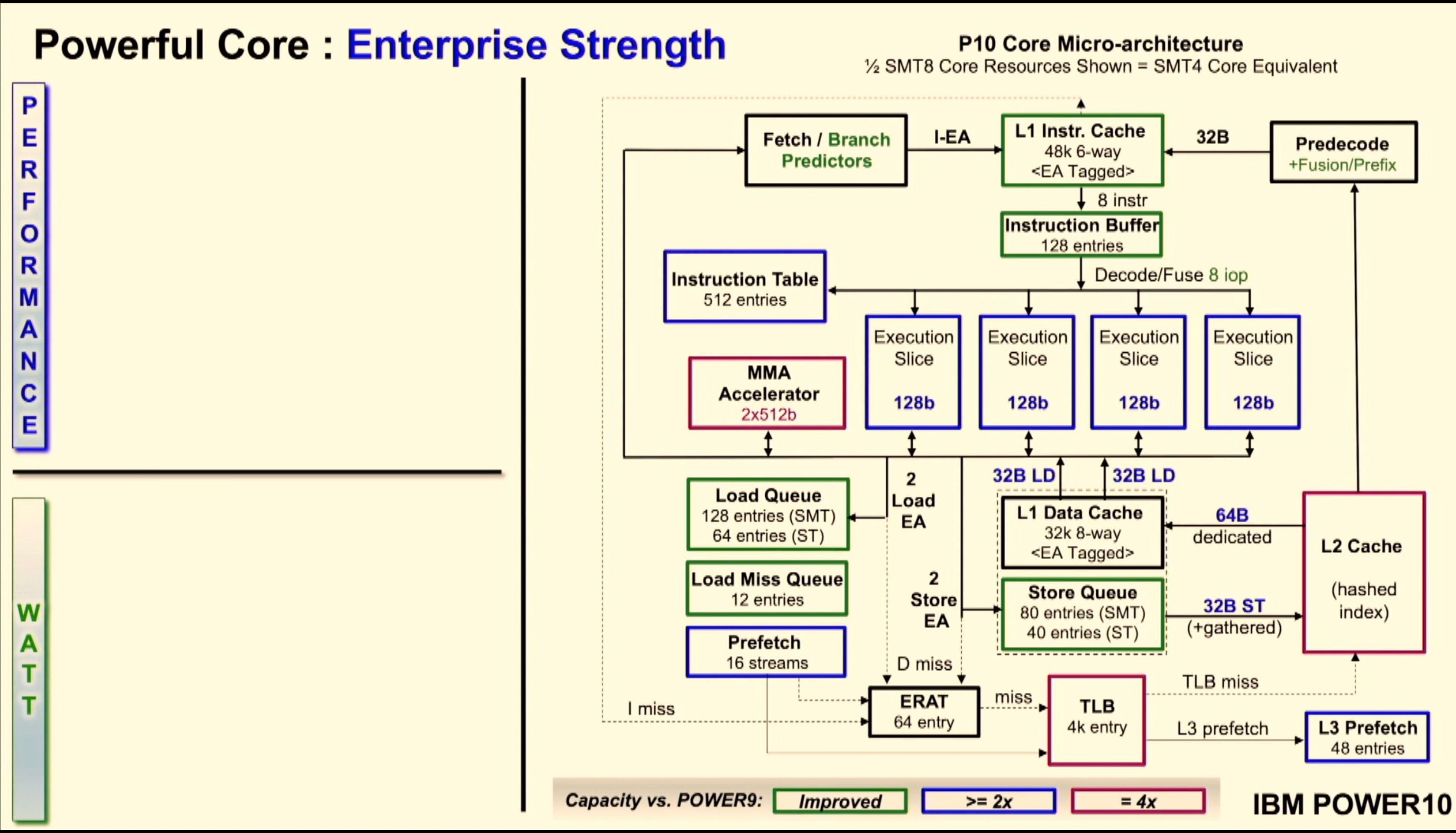

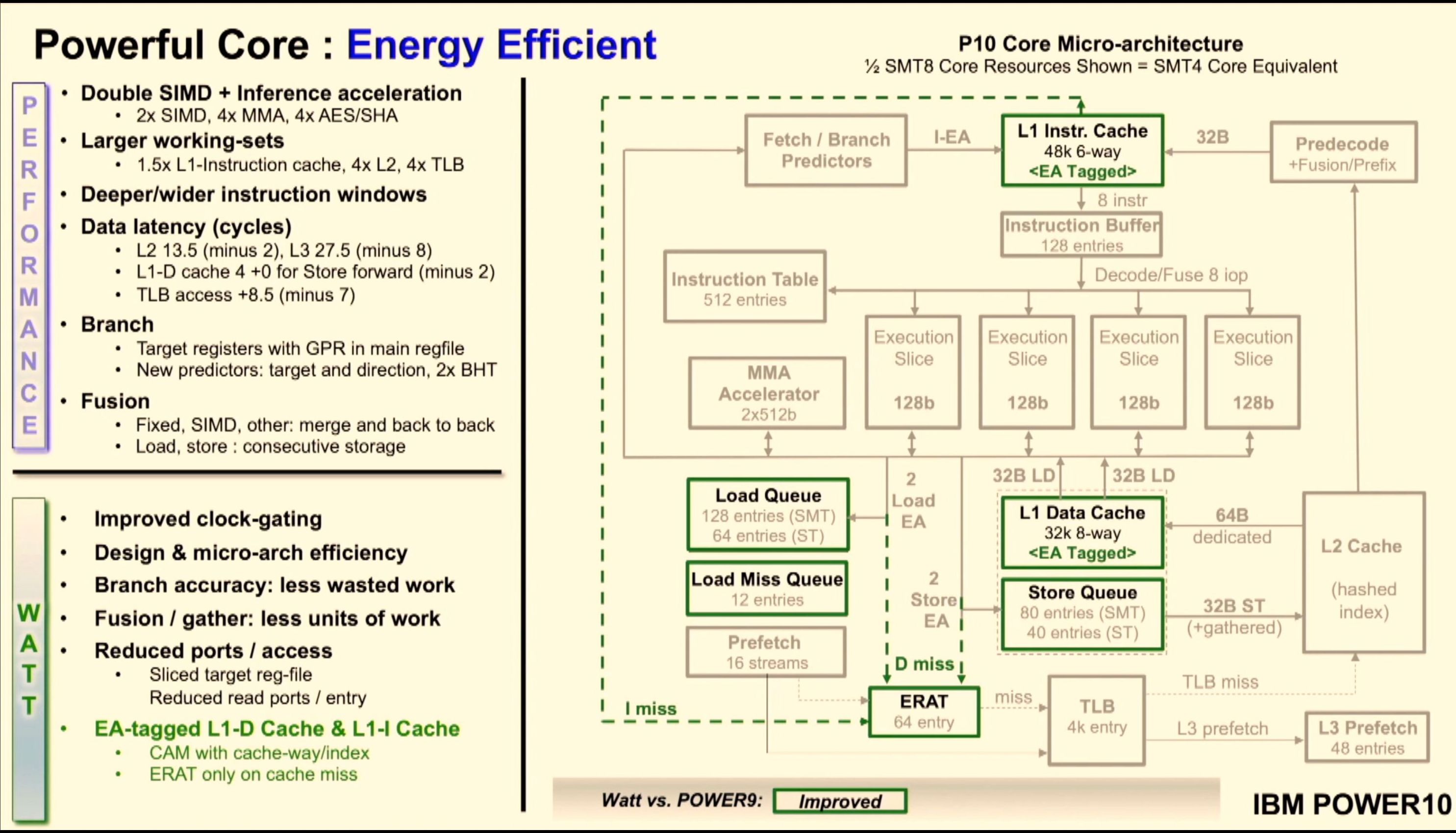

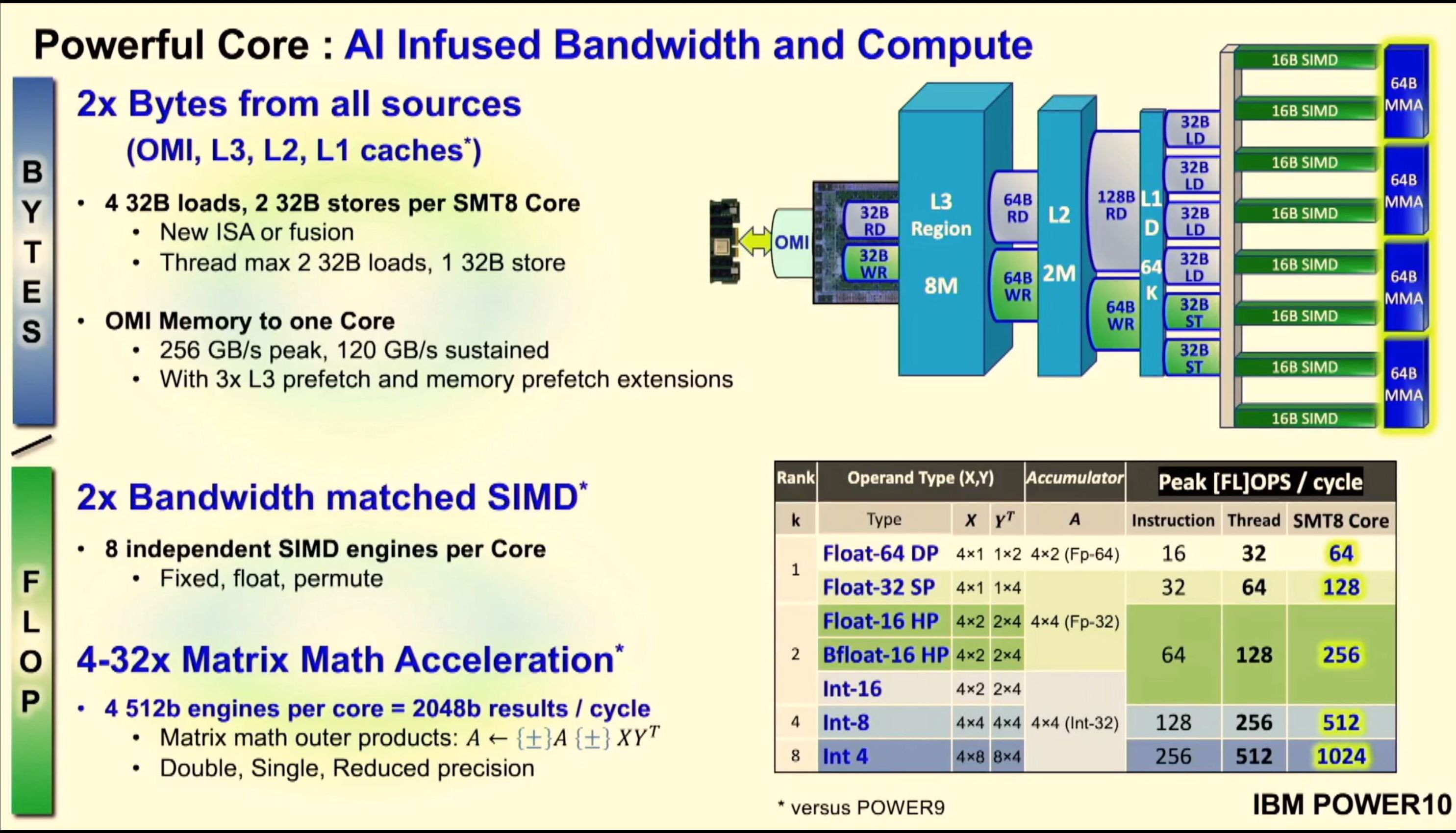

Ein wahres technisches Meisterwerk, der IBM Power10 mit wahlweise 4xSMT oder 8x SMT:

Hier ein schöner Artikel mit den Eckdaten: https://www.nextplatform.com/2020/08/18/ibm-brings-an-architecture-gun-to-a-chip-knife-fight/

Pressemitteilung auf hier auf P3D: https://forum.planet3dnow.de/index....next-generation-ibm-power10-processor.436605/

Hier werden sicherlich auch x86-CPUs für Server von Intel und AMD etwas liefern müssen und sich nicht nur auf den Wettbewerb untereinander konzentrieren dürfen.

Zunächst mal ein schöner Dieshot:

Die Power ISA v3.1 ist von IBM, im Rahmen von OpenPOWER, offengelegt:

ibm.ent.box.com

ibm.ent.box.com

Der Chip hat 18 Mrd. Transistoren auf einer Größe von 602 mm² mit 18 Metal-Layern.

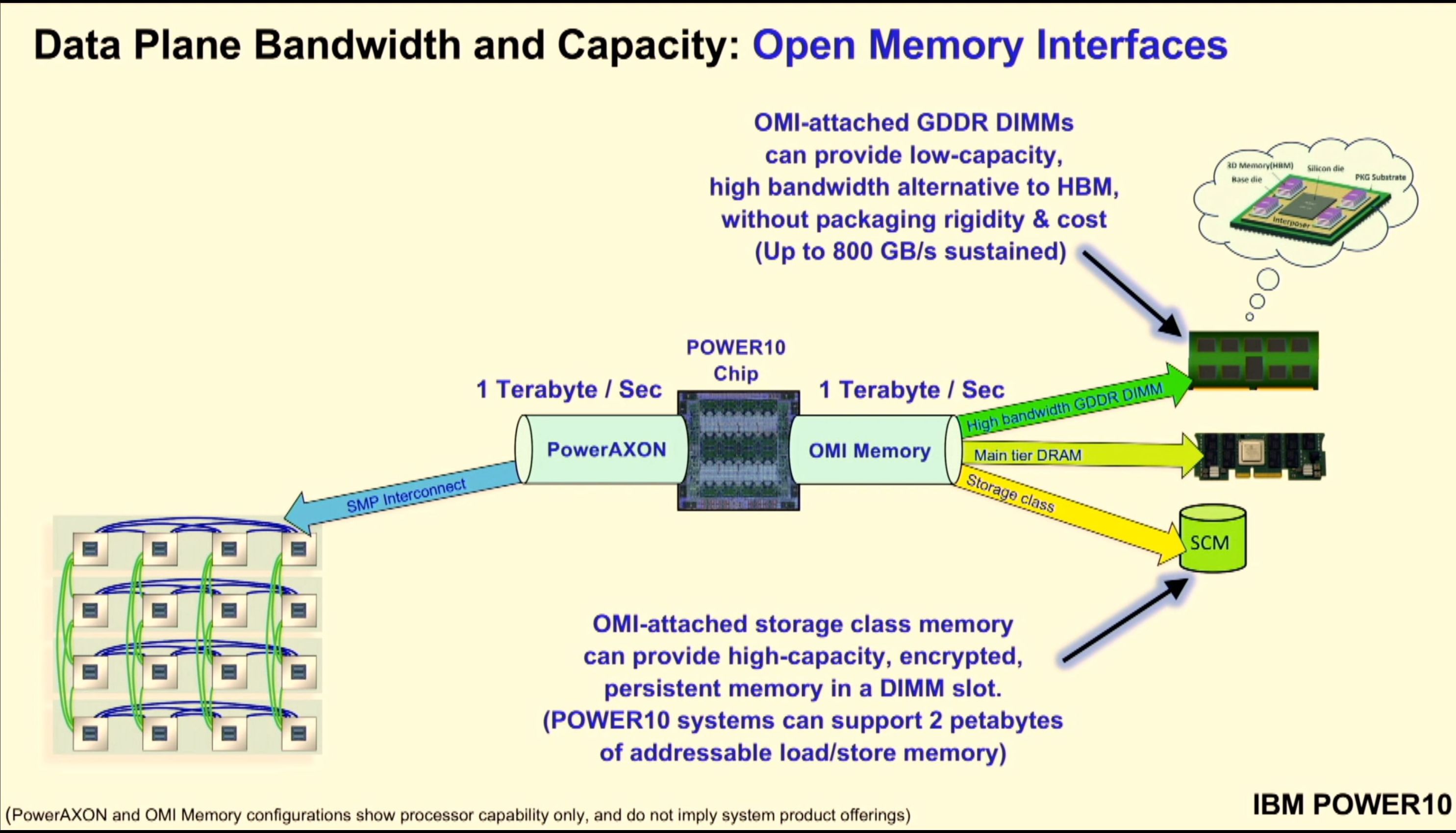

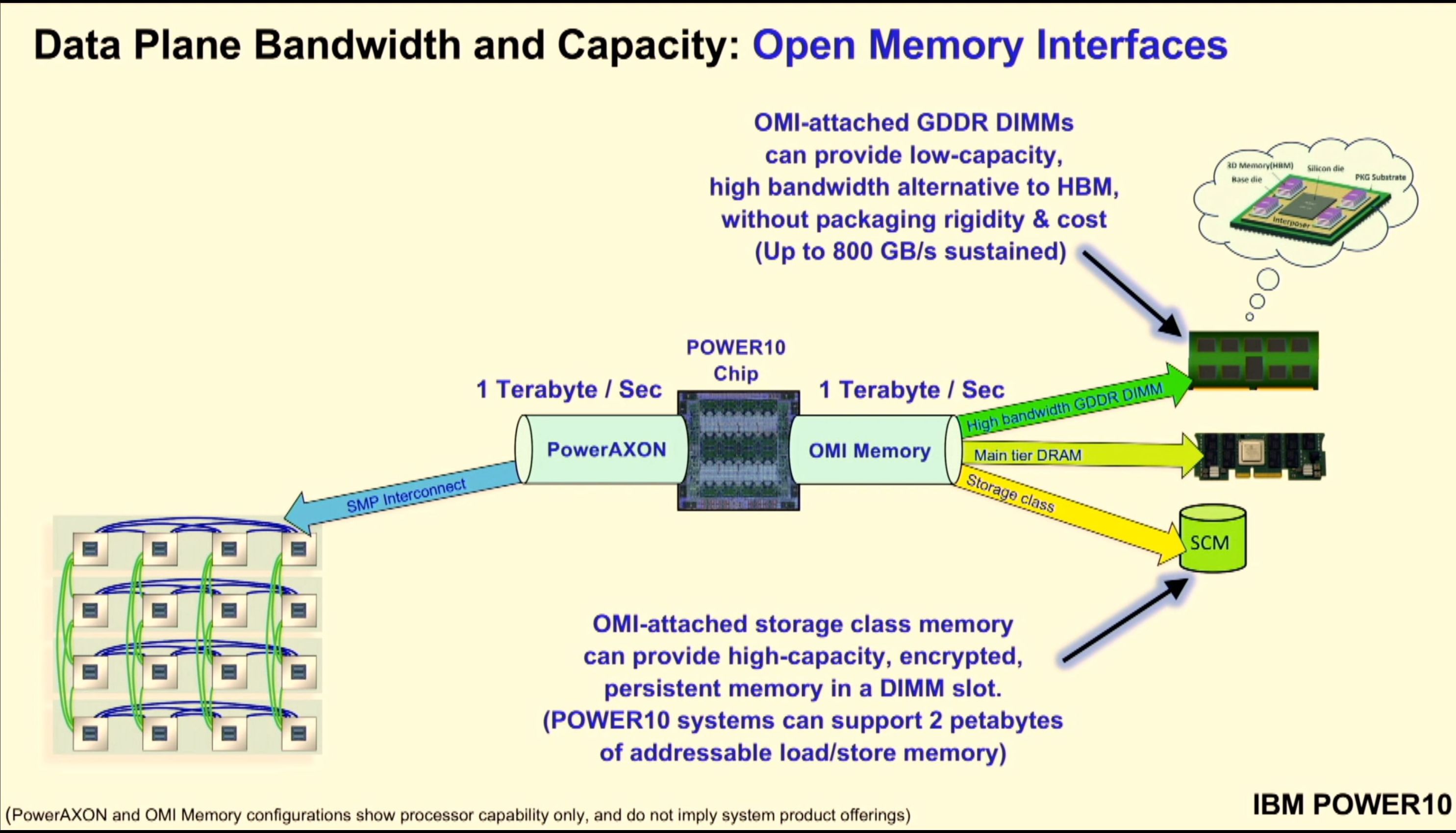

Bietet eine günstige Alternative zu HBM für billigen GDDR-Speicher mit der OMI-Anbindung.

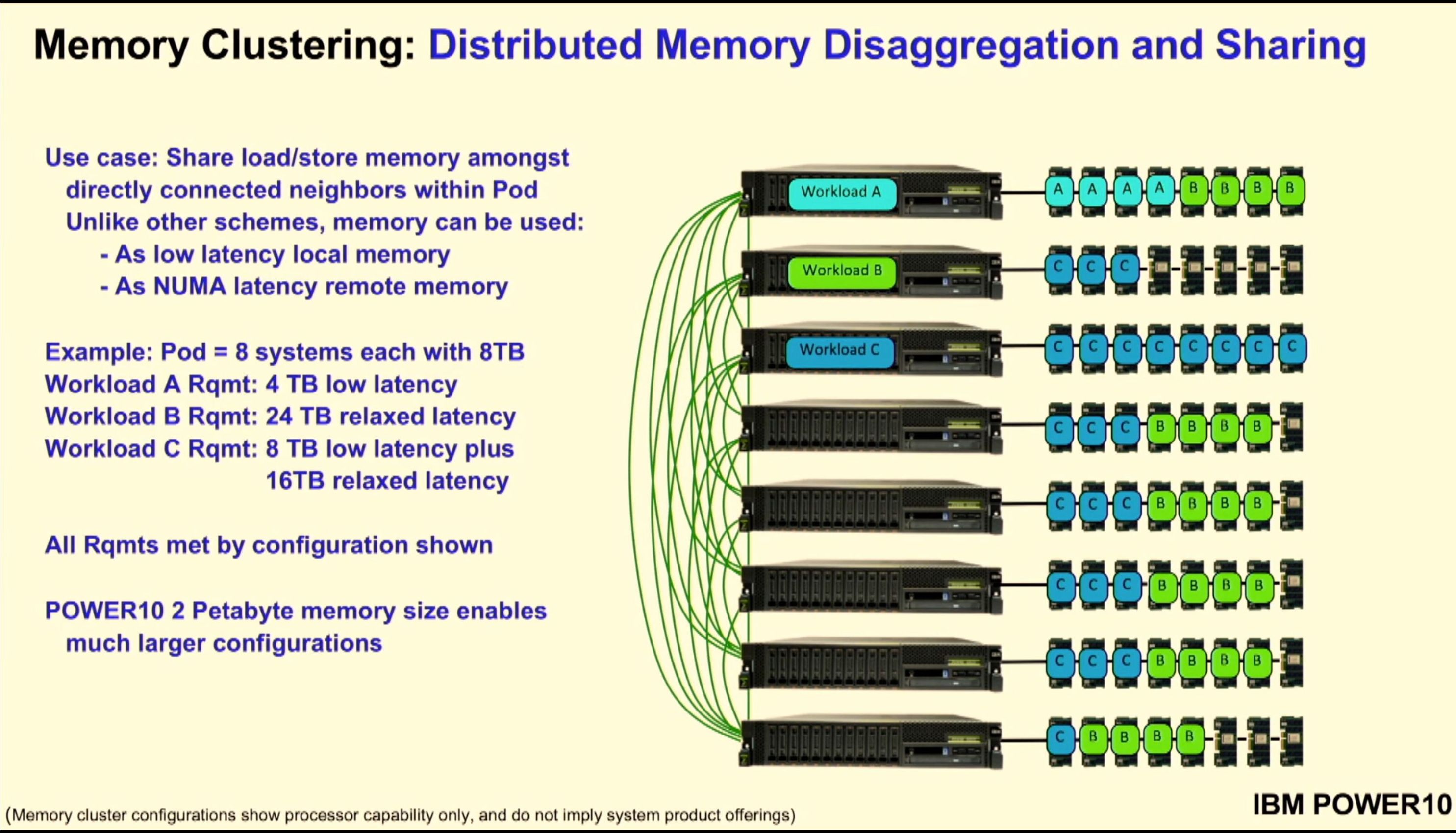

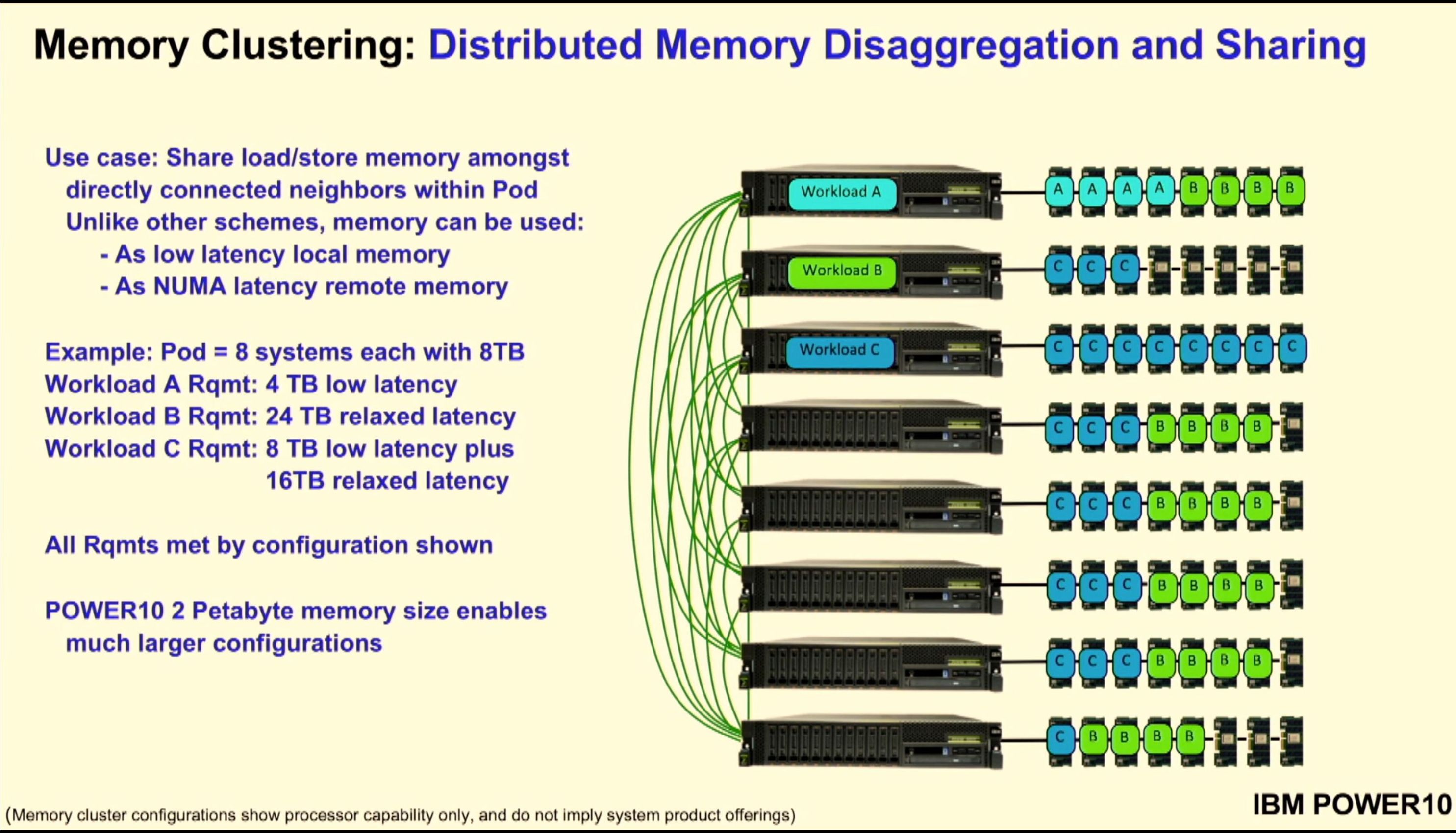

Gemischte Workload-Szenarien mit unterschiedlichen Speicheranforderungen in einem System.

Die Folien stammen aus Anandtechs Liveblog zur Hot Chips 2020:

Hier ein schöner Artikel mit den Eckdaten: https://www.nextplatform.com/2020/08/18/ibm-brings-an-architecture-gun-to-a-chip-knife-fight/

Pressemitteilung auf hier auf P3D: https://forum.planet3dnow.de/index....next-generation-ibm-power10-processor.436605/

Hier werden sicherlich auch x86-CPUs für Server von Intel und AMD etwas liefern müssen und sich nicht nur auf den Wettbewerb untereinander konzentrieren dürfen.

Zunächst mal ein schöner Dieshot:

Die Power ISA v3.1 ist von IBM, im Rahmen von OpenPOWER, offengelegt:

PowerISA_public.v3.1.pdf | Powered by Box

Der Chip hat 18 Mrd. Transistoren auf einer Größe von 602 mm² mit 18 Metal-Layern.

- 15 SMT8 Kerne oder 30 SMT4 Kerne - es gibt 2 Versionen des Chip (oben die STM8 Version)

- 1 SMT8- respektive 2 SMT4-Kerne sind deaktiviert und werden wohl, bei besserer Fertigung, später mit allen Kernen aktiv den Markt erreichen.

Bietet eine günstige Alternative zu HBM für billigen GDDR-Speicher mit der OMI-Anbindung.

Gemischte Workload-Szenarien mit unterschiedlichen Speicheranforderungen in einem System.

Die Folien stammen aus Anandtechs Liveblog zur Hot Chips 2020:

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Bulldozer hatte kein SMT. AMDs erste Erfahrung mit SMT ist Zen.

Bulldozers CMT war anders aufgebaut: https://de.wikipedia.org/wiki/AMD_Bulldozer

Übrigens ist für bestimmte Workloads, die gut mit SMT skalieren, auch ein Vorteil bei den laufenden Kosten verbunden. Software-Lizenzen werden mitlerweile pro Kern berechnet und ein SMT4- oder SMT8-Design zählt auch als 1 Kern. Auf diese Weise spart man Unsummen pro Jahr bei großen Maschinen.

Das bedeute es gibt einen ziemlich großen Faktor im TCO wenn die Software mit einbezogen wird.

Bulldozers CMT war anders aufgebaut: https://de.wikipedia.org/wiki/AMD_Bulldozer

Die von AMD bei Bulldozer eingeführte Clustered-Integer-Core-Architektur wurde ursprünglich von DEC entwickelt und erstmals 1996 mit der RISC-CPU Alpha 21264 vorgestellt.

Das Modul ist ein Kompromiss zwischen echtem Dualcore, wo jedem Thread alle Funktionseinheiten des Prozessorkerns zur Verfügung stehen, und einem Singlecore mit Simultaneous Multithreading (SMT). Das Konzept spart Fläche im Vergleich zum gewöhnlichen Dualcore. Ein Modul ist in verschiedene einfach und doppelt vorhandene Einheiten aufgeteilt, die sich zudem manche Ressourcen teilen. Es hat zwei Integer-Einheiten (Ganzzahl) und eine 256-Bit-Floatingpoint-(Gleitkommazahl)-Einheit, die bei Bedarf in zwei 128-Bit-FPUs aufgeteilt werden kann. Die Fetch-und-Decode-Einheit sind ebenfalls nur einfach vorhanden und teilen die Last auf die jeweiligen Einheiten auf. Ein Modul verfügt über einen 2-MB-Shared-L2-Cache, einen 16-kB-4-Wege-L1-Datacache pro Integercluster und einen 64-kB-2-Wege-L1-Instructionscache. Die beiden unabhängigen Integercluster sind jeweils mit zwei ALUs und zwei AGUs ausgestattet, was maximal vier Arithmetik- und Speicheroperationen pro Modul und Takt erlaubt.[6] Jedes Modul besitzt zwei symmetrische 128-Bit-FMAC-Gleitkommapipelines, die bei Bedarf in eine 256-Bit-breite Einheit umfunktioniert und damit für einen FMA-Befehl verwendet werden können. FMA rundet anders als der Multiply-Add-Befehl erst nach Ende der kompletten Berechnung das Ergebnis. Alle Module einer CPU teilen sich den ggf. vorhandenen L3-Cache sowie das Dual-Channel Interface.

Doppelposting wurde automatisch zusammengeführt:

Übrigens ist für bestimmte Workloads, die gut mit SMT skalieren, auch ein Vorteil bei den laufenden Kosten verbunden. Software-Lizenzen werden mitlerweile pro Kern berechnet und ein SMT4- oder SMT8-Design zählt auch als 1 Kern. Auf diese Weise spart man Unsummen pro Jahr bei großen Maschinen.

Das bedeute es gibt einen ziemlich großen Faktor im TCO wenn die Software mit einbezogen wird.

Zuletzt bearbeitet:

Peet007

Admiral Special

- Mitglied seit

- 30.09.2006

- Beiträge

- 1.884

- Renomée

- 39

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 8700G

- Mainboard

- MSI Mortar B650

- Kühlung

- Wasser

- Speicher

- 32 GB

- Grafikprozessor

- IGP

- Display

- Philips

- Soundkarte

- onBoard

- Netzteil

- 850 Watt

- Betriebssystem

- Manjaro / Ubuntu

- Webbrowser

- Epiphany

Sowas wie eine IF ist nicht verhanden dafür einen 4 mal so großen L2 Cache wie Zen2. 512 kB SMT2 bei 2 MB SMT8. Sehr ähnlich Bin gespannt wie der Vergleich zu Epyc ausfällt wie Leistungsaufnahme unterschiede bei verschiedenen Befehlssätzen, Taktung usw.

Interessant ist für mich auch das man einen 16 Core Die hat, kann durchaus sein das AMD da auch ein 16 Core Chiplet anstrebt.

Interessant ist für mich auch das man einen 16 Core Die hat, kann durchaus sein das AMD da auch ein 16 Core Chiplet anstrebt.

Zuletzt bearbeitet:

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Der Die ist mit über 600mm² in 7nm allerdings etwas groß für ein Chiplet. Allerdings scheint hier die Transistordichte auch nicht besonders hoch zu sein und das könnte dem Samsung Prozess geschuldet sein. 18 Mrd/600 mm² = 30 MTr/mm²

TSMC 7FF liegt bei 96,5 MTr/mm² und 5nm bei 173 MTr/mm²

TSMC 7FF liegt bei 96,5 MTr/mm² und 5nm bei 173 MTr/mm²

[/QUOTE]

Übrigens ist für bestimmte Workloads, die gut mit SMT skalieren, auch ein Vorteil bei den laufenden Kosten verbunden. Software-Lizenzen werden mitlerweile pro Kern berechnet und ein SMT4- oder SMT8-Design zählt auch als 1 Kern. Auf diese Weise spart man Unsummen pro Jahr bei großen Maschinen.

Das bedeute es gibt einen ziemlich großen Faktor im TCO wenn die Software mit einbezogen wird.

[/QUOTE]

Da behaupte ich mal, dass das noch so ist. Ich bin mir ziemlich sicher, dass wenn SMT4/SMT8 in einem Prozessor im Massenmarkt vorhanden ist, dass dann findige Softwarefirmen diese auch als 4-/8-Kerne zählen werden.

Übrigens ist für bestimmte Workloads, die gut mit SMT skalieren, auch ein Vorteil bei den laufenden Kosten verbunden. Software-Lizenzen werden mitlerweile pro Kern berechnet und ein SMT4- oder SMT8-Design zählt auch als 1 Kern. Auf diese Weise spart man Unsummen pro Jahr bei großen Maschinen.

Das bedeute es gibt einen ziemlich großen Faktor im TCO wenn die Software mit einbezogen wird.

[/QUOTE]

Da behaupte ich mal, dass das noch so ist. Ich bin mir ziemlich sicher, dass wenn SMT4/SMT8 in einem Prozessor im Massenmarkt vorhanden ist, dass dann findige Softwarefirmen diese auch als 4-/8-Kerne zählen werden.

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Klar den selben move von Sockel zu Core werden sie sicher auch von Core zu Thread machen, sollte SMT4 und mehr Verbreitung finden.

Peet007

Admiral Special

- Mitglied seit

- 30.09.2006

- Beiträge

- 1.884

- Renomée

- 39

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 8700G

- Mainboard

- MSI Mortar B650

- Kühlung

- Wasser

- Speicher

- 32 GB

- Grafikprozessor

- IGP

- Display

- Philips

- Soundkarte

- onBoard

- Netzteil

- 850 Watt

- Betriebssystem

- Manjaro / Ubuntu

- Webbrowser

- Epiphany

Virtualisierung ist auch ein Thema für solche Maschienen. Gibt ja Anbieter bei denen man sich einen Virtuellen Rechner mieten kann. Kerne, Grafikleistung und Betriebsystem frei wählbar. Wieviel können da gleichzeitig laufen wenn sie dann nur noch SMT Kerne zugewiesen bekommen.

Ähnliche Themen

- Antworten

- 6

- Aufrufe

- 841

- Antworten

- 0

- Aufrufe

- 515

- Antworten

- 0

- Aufrufe

- 509

- Antworten

- 763

- Aufrufe

- 100K

- Antworten

- 413

- Aufrufe

- 81K