App installieren

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: This feature may not be available in some browsers.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Prognose-Board: Wie geht es bei AMD weiter? Entwicklungen / Strategien / Maßnahmen, die AMD betreffen bzw. die AMD treffen könnte

- Ersteller BavarianRealist

- Erstellt am

Onkel_Dithmeyer

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 22.04.2008

- Beiträge

- 12.943

- Renomée

- 4.014

- Standort

- Zlavti

- Aktuelle Projekte

- Universe@home

- Lieblingsprojekt

- Universe@home

- Meine Systeme

- cd0726792825f6f563c8fc4afd8a10b9

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- Ryzen 9 3900X @4000 MHz//1,15V

- Mainboard

- MSI X370 XPOWER GAMING TITANIUM

- Kühlung

- Custom Wasserkühlung vom So. G34

- Speicher

- 4x8 GB @ 3000 MHz

- Grafikprozessor

- Radeon R9 Nano

- Display

- HP ZR30W & HP LP3065

- SSD

- 2 TB ADATA

- Optisches Laufwerk

- LG

- Soundkarte

- Im Headset

- Gehäuse

- Xigmatek

- Netzteil

- BeQuiet Dark Pro 9

- Tastatur

- GSkill KM570

- Maus

- GSkill MX780

- Betriebssystem

- Ubuntu 20.04

- Webbrowser

- Firefox Version 94715469

- Internetanbindung

- ▼100 Mbit ▲5 Mbit

Ich vermute dass es der gleiche ist. Sonst würde man es 2017 zeitlich kaum schaffen.

amdfanuwe

Grand Admiral Special

- Mitglied seit

- 24.06.2010

- Beiträge

- 2.372

- Renomée

- 34

- Details zu meinem Desktop

- Prozessor

- 4200+

- Mainboard

- M3A-H/HDMI

- Kühlung

- ein ziemlich dicker

- Speicher

- 2GB

- Grafikprozessor

- onboard

- Display

- Samsung 20"

- HDD

- WD 1,5TB

- Netzteil

- Extern 100W

- Betriebssystem

- XP, AndLinux

- Webbrowser

- Firefox

- Verschiedenes

- Kaum hörbar

@Onkel_dithmeyer : Wenn alles für Interposer ausgelegt ist, könnte man auch den Speichercontroller und Chipsatz auf einem seperatem Chip fertigen, eventuell sogar in günstigen 40nm oder 28nm.

Ist halt eine reine Kostenfrage, ob viele kleine Chips mit hohem Yield günstiger sind wie mehrere monolitische Chips.

--- Update ---

Wenns der gleiche ist, müssten die CPUs auch mit Interposer kommen.

Ist halt eine reine Kostenfrage, ob viele kleine Chips mit hohem Yield günstiger sind wie mehrere monolitische Chips.

--- Update ---

Wenns der gleiche ist, müssten die CPUs auch mit Interposer kommen.

bschicht86

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 14.12.2006

- Beiträge

- 4.249

- Renomée

- 228

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- 2950X

- Mainboard

- X399 Taichi

- Kühlung

- Heatkiller IV Pure Chopper

- Speicher

- 64GB 3466 CL16

- Grafikprozessor

- 2x Vega 64 @Heatkiller

- Display

- Asus VG248QE

- SSD

- PM981, SM951, ein paar MX500 (~5,3TB)

- HDD

- -

- Optisches Laufwerk

- 1x BH16NS55 mit UHD-BD-Mod

- Soundkarte

- Audigy X-Fi Titanium Fatal1ty Pro

- Gehäuse

- Chieftec

- Netzteil

- Antec HCP-850 Platinum

- Betriebssystem

- Win7 x64, Win10 x64

- Webbrowser

- Firefox

- Verschiedenes

- LS120 mit umgebastelten USB -> IDE (Format wie die gängigen SATA -> IDE)

@Onkel_dithmeyer : Wenn alles für Interposer ausgelegt ist, könnte man auch den Speichercontroller und Chipsatz auf einem seperatem Chip fertigen

Kostensparend wäre es allemal, aber dagegen steht die damit gestiegene Leitungslänge und Latenz, gerade zum Speichercontroller.

BoMbY

Grand Admiral Special

- Mitglied seit

- 22.11.2001

- Beiträge

- 7.468

- Renomée

- 293

- Standort

- Aachen

- Details zu meinem Desktop

- Prozessor

- Ryzen 3700X

- Mainboard

- Gigabyte X570 Aorus Elite

- Kühlung

- Noctua NH-U12A

- Speicher

- 2x16 GB, G.Skill F4-3200C14D-32GVK @ 3600 16-16-16-32-48-1T

- Grafikprozessor

- RX 5700 XTX

- Display

- Samsung CHG70, 32", 2560x1440@144Hz, FreeSync2

- SSD

- AORUS NVMe Gen4 SSD 2TB, Samsung 960 EVO 1TB, Samsung 840 EVO 1TB, Samsung 850 EVO 512GB

- Optisches Laufwerk

- Sony BD-5300S-0B (eSATA)

- Gehäuse

- Phanteks Evolv ATX

- Netzteil

- Enermax Platimax D.F. 750W

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox

ZEN + GPU auf Interposer wurde für 2017 als APU angekündigt, wenn ich nicht irre.

Meine Frage ist: Ist das das der gleiche Chip wie auf den CPUs oder wird es mehrere verschiedene geben?

Aus Kostengründen wäre es vermutlich schlau die normale CPU mit einer normalen GPU auf einem Interposer als APU zu verkaufen. Dadurch wird zwar das eigentliche Produkt ein paar Prozent teurer, aber es spart die komplette Entwicklung eines eigenen Kombi-Chips.

Das hatten wir ja schon länger so spekuliert. Auch Multisource funktioniert dann leichter und man kann die passenden Prozesse für die verschiedenen Chips verwenden.

Eine ähnliche Zielrichtung sieht man z.B. bei Marcells MoChi

Dann wäre Semicustom ein Kinderspiel, v.a. wenn noch HSA von allen Teilen unterstützt wird. Auch dazu passend: Neue HSA Hardware

Eine ähnliche Zielrichtung sieht man z.B. bei Marcells MoChi

Dann wäre Semicustom ein Kinderspiel, v.a. wenn noch HSA von allen Teilen unterstützt wird. Auch dazu passend: Neue HSA Hardware

Opteron

Redaktion

☆☆☆☆☆☆

Aus Kostengründen wäre es vermutlich schlau die normale CPU mit einer normalen GPU auf einem Interposer als APU zu verkaufen. Dadurch wird zwar das eigentliche Produkt ein paar Prozent teurer, aber es spart die komplette Entwicklung eines eigenen Kombi-Chips.

Ja, außerdem kann man dann auch CPUs untereinander verschalten und Opterons mit ~32Kernen auf den Markt bringen.

Bei den K10 gabs auf dem Die auch immer 3-4 Hypertransportanschlüsse. Brauchte man nicht im Desktop,aber soviel machte das nicht aus.

--- Update ---

HSA mit MIPS und PowerVR ... schon witzigDann wäre Semicustom ein Kinderspiel, v.a. wenn noch HSA von allen Teilen unterstützt wird. Auch dazu passend: Neue HSA Hardware

gruffi

Grand Admiral Special

- Mitglied seit

- 08.03.2008

- Beiträge

- 5.393

- Renomée

- 65

- Standort

- vorhanden

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 5 1600

- Mainboard

- MSI B350M PRO-VDH

- Kühlung

- Wraith Spire

- Speicher

- 2x 8 GB DDR4-2400 CL16

- Grafikprozessor

- XFX Radeon R7 260X

- Display

- LG W2361

- SSD

- Crucial CT250BX100SSD1

- HDD

- Toshiba DT01ACA200

- Optisches Laufwerk

- LG Blu-Ray-Brenner BH16NS40

- Soundkarte

- Realtek HD Audio

- Gehäuse

- Sharkoon MA-I1000

- Netzteil

- be quiet! Pure Power 9 350W

- Betriebssystem

- Windows 10 Professional 64-bit

- Webbrowser

- Mozilla Firefox

- Verschiedenes

- https://valid.x86.fr/mb4f0j

IIRC war bei APUs bisher nur von maximal 4 Kernen die Rede. Kann in Zukunft mit kleineren Fertigungsstrukturen aber sicherlich auch mehr werden.ZEN soll als CPU Desktop (4,6,8 Kerne 2 Kanal DDR4 ), für Server (16 Kerne 4Kanal DDR4) und für APU (4,8 Kerne + GPU + HBM + 2Kanal DDR4?) erscheinen.

Opteron

Redaktion

☆☆☆☆☆☆

IIRC war bei APUs bisher nur von maximal 4 Kernen die Rede. Kann in Zukunft mit kleineren Fertigungsstrukturen aber sicherlich auch mehr werden.

Ja, aber bei 14nm sollten 4 Zen Kerne schon reichen. Das wäre schließlich noch zuzüglich SMT. Ggü den 4 Kernen von 2 BD-Modulen der bisherigen APUs wäre das schon ne Steigerung.

Alter Sack

Lt. Commander

- Mitglied seit

- 10.03.2013

- Beiträge

- 143

- Renomée

- 0

- Standort

- Dennheritz

- Details zu meinem Desktop

- Prozessor

- A10-6700

- Mainboard

- Asrock FM A88X Extreme6+

- Kühlung

- Scythe Ninja II

- Speicher

- 8 GB DDR 3 1600 MHz

- Grafikprozessor

- APU

- Display

- 20" Samsung 1680x1050

- SSD

- Samssung Evo 840 256 GB

- HDD

- 1x 2 TB

- Optisches Laufwerk

- DVD-Brenner

- Soundkarte

- Onboard

- Netzteil

- Be Quiet 400W, 80+ Gold

- Betriebssystem

- Win7 x 64, SP1

- Webbrowser

- Opera, Firefox

- Verschiedenes

- Mein Allround-PC, den ich bei Bedarf , durch eine HD7870 aufwerte.

Gegen eine Deskop-GPU auf dem

Interposer spräche für mich der dann

überflüssige Speichercontroller.

Interposer spräche für mich der dann

überflüssige Speichercontroller.

amdfanuwe

Grand Admiral Special

- Mitglied seit

- 24.06.2010

- Beiträge

- 2.372

- Renomée

- 34

- Details zu meinem Desktop

- Prozessor

- 4200+

- Mainboard

- M3A-H/HDMI

- Kühlung

- ein ziemlich dicker

- Speicher

- 2GB

- Grafikprozessor

- onboard

- Display

- Samsung 20"

- HDD

- WD 1,5TB

- Netzteil

- Extern 100W

- Betriebssystem

- XP, AndLinux

- Webbrowser

- Firefox

- Verschiedenes

- Kaum hörbar

Welcher überflüssige Speichercontroller?

Meine aktuelle Vorstellung Betreffs ZEN APU ist dahingehend, dass die GPU mit HBM versorgt wird und die CPU noch über 2 DDR 4 Channels verfügt.

Fiji sollte mit 14/16nm halb so groß ausfallen, da wär noch Platz für die CPU auf dem Interposer.

Dürfte dann aber immer noch 100W für die GPU alleine benötigen (Nano ca. 180W, im neuem Prozess dann etwa 100W.

Da denke ich mehr an einen halben Fiji mit ca. 50 Watt TDP, ca. R-380 X Leistung, 4GB HBM und 4/8 ZEN Kernen. Dürfte Flotter sein als aktuelle Konsolen.

Wäre eine nette APU.

Ich denke auch, dass ab Radeon 470 Interposer verwendet werden, somit die größeren GPUs eh nur noch für Interposer entwickelt werden.

Meine aktuelle Vorstellung Betreffs ZEN APU ist dahingehend, dass die GPU mit HBM versorgt wird und die CPU noch über 2 DDR 4 Channels verfügt.

Fiji sollte mit 14/16nm halb so groß ausfallen, da wär noch Platz für die CPU auf dem Interposer.

Dürfte dann aber immer noch 100W für die GPU alleine benötigen (Nano ca. 180W, im neuem Prozess dann etwa 100W.

Da denke ich mehr an einen halben Fiji mit ca. 50 Watt TDP, ca. R-380 X Leistung, 4GB HBM und 4/8 ZEN Kernen. Dürfte Flotter sein als aktuelle Konsolen.

Wäre eine nette APU.

Ich denke auch, dass ab Radeon 470 Interposer verwendet werden, somit die größeren GPUs eh nur noch für Interposer entwickelt werden.

Alter Sack

Lt. Commander

- Mitglied seit

- 10.03.2013

- Beiträge

- 143

- Renomée

- 0

- Standort

- Dennheritz

- Details zu meinem Desktop

- Prozessor

- A10-6700

- Mainboard

- Asrock FM A88X Extreme6+

- Kühlung

- Scythe Ninja II

- Speicher

- 8 GB DDR 3 1600 MHz

- Grafikprozessor

- APU

- Display

- 20" Samsung 1680x1050

- SSD

- Samssung Evo 840 256 GB

- HDD

- 1x 2 TB

- Optisches Laufwerk

- DVD-Brenner

- Soundkarte

- Onboard

- Netzteil

- Be Quiet 400W, 80+ Gold

- Betriebssystem

- Win7 x 64, SP1

- Webbrowser

- Opera, Firefox

- Verschiedenes

- Mein Allround-PC, den ich bei Bedarf , durch eine HD7870 aufwerte.

Ja gut, wenn HBM nur für die

GPU da sein sollte. Mir würden

schon 1024 Shader und 2 GB

für nicht ganz taufrische Spiele

reichen.

GPU da sein sollte. Mir würden

schon 1024 Shader und 2 GB

für nicht ganz taufrische Spiele

reichen.

amdfanuwe

Grand Admiral Special

- Mitglied seit

- 24.06.2010

- Beiträge

- 2.372

- Renomée

- 34

- Details zu meinem Desktop

- Prozessor

- 4200+

- Mainboard

- M3A-H/HDMI

- Kühlung

- ein ziemlich dicker

- Speicher

- 2GB

- Grafikprozessor

- onboard

- Display

- Samsung 20"

- HDD

- WD 1,5TB

- Netzteil

- Extern 100W

- Betriebssystem

- XP, AndLinux

- Webbrowser

- Firefox

- Verschiedenes

- Kaum hörbar

Ach so meintest du das, dass die CPU vom HBM mitversorgt wird und dann die Speicherkontroller der CPU brachliegen.

Das wäre die Laptopvariante, 4/8GB HBM 2/4 Kerne, kleine GPU (1024+ Shader), eventuell noch mit 128/256GB SSD. Wäre dann der Chip für Mobilgeräte bei denen eh nie einer den Speicher erweitert, weil es sowieso nicht geht.

Das wäre die Laptopvariante, 4/8GB HBM 2/4 Kerne, kleine GPU (1024+ Shader), eventuell noch mit 128/256GB SSD. Wäre dann der Chip für Mobilgeräte bei denen eh nie einer den Speicher erweitert, weil es sowieso nicht geht.

cyrusNGC_224

Grand Admiral Special

- Mitglied seit

- 01.05.2014

- Beiträge

- 5.924

- Renomée

- 117

- Aktuelle Projekte

- POGS, Asteroids, Milkyway, SETI, Einstein, Enigma, Constellation, Cosmology

- Lieblingsprojekt

- POGS, Asteroids, Milkyway

- Meine Systeme

- X6 PII 1090T, A10-7850K, 6x Athlon 5350, i7-3632QM, C2D 6400, AMD X4 PII 810, 6x Odroid U3

- BOINC-Statistiken

Wenn man das aktuelle Gerücht über angeblich (für AMD) knappe HBM Ressourcen bedenkt...

Aber mal eine andere, dumme Frage: Bis jetzt weiß man nur von 3 FinFet Tape-outs. Wie sollen die die nächste Grafikkarten Generation (welche doch mindestens aus 3 versch. Dies besteht) und wenigstens einen ZEN CPU Die abdecken können?

Setzt man etwa wieder auf teilweises rebranding?

Aber mal eine andere, dumme Frage: Bis jetzt weiß man nur von 3 FinFet Tape-outs. Wie sollen die die nächste Grafikkarten Generation (welche doch mindestens aus 3 versch. Dies besteht) und wenigstens einen ZEN CPU Die abdecken können?

Setzt man etwa wieder auf teilweises rebranding?

BoMbY

Grand Admiral Special

- Mitglied seit

- 22.11.2001

- Beiträge

- 7.468

- Renomée

- 293

- Standort

- Aachen

- Details zu meinem Desktop

- Prozessor

- Ryzen 3700X

- Mainboard

- Gigabyte X570 Aorus Elite

- Kühlung

- Noctua NH-U12A

- Speicher

- 2x16 GB, G.Skill F4-3200C14D-32GVK @ 3600 16-16-16-32-48-1T

- Grafikprozessor

- RX 5700 XTX

- Display

- Samsung CHG70, 32", 2560x1440@144Hz, FreeSync2

- SSD

- AORUS NVMe Gen4 SSD 2TB, Samsung 960 EVO 1TB, Samsung 840 EVO 1TB, Samsung 850 EVO 512GB

- Optisches Laufwerk

- Sony BD-5300S-0B (eSATA)

- Gehäuse

- Phanteks Evolv ATX

- Netzteil

- Enermax Platimax D.F. 750W

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox

Es soll wohl drei Arctic Islands geben, Greenland, Baffin und Ellesmere, für das erste Release denke ich mal auf zwei davon beschränkt, jeweils mit Pro und XT Variante. Prinzipiell würde ein CPU-Die mit z.B. 4 Kernen ausreichen, der Rest kann dann per 2.5d Stacking und Selektion erledigt werden. Das würde für eine komplette Reihe an CPU/GPU/APU-Produkten reichen.

hot

Admiral Special

- Mitglied seit

- 21.09.2002

- Beiträge

- 1.187

- Renomée

- 15

- Details zu meinem Desktop

- Prozessor

- AMD Phenom 9500

- Mainboard

- Asrock AOD790GX/128

- Kühlung

- Scythe Mugen

- Speicher

- 2x Kingston DDR2 1066 CL7 1,9V

- Grafikprozessor

- Leadtek Geforce 260 Extreme+

- Display

- Samsung 2432BW

- HDD

- Samsung HD403LJ, Samung SP1614C

- Optisches Laufwerk

- LG HL55B

- Soundkarte

- Realtek ALC890

- Gehäuse

- Zirco AX

- Netzteil

- Coba Nitrox 600W Rev.2

- Betriebssystem

- Vista x64 HP

- Webbrowser

- Firefox

Wahrscheinlich wird es einen 8-Kerner mit L3 und einen 4-Kerne mit oder ohne L3 geben - zudem wird man dann den 4-Kerner auf Raven Ridge einfach mit Ellesmere zusammen mit HBM2 auf einen Interposer platzieren.

Sind dann insgesamt 5 14nm Dies: Die 3 Arctic-Chips einen nativen 4-Kerner und einen nativen 8-Kerner.

Im Serversegment könnte man dann 2 Summit Ridge auf einen Interposer kleben. Längerfristig dürfte man noch an einer big-Chip-GPU arbeiten.

Sind dann insgesamt 5 14nm Dies: Die 3 Arctic-Chips einen nativen 4-Kerner und einen nativen 8-Kerner.

Im Serversegment könnte man dann 2 Summit Ridge auf einen Interposer kleben. Längerfristig dürfte man noch an einer big-Chip-GPU arbeiten.

Zuletzt bearbeitet:

amdfanuwe

Grand Admiral Special

- Mitglied seit

- 24.06.2010

- Beiträge

- 2.372

- Renomée

- 34

- Details zu meinem Desktop

- Prozessor

- 4200+

- Mainboard

- M3A-H/HDMI

- Kühlung

- ein ziemlich dicker

- Speicher

- 2GB

- Grafikprozessor

- onboard

- Display

- Samsung 20"

- HDD

- WD 1,5TB

- Netzteil

- Extern 100W

- Betriebssystem

- XP, AndLinux

- Webbrowser

- Firefox

- Verschiedenes

- Kaum hörbar

Wahrscheinlich wird es einen 8-Kerner mit L3 und einen 4-Kerne mit oder ohne L3 geben

Hätte früher Sinn gehabt. Durch den Interposer verändert sich das alles etwas. Warum nicht einen 4 Kerner mit single Channel DDR4 und L3?

Klebt man 2 davon für Summit Ridge auf einen Interposer und 4/6/8 Stück für den Serverchip.

Raven Ridge bekommt einen + GPU + HBM für günstige single Channel Systeme.

Für ganz billige Systeme gibt es dann einen Teildefekten 2Kerner + teildefekter GPU + HBM ohne DDR4 Speicherinterface.

Oder gar NB+SB+Speicherinterface und L3 Cache auf einen extra Chip?

Der Interposer erlaubt neue Varianten.

Vielleicht auch 2 GPU auf einen Interposer anstatt einen BigChip? Für VR vielleicht nicht ganz so unsinnig.

Wären 3 Chips in 14/16nm + SB/NB/MC.. in 40 oder 28nm um alle xPU Varianten abzudecken.

Zuletzt bearbeitet:

Bobo_Oberon

Grand Admiral Special

- Mitglied seit

- 18.01.2007

- Beiträge

- 5.045

- Renomée

- 190

HBM auf CPU-Produkten halte ich derzeit für suboptimal.

HBM-RAM funktioniert nur deswegen so gut, weil das Interface extrem breit ist - aber der Preis dafür ist extrem geringe Taktfrequenz (HBM1 derzeit max 500 MHz).

Geringer Takt (-> hohe Latenzeit), eher serielle Abarbeitung der CPU-Tasks (gegenüber massiv parallelen Tasks bei GPUs), sprechen GEGEN HBM.

Intel bevorzugt da Hybrid Memory Cube von Systempartner Micron.

Man muss abwarten wie "günstg" AMDs APUs werden, wenn tatsächlich einzelne Module wie CPU-, GPU, L3-Cache, HBM-RAM auf einem Interposer "zusammengeklatscht werden. Noch bin ich nicht davon überzeugt, dass da auch 50 US$-Produkte demnächst (2016/2017) in der Produkt-Pipeline des Athlon-Erfinders vorbereitet werden.

Für den Servermarkt halte ich hingegen schon jetzt CPU/GPU/APU-Produkte mit HBM/HMC für interessant, weil bei entsprechender Rechenpower und gedeckeltem Strombedarf ein Markt da ist.

MFG Bobo (2015)

HBM-RAM funktioniert nur deswegen so gut, weil das Interface extrem breit ist - aber der Preis dafür ist extrem geringe Taktfrequenz (HBM1 derzeit max 500 MHz).

Geringer Takt (-> hohe Latenzeit), eher serielle Abarbeitung der CPU-Tasks (gegenüber massiv parallelen Tasks bei GPUs), sprechen GEGEN HBM.

Intel bevorzugt da Hybrid Memory Cube von Systempartner Micron.

Man muss abwarten wie "günstg" AMDs APUs werden, wenn tatsächlich einzelne Module wie CPU-, GPU, L3-Cache, HBM-RAM auf einem Interposer "zusammengeklatscht werden. Noch bin ich nicht davon überzeugt, dass da auch 50 US$-Produkte demnächst (2016/2017) in der Produkt-Pipeline des Athlon-Erfinders vorbereitet werden.

Für den Servermarkt halte ich hingegen schon jetzt CPU/GPU/APU-Produkte mit HBM/HMC für interessant, weil bei entsprechender Rechenpower und gedeckeltem Strombedarf ein Markt da ist.

MFG Bobo (2015)

Zuletzt bearbeitet:

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Ich denke nicht, dass dies technisch korrekt ist. Zumal mir nicht klar ist ob du meinst HBM hätte höhere Latenz als HMC oder höher als derzeitiger DDR?Geringer Takt (-> hohe Latenzeit), eher serielle Abarbeitung der CPU-Tasks (gegenüber massiv parallelen Tasks bei GPUs), sprechen GEGEN HBM.

Intel bevorzugt da Hybrid Memory Cube von Systempartner Micron.

HBM hat auf jeden Fall kürzere Latenzen als DDR trotz niedrigerdem Takt.

http://www.extremetech.com/computin...-between-wide-io-hbm-and-hybrid-memory-cube/2

Das ist mit HBM auch der Fall.Many of the new standards explicitly allow for multi-threading and simultaneous accesses to different banks of memory which could drastically cut latency on common operations.

http://www.xilinx.com/support/documentation/white_papers/wp456-DDR-serial-mem.pdf

Und für den Consumer Bereich halte ich eine JEDEC-Ratifizierung für zwingend. Intel scheint dies für HMC noch nicht vor zu haben. HBM ist schon JEDEC-Standard.On the engineering design side,of course, HBM latency would be extremely low because the die resides inside the package with the user device

--- Update ---

Ich sehe keine Grund HBM im 50$ Bereich zu benötigen. Da gibt es einen Preisbereich zwischen 100$ und 300$ der mit HBM besser bedient ist. Die kleinen Lowend Produkte werden irgendwann folgen. Zumal man den Speicherpreis auch mit rein rechnen sollte der ja ansonsten separat dazu kommt für die Plattform.Man muss abwarten wie "günstg" AMDs APUs werden, wenn tatsächlich einzelne Module wie CPU-, GPU, L3-Cache, HBM-RAM auf einem Interposer "zusammengeklatscht werden. Noch bin ich nicht davon überzeugt, dass da auch 50 US$-Produkte demnächst (2016/2017) in der Produkt-Pipeline des Athlon-Erfinders vorbereitet werden.

Ich schließe mich hier Complicated an, die 500MHz sehen auf dem Papier nur schlecht aus gegen die "3,6GHz" von DDR4, intern arbeitet aber in beiden nur DRAM:

http://www.extremetech.com/extreme/...g-ddr4-to-3200mhz-improve-overall-performance

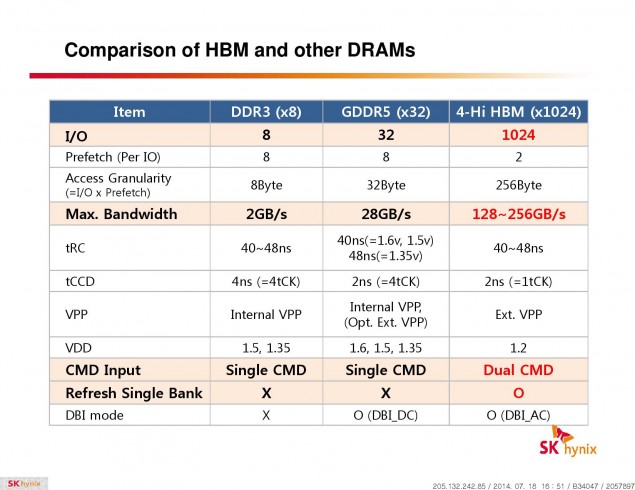

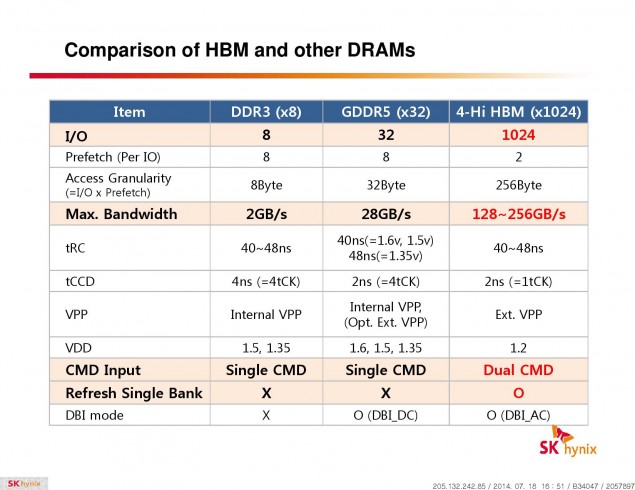

Bzw. auch hier die Latenzen von DDR3 und GDDR5 vs HBM. DDR4 besitzt laut Datenblat auch eine tRC von 40-48ns (skhynix DDR4 Datasheet)

Code besteht In der Regel auch nicht nur aus Sprüngen, da wird einiges sequenziell abgearbeitet, es dürften sich die 1024bit Zugriffe also auch nicht als schlecht erweisen.

Ein weiterer Vorteil von HBM könnte auch sein, dass der gesamte Speicher nicht mehr auf einmal refreshed werden muss, sondern dies blockweise geschehen kann. Wenn sowieso immer andere Threads an anderen Adressen und vermutlich auch Blöcken ausgeführt wird. Ich muss aber zugeben, dass ich nicht weiß, ob DDR4 das auch beherrscht.

http://www.extremetech.com/extreme/...g-ddr4-to-3200mhz-improve-overall-performance

Bzw. auch hier die Latenzen von DDR3 und GDDR5 vs HBM. DDR4 besitzt laut Datenblat auch eine tRC von 40-48ns (skhynix DDR4 Datasheet)

Code besteht In der Regel auch nicht nur aus Sprüngen, da wird einiges sequenziell abgearbeitet, es dürften sich die 1024bit Zugriffe also auch nicht als schlecht erweisen.

Ein weiterer Vorteil von HBM könnte auch sein, dass der gesamte Speicher nicht mehr auf einmal refreshed werden muss, sondern dies blockweise geschehen kann. Wenn sowieso immer andere Threads an anderen Adressen und vermutlich auch Blöcken ausgeführt wird. Ich muss aber zugeben, dass ich nicht weiß, ob DDR4 das auch beherrscht.

amdfanuwe

Grand Admiral Special

- Mitglied seit

- 24.06.2010

- Beiträge

- 2.372

- Renomée

- 34

- Details zu meinem Desktop

- Prozessor

- 4200+

- Mainboard

- M3A-H/HDMI

- Kühlung

- ein ziemlich dicker

- Speicher

- 2GB

- Grafikprozessor

- onboard

- Display

- Samsung 20"

- HDD

- WD 1,5TB

- Netzteil

- Extern 100W

- Betriebssystem

- XP, AndLinux

- Webbrowser

- Firefox

- Verschiedenes

- Kaum hörbar

HBM-RAM funktioniert nur deswegen so gut, weil das Interface extrem breit ist - aber der Preis dafür ist extrem geringe Taktfrequenz (HBM1 derzeit max 500 MHz).

Geringer Takt (-> hohe Latenzeit), eher serielle Abarbeitung der CPU-Tasks (gegenüber massiv parallelen Tasks bei GPUs), sprechen GEGEN HBM.

MFG Bobo (2015)

2 mal Fail.

Der Takt ist so niedrig damit sparsamer gearbeitet werden kann. Durch das breite Interface ergibt sich dennoch eine hohe Bandbreite. Bei HBM ist es möglich mit einem breitem Inteface zu arbeiten, bei "normalem" Ram ist es kaum machbar soviele Leitungen auf dem Board zu verlegen.

Die Latenz, Zugriffszeit bis das erste Byte eintrudelt, ist bei HBM genau so hoch wie bei DDR/2/3. Nicht umsonst werden die Latency Zeiten mit zunehmender Taktfrequenz beim Ram immer größer. Sind intern alles die selben RAM Strukturen.

Zur seriellen Abarbeitung mußte ich auch schmunzeln. Das war einmal. Aktuelle Prozessoren adressieren den Speicher nur noch bei abgeschalteten Caches Byteweise.

Ein Cache pfeift sich immer eine ganze Cacheline rein oder raus, auch wenns nur ein Byte betrifft.

Bei Cachelinegrößen von 64 oder 128Byte sind bei DDR 4 bzw. 8 Takte nötig, bis die Cacheline gefüllt ist. Bei HBM eben nur einen Takt für die 128 Byte.

Durch die Caches eignet sich HBM genauso gut für CPUs wie für GPUs.

Bobo_Oberon

Grand Admiral Special

- Mitglied seit

- 18.01.2007

- Beiträge

- 5.045

- Renomée

- 190

@amdfanuwe

schau mal " ... HBM-RAM funktioniert nur deswegen so gut, weil das Interface extrem breit ist - aber der Preis dafür ist extrem geringe Taktfrequenz ... " -> ich sehe da keinen Widerspruch.

Geringerer Takt = potenziell weniger Interferenzen (was durch mehr Leitungen wieder aufgefressen wird) und potenziell geringere Betriebsspannung.

schau mal " ... eher serielle Abarbeitung der CPU-Tasks (gegenüber massiv parallele ... " -> das ist keine absolute Aussage, sondern eine abschwächende.

MFG Bobo(2015)

schau mal " ... HBM-RAM funktioniert nur deswegen so gut, weil das Interface extrem breit ist - aber der Preis dafür ist extrem geringe Taktfrequenz ... " -> ich sehe da keinen Widerspruch.

Geringerer Takt = potenziell weniger Interferenzen (was durch mehr Leitungen wieder aufgefressen wird) und potenziell geringere Betriebsspannung.

schau mal " ... eher serielle Abarbeitung der CPU-Tasks (gegenüber massiv parallele ... " -> das ist keine absolute Aussage, sondern eine abschwächende.

MFG Bobo(2015)

amdfanuwe

Grand Admiral Special

- Mitglied seit

- 24.06.2010

- Beiträge

- 2.372

- Renomée

- 34

- Details zu meinem Desktop

- Prozessor

- 4200+

- Mainboard

- M3A-H/HDMI

- Kühlung

- ein ziemlich dicker

- Speicher

- 2GB

- Grafikprozessor

- onboard

- Display

- Samsung 20"

- HDD

- WD 1,5TB

- Netzteil

- Extern 100W

- Betriebssystem

- XP, AndLinux

- Webbrowser

- Firefox

- Verschiedenes

- Kaum hörbar

Der Preis dafür ist nicht die geringe Taktfrequenz. Bei HBM 2 gehts ja wieder auf 1GHz. Du solltest nach dem Designziel fragen: Hohe Bandbreite bei geringem Verbrauch.

Bandbreite = Frequenz X Bits, Verbrauch proportional zur Frequenz. Bei Grafikkarten sieht man ja auch, dass bei entsprechendem Aufwand 512 Bit Speicherinterfaces auch mit hoher Frequenz gehen und Quad Channel DDR sind auch nicht grad wenig Leitungen.

Ein großer Vorteil von HBM betrifft auch die Bustreiber. Da diese nur kurze Wege über Interposer treiben müssen, können diese sowohl im HBM als auch auf der GPU entsprechend stromsparender ausgelegt werden.

...eher serielle Abarbeitung trifft es auch nicht ganz, vielleicht eher wahlfreie Speicherzugriffe (Random Access Memory) man weiß halt nie so richtig, welches Byte als nächstes angefordert wird.

man weiß halt nie so richtig, welches Byte als nächstes angefordert wird.

Es bleibt aber dabei, dass HBM gleiche bzw. verbesserte Zugriffszeiten hat und eine Cacheline genauso schnell oder schneller füllt wie herkömmlicher Ram auf dem Board und dabei Energiesparender arbeitet. Erkauft wird sich das ganze dadurch, dass man einen Interposer verwenden muß.

Bandbreite = Frequenz X Bits, Verbrauch proportional zur Frequenz. Bei Grafikkarten sieht man ja auch, dass bei entsprechendem Aufwand 512 Bit Speicherinterfaces auch mit hoher Frequenz gehen und Quad Channel DDR sind auch nicht grad wenig Leitungen.

Ein großer Vorteil von HBM betrifft auch die Bustreiber. Da diese nur kurze Wege über Interposer treiben müssen, können diese sowohl im HBM als auch auf der GPU entsprechend stromsparender ausgelegt werden.

...eher serielle Abarbeitung trifft es auch nicht ganz, vielleicht eher wahlfreie Speicherzugriffe (Random Access Memory)

man weiß halt nie so richtig, welches Byte als nächstes angefordert wird.

man weiß halt nie so richtig, welches Byte als nächstes angefordert wird.Es bleibt aber dabei, dass HBM gleiche bzw. verbesserte Zugriffszeiten hat und eine Cacheline genauso schnell oder schneller füllt wie herkömmlicher Ram auf dem Board und dabei Energiesparender arbeitet. Erkauft wird sich das ganze dadurch, dass man einen Interposer verwenden muß.

Ich sehe keine Grund HBM im 50$ Bereich zu benötigen. Da gibt es einen Preisbereich zwischen 100$ und 300$ der mit HBM besser bedient ist. Die kleinen Lowend Produkte werden irgendwann folgen. Zumal man den Speicherpreis auch mit rein rechnen sollte der ja ansonsten separat dazu kommt für die Plattform.

Letztendlich ist das eine Kostenabwägung: Wieviel kostet HBM incl. Interposer und dem Zusammenbau gegenüber externen RAM und der entsprechenden Platinenfläche und Platinenlagen?

BTW: Wieviele Platinenlagen haben die HBM Grakas gegenüber Grakas mit normalen RAM?

mariahellwig

Grand Admiral Special

AMD hat mit Oculus und, man höre, Dell eine Absichtserklärung unterzeichnet. In Sachen VR kann man AMD wirklich nicht vorwerfen hinterher zu laufen. Da kann man gespannt sein, ob am Ende wie so oft nicht trotzdem die anderen das Geld verdienen.

http://www.amd.com/en-us/press-releases/Pages/amd-partners-with-2015oct05.aspx

http://www.amd.com/en-us/press-releases/Pages/amd-partners-with-2015oct05.aspx

hoschi_tux

Grand Admiral Special

- Mitglied seit

- 08.03.2007

- Beiträge

- 4.760

- Renomée

- 286

- Standort

- Ilmenau

- Aktuelle Projekte

- Einstein@Home, Predictor@Home, QMC@Home, Rectilinear Crossing No., Seti@Home, Simap, Spinhenge, POEM

- Lieblingsprojekt

- Seti/Spinhenge

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen R9 5900X

- Mainboard

- ASUS TUF B450m Pro-Gaming

- Kühlung

- Noctua NH-U12P

- Speicher

- 2x 16GB Crucial Ballistix Sport LT DDR4-3200, CL16-18-18

- Grafikprozessor

- AMD Radeon RX 6900XT (Ref)

- Display

- LG W2600HP, 26", 1920x1200

- HDD

- Crucial M550 128GB, Crucial M550 512GB, Crucial MX500 2TB, WD7500BPKT

- Soundkarte

- onboard

- Gehäuse

- Cooler Master Silencio 352M

- Netzteil

- Antec TruePower Classic 550W

- Betriebssystem

- Gentoo 64Bit, Win 7 64Bit

- Webbrowser

- Firefox

AMD scheint endlich mal Nägel mit Köpfen zu machen und was bis zum Ende durchzuziehen. Die Furys haben sie schon mit VR Gaming beworben, nun legen sie nach.

Jetzt muss sich nur noch VR Gaming durchsetzen

Mir scheint, dass AMD unter Su endlich mal klare Wege einschlägt und weniger auf zig Hochzeiten zugleich tanzen will. Hoffe, das schlägt sich demnächst auch in den Bilanzen nieder.

Jetzt muss sich nur noch VR Gaming durchsetzen

Mir scheint, dass AMD unter Su endlich mal klare Wege einschlägt und weniger auf zig Hochzeiten zugleich tanzen will. Hoffe, das schlägt sich demnächst auch in den Bilanzen nieder.

Ähnliche Themen

- Antworten

- 728

- Aufrufe

- 50K

- Antworten

- 0

- Aufrufe

- 2K

- Antworten

- 0

- Aufrufe

- 1K

- Antworten

- 760

- Aufrufe

- 99K