App installieren

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: This feature may not be available in some browsers.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Was kommt (nach den ersten Deneb (K10.5+)) fuer den Desktop bis zum Launch der BD(APUs)?

- Ersteller TNT

- Erstellt am

rkinet

Grand Admiral Special

http://www.computerbase.de/news/hardware/komplettsysteme/2010/maerz/google_desktop-pcs/Warum solte AMD den K10 nochmals überarbeiten wenn der 2011 von Bulldozer abgelöst wird?

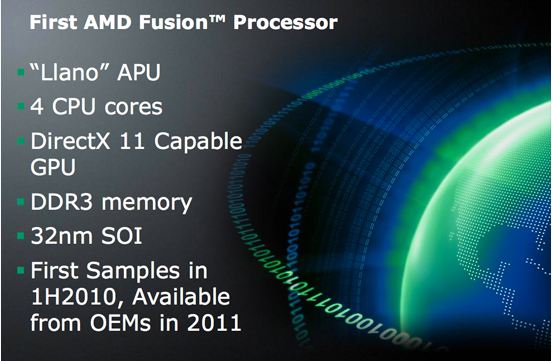

was hat das für ein Sinn? Liano kommt mit IGP in 32nm und basiert auf K10, spät. 2012 wird dann der K10 komplett von BD abgelöst und in Rente geschickt!

Die Performance und die Gerätezahl im Desktop wird lt. Google bald nur noch Randthema sein. Also eine eher kleine Gemeinde die sich viele Cores und aufwendige x86-64 Cores noch zulegen wird.

Vielleicht lebt der K10.5 in der LIano-Socket Infrastruktur viel länger als man heute noch erwartet ?!

Also BD für So. AM3 und K10.5 auch noch in 22nm nach einigen GPU Refresh ?!

mocad_tom

Admiral Special

- Mitglied seit

- 17.06.2004

- Beiträge

- 1.234

- Renomée

- 52

Ich war bloss gerade zu faul dafür zu argumentieren, weil es einfach leichter fällt dagegen zu argumentieren.

Soll sich aber bei mir nicht einschleichen, weil ich das als keinen guten ton empfinde.

BD-Modul-Äquivalent zu Dual-K10.5-Äquivalent müsste also wie folgt aussehen:

BD-Modul(beinhaltet 2 Int-Cores) + 1MB-L2-Cache

(K10.5 + 1MB-L2) x 2

Zusätzlich hinzukommt, dass die Bridge bei einem Okta-Core-K10.5 deutlich größer ausfallen müsste als bei einem 4-BD-Modul-Chip.

Die Bridge des K10.5 benötigt 8 Ports.

Die Bridge des BD benötigt 4 Ports (im Prinzip kann die des Shanghai weiter verwendet werden).

Soll sich aber bei mir nicht einschleichen, weil ich das als keinen guten ton empfinde.

BD-Modul-Äquivalent zu Dual-K10.5-Äquivalent müsste also wie folgt aussehen:

BD-Modul(beinhaltet 2 Int-Cores) + 1MB-L2-Cache

(K10.5 + 1MB-L2) x 2

Zusätzlich hinzukommt, dass die Bridge bei einem Okta-Core-K10.5 deutlich größer ausfallen müsste als bei einem 4-BD-Modul-Chip.

Die Bridge des K10.5 benötigt 8 Ports.

Die Bridge des BD benötigt 4 Ports (im Prinzip kann die des Shanghai weiter verwendet werden).

Triskaine

Lt. Commander

- Mitglied seit

- 19.01.2009

- Beiträge

- 105

- Renomée

- 12

Guter Punkt, aber Stopp! Du hast den L2 beim Llano vergessen.

@Dresdenboy: Die 210 mm² für ein 4-Modul Bulldozer, die du im Januar geschätzt hast, sind zu gering. Wenn wir eine für 32 nm realistische Transistordichte annehmen, so ca. 4,6 - 4,7 Millionen pro mm² (Gulftown liegt übrigens bei 4,71), dann kommen wir bei 210 mm² auf ca. 975 Millionen xtors. Die 16 MB L2+L3 Cache die du veranschlagst (halte ich für eine gute Schätzung

) würden aber bereits 805 Millionen xtors in Beschlag nehmen, da würde höchstens Platz für ein Modul plus Peripherie sein.

) würden aber bereits 805 Millionen xtors in Beschlag nehmen, da würde höchstens Platz für ein Modul plus Peripherie sein. Ich denke das ein 4-Modul Bulldozer sich in der selben Größenordung wie Deneb und Nehalem bewegen wird, also so um die 240-270 mm², anders lässt sich der ganze Kram den er haben wird nicht unterbringen. Damit läge man bei ca. 1200 Millionen xtors.

Llano liegt ja laut AMD bei ~ 1000 Millionen xtors.

gruffi

Grand Admiral Special

- Mitglied seit

- 08.03.2008

- Beiträge

- 5.393

- Renomée

- 65

- Standort

- vorhanden

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 5 1600

- Mainboard

- MSI B350M PRO-VDH

- Kühlung

- Wraith Spire

- Speicher

- 2x 8 GB DDR4-2400 CL16

- Grafikprozessor

- XFX Radeon R7 260X

- Display

- LG W2361

- SSD

- Crucial CT250BX100SSD1

- HDD

- Toshiba DT01ACA200

- Optisches Laufwerk

- LG Blu-Ray-Brenner BH16NS40

- Soundkarte

- Realtek HD Audio

- Gehäuse

- Sharkoon MA-I1000

- Netzteil

- be quiet! Pure Power 9 350W

- Betriebssystem

- Windows 10 Professional 64-bit

- Webbrowser

- Mozilla Firefox

- Verschiedenes

- https://valid.x86.fr/mb4f0j

L2 nicht vergessen.Angenommen ein BD-Modul mit 2 Int-Core ist also 24mm^2 groß - wo wäre dann der Vorteil zu zwei K10.5-Kerne - die sind 9.7mm^2 * 2 = 19.4mm^2 groß

Ein K10.5 Kern inklusive L2 braucht ~20 mm², zwei davon ~40 mm, dies auf 32 nm geshrinkt ~25 mm². Wäre also eine vergleichbare Grösse zu einem Bulldozer Modul. Nur, ein Bulldozer Kern kann auf viermal so viel L2 zugreifen, 2 Kerne eines Moduls immer noch auf doppelt so viel L2. Ein Bulldozer Kern wird sicherlich auch um einiges effizienter arbeiten. Und damit meine ich nicht nur höhere Taktraten bei gleicher TDP, sondern ich gehe auch von mehr IPC aus.

Ein K10.5 Kern inklusive L2 braucht ~20 mm², zwei davon ~40 mm, dies auf 32 nm geshrinkt ~25 mm². Wäre also eine vergleichbare Grösse zu einem Bulldozer Modul. Nur, ein Bulldozer Kern kann auf viermal so viel L2 zugreifen, 2 Kerne eines Moduls immer noch auf doppelt so viel L2. Ein Bulldozer Kern wird sicherlich auch um einiges effizienter arbeiten. Und damit meine ich nicht nur höhere Taktraten bei gleicher TDP, sondern ich gehe auch von mehr IPC aus.Gehe mal von einer höheren Transistordichte bei AMD aus. Ältere Zahlen von Hans de Vries deuten jedenfalls darauf hin. 240-270 mm² erscheinen mir zu viel. Dann würde der 8-Kerner wieder deutlich über 300 mm² liegen. Ich denke eher, AMD wird das nicht wollen. Vor allem, da sie 2 von diesen Chips in ein Package für Interlagos bekommen wollen. 16 MiB L2+L3 erscheinen mir für einen 4-Kerner auch zu viel. Ausser T-RAM kommt schon zum Einsatz. Dann ist das mit bisherigen Zahlen aber sowieso nicht mehr vergleichbar. 2x 2 MiB L2 + 8 MiB L3 (= 12 MiB) erscheint mir bei einem 4-Kerner irgendwie "runder". Ich könnte mir den 4-Kerner auch völlig ohne L3 vorstellen.Wenn wir eine für 32 nm realistische Transistordichte annehmen, so ca. 4,6 - 4,7 Millionen pro mm² (Gulftown liegt übrigens bei 4,71)

Zuletzt bearbeitet:

Meine Daten eingesetzt in deinen Text, schon für 32 nm BD (mit Llano-Core als Basis) und mit Kommentaren:

...

- 12.5 mm² for 2 MB L2

(dank dieser Größe sind wir doch noch bei recht ähnlichen Werten gelandet)

Summe: 24.6 mm²

Warum benötigt ein Bulldozer 2 MB L2 ?

Ein Propus hat pro Kern auch nur 512 KB L2, wo ein Integer-Kern und eine FPU dran hängt und die Performance-Einbrüche wegen fehlendem L3 liegen ja AFAIK nur bei 3%

Sollte beim Bolldozer nicht auch ein 512 KB L2 pro Integer-Kern reichen, wo eben auch die FPU dranhängt.

Hört sich nicht ein Bulldozer mit 1MB L2 & nur 18mm" bzw. 25% geringerer Größe bei vielleicht nur 3-5% Performance-Verlust nicht attraktiver an

??

??Oder wo ist der denkfehler?

Zuletzt bearbeitet:

VlaDeZ

Lieutnant

- Mitglied seit

- 29.05.2009

- Beiträge

- 83

- Renomée

- 2

Ich habe nicht wirklich Ahnung von all´ dem hier (lese nur immer mit^^) , aber ich denke mal, dass es bei einem hochtaktendem Design, was der Bulldozer wohl werden dürfte, von Vorteil ist, viel L2 Chache zu besitzen.

Stichwort BruteForce?

Stichwort BruteForce?

Opteron

Redaktion

☆☆☆☆☆☆

Warum benötigt ein Bulldozer 2 MB L2 ?

Ein Propus hat pro Kern auch nur 512 KB L2, wo ein Integer-Kern und eine FPU dran hängt und die Performance-Einbrüche wegen fehlendem L3 liegen ja AFAIK nur bei 3%

Sollte beim Bolldozer nicht auch ein 512 KB L2 pro Integer-Kern reichen, wo eben auch die FPU dranhängt.

Hört sich nicht ein Bulldozer mit 1MB L2 & nur 18mm" bzw. 25% geringerer Größe bei vielleicht nur 3-5% Performance-Verlust nicht attraktiver an??

Oder wo ist der denkfehler?

2 MB = Optimum

Ich sag mal so, AMD wird entsprechende Simulationen gemacht haben.

Ich habe in meiner persönlichen Pi*Daumen Abschätzung das Preis/Leistungs L2 Maximum ebenfalls auf 2 MB taxiert.

Grund hierfür waren Beobachtungen bei den Intels, die verlieren mit weniger als 2 MB Cache schon sehr stark an Leistung. Teilweise gibts auch schon größere Unterschiede zw. den 2 und 3 MB Typen.

Das Ganze ist zwar eine sehr unscharfe Angelegenheit, da bei Intels L2 Designs neben der Größe gleichzeitig auch die Assoziativität abnimmt, aber ich hab da mal trotzdem das Fazit für mich gezogen, dass 2MB mit etwas höherer Assoziativität als die Intels ein guter Kompromiss wäre, z.B. 2MB / 16fach. (Die Intels haben bei 2 MB 8fach).

Abgesehen davon bin ich schon von Anfang an ein Kritiker der kleinen Intel L2 Caches, Meiner Meinung nach wären die mit mehr L2 noch besser, aber mangels Nehalem Design mit großem L2 kann ichs nicht beweisen. Intel hat die meines Erachtens so gewählt, da Nehalem v.a. ein Server Design ist, und sie sich deswegen für Inclusive Caches entschieden haben, was wiederum keine große L2 Caches zuläßt.

Entlastung des L3 Caches / RAM Zugriffe.

Mit BD wird einiges an "Druck" zugelegt, 8 Kerne verursachen eine höhere Last als 4, da träfe es sich gut die Speicheranfragen innerhalb eines Moduls halten zu können, v.a. auch wenn der L3 (deutlich) langsamer taktet.

Höhere Anforderungen aufgrund kleiner L1 Caches

Wenn die L1 wirklich nur 16kB groß werden, dann häufen sich die Anfragen auf den L2. Das muss man beim Vergleich mit dem K10 beachten. Dort puffern die fast schon riesigen L1 Caches mit 64k schon ziemlich viel weg.

Vielleicht hast Du gar keinen Denkfehler

Vielleicht ist die Info aus dem AMD Compiler einfach falsch, ein Restrisiko besteht noch, aber ich sehe es aufgrund der ganze Umstände (es wurde ja erwähnt, dass sie AMD Dokumente zur Verfügung hatten) als relativ gesichert bei ca. 95%.

@Dresdenboy:

Hast Du bei Deiner Kalkulation eigentlich auch irgendwo den L0 Cache (RRC) mit dabei ? Wäre wohl um die 8kB.

ciao

Alex

Zuletzt bearbeitet:

Triskaine

Lt. Commander

- Mitglied seit

- 19.01.2009

- Beiträge

- 105

- Renomée

- 12

240-270 mm² erscheinen mir zu viel. Dann würde der 8-Kerner wieder deutlich über 300 mm² liegen. Ich denke eher, AMD wird das nicht wollen. Vor allem, da sie 2 von diesen Chips in ein Package für Interlagos bekommen wollen. 16 MiB L2+L3 erscheinen mir für einen 4-Kerner auch zu viel. Ausser T-RAM kommt schon zum Einsatz. Dann ist das mit bisherigen Zahlen aber sowieso nicht mehr vergleichbar. 2x 2 MiB L2 + 8 MiB L3 (= 12 MiB) erscheint mir bei einem 4-Kerner irgendwie "runder". Ich könnte mir den 4-Kerner auch völlig ohne L3 vorstellen.

Die Rede ist von einem 4-Modul Bulldozer, den kannst du auch von mir aus Octo Core nennen. Mit 240-270 mm² würden zwei von denen locker in ein G34 Package passen, es passen ja schließlich auch zwei istanbul mit je 346 mm² rein.

Einen 8-Modul Bulldozer wird es hingegen nicht geben. Die 2 MB L2 Cache stammen aus den Compiler Leaks die hier vor ein paar Wochen rumgingen. Wenn schon der L2 Cache so groß ist, macht es wenig Sinn einen kleineren (pro Core)-L3 Cache zu verbauen.

Duplex

Admiral Special

@Triskaine

Für Server kommt Interlagos mit 16 Kernen

http://www.hardwareboard.eu/showthr...ulldozer-die-n%E4chste-AMD-Generation-in-2011

Die machen mir Angst...

Für Server kommt Interlagos mit 16 Kernen

http://www.hardwareboard.eu/showthr...ulldozer-die-n%E4chste-AMD-Generation-in-2011

AMD selber bezeichnet Bulldozer als "leistungsfähigsten Single- und Multi-Thread-Prozessorkern der Geschichte"

Die machen mir Angst...

Zuletzt bearbeitet:

WindHund

Grand Admiral Special

- Mitglied seit

- 30.01.2008

- Beiträge

- 12.224

- Renomée

- 536

- Standort

- Im wilden Süden (0711)

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- NumberFields@home

- Lieblingsprojekt

- none, try all

- Meine Systeme

- RYZEN R9 3900XT @ ASRock Taichi X570 & ASUS RX Vega64

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5950X

- Mainboard

- ASRock 570X Taichi P5.05 Certified

- Kühlung

- AlphaCool Eisblock XPX, 366x40mm Radiator 6l Brutto m³

- Speicher

- 2x 16 GiB DDR4-3600 CL26 Kingston (Dual Rank, unbuffered ECC)

- Grafikprozessor

- 1x ASRock Radeon RX 6950XT Formula OC 16GByte GDDR6 VRAM

- Display

- SAMSUNG Neo QLED QN92BA 43" up to 4K@144Hz FreeSync PP HDR10+

- SSD

- WD_Black SN850 PCI-Express 4.0 NVME

- HDD

- 3 Stück

- Optisches Laufwerk

- 1x HL-DT-ST BD-RE BH10LS30 SATA2

- Soundkarte

- HD Audio (onboard)

- Gehäuse

- SF-2000 Big Tower

- Netzteil

- Corsair RM1000X (80+ Gold)

- Tastatur

- Habe ich

- Maus

- Han I

- Betriebssystem

- Windows 10 x64 Professional (up to date!)

- Webbrowser

- @Chrome.Google & Edge Chrome

@Triskaine

Für Server kommt Interlagos mit 16 Kernen

http://www.hardwareboard.eu/showthr...ulldozer-die-n%E4chste-AMD-Generation-in-2011

Die machen mir Angst...

Danke für den Link!

Hier noch ein Auszug:

Doch die letzte und gleichzeitig größte Neuerung der Bulldozer Architektur ist das AMD Fusion Konzept, was Bulldozer dann zu einer APU macht (GPU und CPU auf einem Die). Dort kommt eine eigenständige GPU zum Einsatz, der AMD es erlaubt, der CPU Arbeit abzunehmen.

Bei Bulldozer werden Floating-Point-Verarbeitung nun anstatt von der CPU (über die 128-Bit FPU), von der GPU ausgeführt, die bei solchen Verarbeitungen eine deutlich höhere Performance bringen soll.

Das erinnert irgendwie an die PhysX Technik (der CPU Rechenarbeit abnehmen)

Wenn das aber auch von normaler Software genutzt werden kann (Office, Multi-Media, etc.) dann ist das Zitat von dir nicht zuweit hergeholt!

Markus Everson

Grand Admiral Special

Zitat: "AMD hat gestern neue Folien VÖ, die näher auf den kommenden Phenom II Nachfolger Llano auf Bulldozer Architektur eingehen."

Llano auf Bulldozer Architektur...?

[Edith]

"Im Idle soll die CPU gar nur 25 Watt verbrauchen, was sich sehr vielversprechend anhört."

Habe ich was nicht mitbekommen und die Seite will so ne Art Satire darstellen?

Zuletzt bearbeitet:

Dr@

Grand Admiral Special

- Mitglied seit

- 19.05.2009

- Beiträge

- 12.791

- Renomée

- 4.066

- Standort

- Baden-Württemberg

- Aktuelle Projekte

- Collatz Conjecture

- Meine Systeme

- Zacate E-350 APU

- BOINC-Statistiken

- Mein Laptop

- FSC Lifebook S2110, HP Pavilion dm3-1010eg

- Details zu meinem Laptop

- Prozessor

- Turion 64 MT37, Neo X2 L335, E-350

- Mainboard

- E35M1-I DELUXE

- Speicher

- 2x1 GiB DDR-333, 2x2 GiB DDR2-800, 2x2 GiB DDR3-1333

- Grafikprozessor

- RADEON XPRESS 200m, HD 3200, HD 4330, HD 6310

- Display

- 13,3", 13,3" , Dell UltraSharp U2311H

- HDD

- 100 GB, 320 GB, 120 GB +500 GB

- Optisches Laufwerk

- DVD-Brenner

- Betriebssystem

- WinXP SP3, Vista SP2, Win7 SP1 64-bit

- Webbrowser

- Firefox 13

welche folien?

woher kommt das zitat?

@Duplex

Triskaine Aussage zu den 4 Modulen war schon richtig! Interlagos wird wie heute Magny-Cours aus zwei Dies bestehen. Jeder Die wird 4 Module, also 8 Integerkerne, besitzen. Insgesamt wird der Interlagos dann mit 12 bis 16 Kernen verkauft.

MfG @

Edit: Irgendwie geht der Link in Markus Everson Post wo anders hin, als der im Originalpost.

@Duplex

Triskaine Aussage zu den 4 Modulen war schon richtig! Interlagos wird wie heute Magny-Cours aus zwei Dies bestehen. Jeder Die wird 4 Module, also 8 Integerkerne, besitzen. Insgesamt wird der Interlagos dann mit 12 bis 16 Kernen verkauft.

MfG @

Edit: Irgendwie geht der Link in Markus Everson Post wo anders hin, als der im Originalpost.

Zuletzt bearbeitet:

Doch die letzte und gleichzeitig größte Neuerung der Bulldozer Architektur ist das AMD Fusion Konzept, was Bulldozer dann zu einer APU macht (GPU und CPU auf einem Die). Dort kommt eine eigenständige GPU zum Einsatz, der AMD es erlaubt, der CPU Arbeit abzunehmen.

Bei Bulldozer werden Floating-Point-Verarbeitung nun anstatt von der CPU (über die 128-Bit FPU), von der GPU ausgeführt, die bei solchen Verarbeitungen eine deutlich höhere Performance bringen soll.

Irgentwie steht Dein Zitat im Widerspruch zu dem was hier ca. 20 Seiten mindestens 100mal geschrieben wurde.

Ein Bulldozer Modul hat eine 256 bit FPU also ist die Aussage schon mal kompletter Unsinn. BD hat auch erstmal überhaupt nichts mit einer GPU zu tun. Hier hat der Schreiberling Llano und BD bunt durcheinander geworfen. Wahrscheinlich ging er davon aus das LLano einen BD Kern haben wird, was aber wie wir seit der ISCC wissen, nicht der Fall ist. Also einfach nochmal die letzten 20 Seiten durchlesen.

Kurz nochmal eine Zusammenfassung, es kommen drei neue Architekturen 2011:

1. Llano: Ein APU mit 4 K10 Kernen integrierter GPU in 32 nm. Die Plattformen sind Lynx (Dekstop) bzw. Sabine (Notebook).

2. Bulldozer: Bezeichnet einen neuen Kern/Modul, der aus zwei Integer Kernen und einer 256 bit FPU besteht. Ob BD mal in Zukunft 2-4 BD Module mit einer GPU verheiratet ist anzunehmen, aber noch nicht auf der veröffentlichten Roadmap. Der erste Chip mit 4 Modulen ist Zambezi für den Dektop bzw. Valencia für Server. Zwei solche Chips werden zu einem Interlagos (2 Dies x 4 Module x 2 INT Kerne = 16 Kerne) verpackt werden. Die Plattformbezeichnungen lass ich jetzt mal weg. Produziert wird in 32nm.

3. Bobcat: Neuer kleiner K8 basierender Kern, ultrasparsam, ultrakompakt. Er wird sicherlich nur verheiratet mit einer GPU auf den Markt kommen um den Netbook Ultra-Thin Notebook-Markt aufzuräumen. Der erste Chip ist Ontario mit 2 Kernen und GPU. Die Plattform nennt sich Brazos. Interessant ist wie und wo der hergestellt wird. Auf den Folien vom Analysten-Tag ist er komischerweise grau hinterlegt und nicht grün (45nm) oder rot (32nm).

Gruß S.

Dr@

Grand Admiral Special

- Mitglied seit

- 19.05.2009

- Beiträge

- 12.791

- Renomée

- 4.066

- Standort

- Baden-Württemberg

- Aktuelle Projekte

- Collatz Conjecture

- Meine Systeme

- Zacate E-350 APU

- BOINC-Statistiken

- Mein Laptop

- FSC Lifebook S2110, HP Pavilion dm3-1010eg

- Details zu meinem Laptop

- Prozessor

- Turion 64 MT37, Neo X2 L335, E-350

- Mainboard

- E35M1-I DELUXE

- Speicher

- 2x1 GiB DDR-333, 2x2 GiB DDR2-800, 2x2 GiB DDR3-1333

- Grafikprozessor

- RADEON XPRESS 200m, HD 3200, HD 4330, HD 6310

- Display

- 13,3", 13,3" , Dell UltraSharp U2311H

- HDD

- 100 GB, 320 GB, 120 GB +500 GB

- Optisches Laufwerk

- DVD-Brenner

- Betriebssystem

- WinXP SP3, Vista SP2, Win7 SP1 64-bit

- Webbrowser

- Firefox 13

An eurer Stelle würde ich den Artikel Thread aus dem die Zitate stammen vollständig aus meinem Gehirn löschen!

Zuletzt bearbeitet:

Und für die kommenden Nile/Danube-Plattformen verspricht AMD ja +25% mehr Akkulaufzeit und ebensoviel mehr Performance => also müssen dessen 45nm-K10.5 was mehr können, als die aktuellen => demnach muss es sich wohl um überarbeitete Regors/Propus-Dice handeln.

Die Aussagen beziehen sich auf den Neo. Der ist ein etwas betagter 65nm Dualcore also ein BH-G2 (sowas habe ich seit Jahren in meinem Desktop als BE2400). Die 45 nm C3 Regors (DA-C3) sollten da schon einiges besser sein. Schliesslich gibt es ja schon den Athlon X2 240e mit 45W bei 2,8 GHz. Warum soll da kein Low Power Mobile mit 2GHz und weniger als 20W möglich sein.

Gruß S.

Aha, dann dürfte sich der Performance-Einbruch von 2x512 kb L2 statt 2x1024 MB L2 doch etwas stärker auswirken als ich gedacht hatte.2 MB = Optimum

Ich sag mal so, AMD wird entsprechende Simulationen gemacht haben.

Ich habe in meiner persönlichen Pi*Daumen Abschätzung das Preis/Leistungs L2 Maximum ebenfalls auf 2 MB taxiert.

Grund hierfür waren Beobachtungen bei den Intels, ...

Ich kannte ja nur den (genauen) Wert von AMD, nicht von Intel.

Prinzipel darf man nicht vergessen, dass bei einem Modul mit 2x512 kB zwar 25% weniger Core-Fläche bedeutet, aber damit würde z.B. ein 2 Modul-Bulldozer-Die ohne L3, ich schätze mal, eine nur 10-20% gesamte Die-Größe bedeuten.

Da war meine darstellung mit -25% ziemlich verzerrt.

Na ja, 8-Core-Bulldozer kommt mit 32nm, wo man wieder den L3-Cache verdoppeln könnte, ohne die Fläche im Vergleich zum Vergänger vergrößern zu müssen.Entlastung des L3 Caches / RAM Zugriffe.

Mit BD wird einiges an "Druck" zugelegt, 8 Kerne verursachen eine höhere Last als 4, da träfe es sich gut die Speicheranfragen innerhalb eines Moduls halten zu können, v.a. auch wenn der L3 (deutlich) langsamer taktet.

Ich dachte, der kleinere aber schnellere bzw assozierierte L1-Cache wäre sogar schneller.Höhere Anforderungen aufgrund kleiner L1 Caches

Wenn die L1 wirklich nur 16kB groß werden, dann häufen sich die Anfragen auf den L2. Das muss man beim Vergleich mit dem K10 beachten. Dort puffern die fast schon riesigen L1 Caches mit 64k schon ziemlich viel weg.

Wenn ich es richtig in erinnerung haben, ist die Einsparung des L1-Cache (deutilch) geringer als der zusätzliche L2-Cache, weil der L1-65-kb-Cache AFAIK 50% der Fläche vo 512-kb-L2-Cache hat.

Aus der Sicht, macht das anscheinend weniger Sinn, aber vielleicht bedeutet die L1-Verkleinerung und L2-Vergrößerung zu allen sonstigen Verbesserungen auch eine verbesserte Energie-Effizienz bzw. Performance-pro-Watt.

Ge0rgy

Grand Admiral Special

- Mitglied seit

- 14.07.2006

- Beiträge

- 4.322

- Renomée

- 82

- Mein Laptop

- Lenovo Thinkpad X60s

- Details zu meinem Desktop

- Prozessor

- Phenom II 955 BE

- Mainboard

- DFI LanParty DK 790FXB-M3H5

- Kühlung

- Noctua NH-U12P

- Speicher

- 4GB OCZ Platinum DDR1600 7-7-7 @ 1333 6-6-6

- Grafikprozessor

- Radeon 4850 1GB

- HDD

- Western Digital Caviar Black 1TB

- Netzteil

- Enermax Modu 525W

- Betriebssystem

- Linux, Vista x64

- Webbrowser

- Firefox 3.5

Von welchem L! reden wir hier überhaipt, I- oder D-Cache?

Die sind bei AMD ja getrennt.

Im Falle des I-Cache wäre zu überlegen in wieweit der trace-Cache bzw. RRC-Cache den Druck vom L1-I-Cache nimmt... oder ob in so einem Fall wohl ein kleinerer, schnellerer cache mehr bringt als ein großer der gemächlicher arbeitet...

Wie auch immer, ich bin sicher AMD hat da viel herumsimuliert um den besten Kompromiss zu generieren... ehrlich gesagt bin ich schon ziemlic hgespannt auf die ersten konkreten Messwerte von einem BD... den könnte man dann gut mit dem Llano vergleichen, oder einem Opteron etc... werden bestimmt interessante Analysen in welchen Fällen BD in welcher Weise von seiner Arhcitektur profitiert und ob es sogar Fälle gibt wo die "alte" K10-Konstruktion besser wäre...

Da können wir uns dann nach Herzenslust darüber auslassen welche Assoziativität und cache-größe in welchen Fällen wieviel hilft.. .auch im Quervergleich zu Sandy...

Ich seh schon...das wird lustig

Die sind bei AMD ja getrennt.

Im Falle des I-Cache wäre zu überlegen in wieweit der trace-Cache bzw. RRC-Cache den Druck vom L1-I-Cache nimmt... oder ob in so einem Fall wohl ein kleinerer, schnellerer cache mehr bringt als ein großer der gemächlicher arbeitet...

Wie auch immer, ich bin sicher AMD hat da viel herumsimuliert um den besten Kompromiss zu generieren... ehrlich gesagt bin ich schon ziemlic hgespannt auf die ersten konkreten Messwerte von einem BD... den könnte man dann gut mit dem Llano vergleichen, oder einem Opteron etc... werden bestimmt interessante Analysen in welchen Fällen BD in welcher Weise von seiner Arhcitektur profitiert und ob es sogar Fälle gibt wo die "alte" K10-Konstruktion besser wäre...

Da können wir uns dann nach Herzenslust darüber auslassen welche Assoziativität und cache-größe in welchen Fällen wieviel hilft.. .auch im Quervergleich zu Sandy...

Ich seh schon...das wird lustig

Opteron

Redaktion

☆☆☆☆☆☆

Jo, v.a. wird der L2 auch verbreitert werden müssen. Im Moment hat AMD ja eine 128bit Anbindung, aber bei BD muss das etwas mehr werden, wenn gleich 2 Threads versorgt werden wollen. 256bit ist Minimum, eventuell dual ported mit 2x1 MB Blöcken, ähnlich wie bei Nehalems L3 Cache. Beim Nehalem hat jeder Kern einen 2MB L3 Anteil, der etwas schneller ansprechbar ist, als der restliche L3.Aha, dann dürfte sich der Performance-Einbruch von 2x512 kb L2 statt 2x1024 MB L2 doch etwas stärker auswirken als ich gedacht hatte.

Ich kannte ja nur den (genauen) Wert von AMD, nicht von Intel.

Vorteil liegt auf der Hand, für die Applikationen die mit 1 MB auskommen hat man schnellere Zugriffszeiten, bei 2 MB dann nur etwas mehr.

Problem ist das gegenseitige Rauskegeln der Daten aus dem gemeinsamen Cache, aber für Desktopanwendungen wird man mit 4 Modulen und 4 Turbo Cores eh besser fahren, da hätte dann ein Kern den vollen L2. Wäre ideal, aber das ist jetzt schon stark spekuliert

HPC Apps dagegen brauchen eh keinen großen L2, dafür laufen die Nehalems viel zu gut, wahrscheinlich greifen da die Prefetcher zu 100%.

Bei (Web)serversachen, hab ich gerade keine Ahnung, aber schlecht sind die Nehalems da ja auch nicht. Schlechter als 4 SMT Kerne können 8 echte aber sicher nicht sein ^^

Fläche / Größe ist nicht das Problem, Zugriff und Zugriffszeit ist das Hindernis.Na ja, 8-Core-Bulldozer kommt mit 32nm, wo man wieder den L3-Cache verdoppeln könnte, ohne die Fläche im Vergleich zum Vergänger vergrößern zu müssen.

Im Moment wird der L3 Zugriff schön der Reihe nach vergeben, jeder darf mal ran. Wenn sich da jetzt doppelt soviel Kerne streiten würden wird das nicht besser ... v.a. auch wenn der Unterschied zw. Kern und Nichtkerntakt noch weiter steigt.

Das könnte beides zutreffen, erstens spekulieren wir ja schon länger auf einen (sehr) hoch getakteten BD, -> hoher Kerntakt, zweitens ja auch noch über T-RAM, das ist etwas langsamer als die normalen Zellen. Nicht viel, aber etwas

-> im Verhältnis langsamerer Kerntakt. Im Moment hat man ja beim 965er ja schon 1,4 GHz Unterschied, das könnten bei BD schnell 2 GHz werden.

-> im Verhältnis langsamerer Kerntakt. Im Moment hat man ja beim 965er ja schon 1,4 GHz Unterschied, das könnten bei BD schnell 2 GHz werden. Wobei man das eigentlich auch hochrechnen kann ... um DDR3-1600 DC ausnützen zu können, bräuchte man eigentlich 3,2 GHz Nichtkerntakt - wenn man mit einem 64bit Bus zw. Speicherkontroller und XBAR rechnet.

Zumindest anfangs rechne ich da aber natürlich nicht mit 5,2 GHz++ Kerntakt

Aber das Design wird ja ne Weile halten sollen.

Natürlich ist er schneller, aber die Hit Rate ist selbstverständlich nicht größerIch dachte, der kleinere aber schnellere bzw assozierierte L1-Cache wäre sogar schneller.

Naja, beim K7++ dachte sich AMD halt, viel hilft viel, aber jetzt, mit 2 Kernen pro Modul, muss man mit der Fläche besser haushaltenAus der Sicht, macht das anscheinend weniger Sinn, aber vielleicht bedeutet die L1-Verkleinerung und L2-Vergrößerung zu allen sonstigen Verbesserungen auch eine verbesserte Energie-Effizienz bzw. Performance-pro-Watt.

Ich glaub deswegen auch nicht an einen 4way Kern, um das versorgen zu können brächte man dann ein 8way Front-End, das würde sich unter Effizienzkriterien sicher nicht lohnen. Lieber klein und simpel und dafür höher takten

.

EDIT :

.

Jo gespannt ist hier wohl jederehrlich gesagt bin ich schon ziemlic hgespannt auf die ersten konkreten Messwerte von einem BD... den könnte man dann gut mit dem Llano vergleichen, oder einem Opteron etc... werden bestimmt interessante Analysen in welchen Fällen BD in welcher Weise von seiner Arhcitektur profitiert und ob es sogar Fälle gibt wo die "alte" K10-Konstruktion besser wäre...

Da können wir uns dann nach Herzenslust darüber auslassen welche Assoziativität und cache-größe in welchen Fällen wieviel hilft.. .auch im Quervergleich zu Sandy...

Ich seh schon...das wird lustig

Aktuell sind beim AMD - Intel Vergleich die Anno Benches mit seeehr großen Karten lustig, da gilt ausnahmsweise mal "Nehalame", ein K10 ist schneller. Als Grund kommt da eigentlich nur der Cache in frage. Preisfrage ist nur, ob L1 oder L2 ...

Für die, die es noch nicht kennen sollten:

http://www.computerbase.de/artikel/...test_prozessoren_2009/18/#abschnitt_anno_1404

ciao

Alex

Dresdenboy

Redaktion

☆☆☆☆☆☆

Der Transistorflächenansatz ist gut, da ich die Komponenten um die BD-Module eher grob geschätzt habe. Andererseits habe ich versucht, auch schon bei den Cores im Wesentlichen die ein die genutzte Fläche zu werten. Trotzdem gibt es ja immer wieder Leerräume, schlecht (eher mit Nachteilen) nutzbare Flächen usw. Deshalb habe ich nun auch kein Problem damit, bei 10-20% mehr Fläche mitzugehen. Die "uncore"-Komponenten kann ich nochmal genauer schätzen.@Dresdenboy: Die 210 mm² für ein 4-Modul Bulldozer, die du im Januar geschätzt hast, sind zu gering. Wenn wir eine für 32 nm realistische Transistordichte annehmen, so ca. 4,6 - 4,7 Millionen pro mm² (Gulftown liegt übrigens bei 4,71), dann kommen wir bei 210 mm² auf ca. 975 Millionen xtors. Die 16 MB L2+L3 Cache die du veranschlagst (halte ich für eine gute Schätzung) würden aber bereits 805 Millionen xtors in Beschlag nehmen, da würde höchstens Platz für ein Modul plus Peripherie sein.

Ich denke das ein 4-Modul Bulldozer sich in der selben Größenordung wie Deneb und Nehalem bewegen wird, also so um die 240-270 mm², anders lässt sich der ganze Kram den er haben wird nicht unterbringen. Damit läge man bei ca. 1200 Millionen xtors.

Llano liegt ja laut AMD bei ~ 1000 Millionen xtors.

Aber erstmal werde ich ab Mittwoch für eine Woche offline sein. Danach gibt es hier bestimmt viel Interessantes zu lesen.

Aber das ist auch cool:

http://citavia.blog.de/2010/03/03/p...ation-is-online-here-slide-8110111/#c12489963

Da haben schon welche angebissen

Stefan Payne

Grand Admiral Special

Nein, auch das PCie Interface, das beim Nehalem irgendwie buggy ist.Als Grund kommt da eigentlich nur der Cache in frage. Preisfrage ist nur, ob L1 oder L2 ...

Opteron

Redaktion

☆☆☆☆☆☆

Nö das nicht, da der Abstand auch bei 800x600er Auflösung vorhanden ist, bei der Auflösung gehe ich von geringem I/O Aufkommen aus.[3DC]Payne;4164754 schrieb:Nein, auch das PCie Interface, das beim Nehalem irgendwie buggy ist.

Eventuell war das ganze aber nur ne Treibergeschichte, bei den Cat 10.2 Ergebnissen von CB bei Anno 1404, die ich gerade erst gesehen habe, fallen deftige Zugewinne auf:

http://www.computerbase.de/artikel/...richt_ati_catalyst_102/6/#abschnitt_anno_1404

Leider keine Vergleichswerte mit einem AMD Prozessor, aber das könnte es gewesen sein.

ciao

Alex

Jo gespannt ist hier wohl jeder

Aktuell sind beim AMD - Intel Vergleich die Anno Benches mit seeehr großen Karten lustig, da gilt ausnahmsweise mal "Nehalame", ein K10 ist schneller. Als Grund kommt da eigentlich nur der Cache in frage. Preisfrage ist nur, ob L1 oder L2 ...

Für die, die es noch nicht kennen sollten:

http://www.computerbase.de/artikel/...test_prozessoren_2009/18/#abschnitt_anno_1404

ciao

Alex

Ich tippe auf den L2, da der Yorkfield proMhz-mäßig deutlich schneller ist, sogar vorm K10.

.

EDIT :

.

[3DC]Payne;4164754 schrieb:Nein, auch das PCie Interface, das beim Nehalem irgendwie buggy ist.

Nö, das würde den Rückstand des i7-960 Bloomfield nicht erklären.

Opteron

Redaktion

☆☆☆☆☆☆

Aja stimmt ja, den hatte ich ganz vergessen ^^Ich tippe auf den L2, da der Yorkfield proMhz-mäßig deutlich schneller ist, sogar vorm K10.

Zur allgemeinen Belustigung; 3DC arbeitet mit vollem Elan daran den guten Ruf zu verschlechtern:

http://www.3dcenter.org/news/2010-03-08Für die Prozessoren des Jahres 2011 wird aber auch bei AMD wohl ein neuer Sockel vonnöten, da AMD mit den neuen Architekturen Bulldozer und Llano doch einiges ändern wird.

Die aktuelle News hat fast den Anschein als versuche man zum Artikelende hin noch mit aller Gewalt AMD irgendetwas Schlechtes in die Schuhe schieben zu können.

@Dresdenboy:

Urlaub oder Arbeitsreise ?

In jedem Fall viel Spass.

ciao

Alex

Zuletzt bearbeitet:

rkinet

Grand Admiral Special

http://techreport.com/discussions.x/15343Prinzipel darf man nicht vergessen, dass bei einem Modul mit 2x512 kB zwar 25% weniger Core-Fläche bedeutet, aber damit würde z.B. ein 2 Modul-Bulldozer-Die ohne L3, ich schätze mal, eine nur 10-20% gesamte Die-Größe bedeuten.

Da war meine darstellung mit -25% ziemlich verzerrt.

Na ja, 8-Core-Bulldozer kommt mit 32nm, wo man wieder den L3-Cache verdoppeln könnte, ohne die Fläche im Vergleich zum Vergänger vergrößern zu müssen.

Ich dachte, der kleinere aber schnellere bzw assozierierte L1-Cache wäre sogar schneller.

Beim Übergang 32nm auf 22nm sinkt die SRAM-Zelle von 0,15 auf 0,1 um2.

Da wird es eher kritisch ob die CPU-Logik wg. Abwärme auch so proportional sinken kann.

Beim Bulldozer wäre also 1M L2 in 32nm und 22nm eine Größe die im Verhältnis zum Core eher wenig Zusatzfläche bedeutet.

Bzgl. L3 bleibt die Frage ab AMD den IBM-Weg zu eDRAM mitgeht: http://www-03.ibm.com/press/us/en/pressrelease/28428.wss

Für die bisher vorgesehenen 8 MB L3 beim 8-fach Bulldozer Core in 32nm ist SRAM sicherlich noch gut platzsparend machbar. In 22nm und eDRAM hingegen wären 16-24 MB-L3 leicht machbar was besser vs. Intel-Roadmap wäre.

Und im Consumer-Bereich wäre ein 32nm LIano-Nachfolger mit 4* Bulldozer (1-2 MB L2) aber ohne L3 (wg.Platzbedarf) auch nicht als Performance-Überflieger zu erwarten.

Ähnliche Themen

- Antworten

- 0

- Aufrufe

- 923

- Antworten

- 78

- Aufrufe

- 14K

- Antworten

- 2

- Aufrufe

- 3K

- Antworten

- 760

- Aufrufe

- 99K

- Antworten

- 8

- Aufrufe

- 2K