App installieren

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: This feature may not be available in some browsers.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

AMD liefert bereits M2 Samples - DDR-II ab Q1'06 im Handel

- Ersteller rkinet

- Erstellt am

rkinet

Grand Admiral Special

Das Geheimnis heißt 'Serienstreuung'.In diesem Forum sah ich AFAIK Strommessungen, wo der AM2 weniger verbraucht als der mit 939.

Aber in anderen Foren wird das Gegenteil gezeit. Gut, ich hab nur 2-3 Messungen gesehen, aber die reden schon so selbstverständlich, dass der AM2 bekanntlich mehr Strom frist als die 939-CPUs.

Na ja, zumindestens werde ich in Zukunft besonderst auf die Strommessungen von AM2 vs. 939 achten.

AMD erhält Cores mit niedrigen Strombedarf und solche mit etwas erhöhtem Strombedarf.

Da ist es reiner Zufall, wenn man passende Ergebnisse beim Vergleichstest erhält.

Man kann sich entsprechende Messungen von 'Fachmedien' gleich hinter die Haare schmieren oder die Messungen in den Gulli werfen.

AMD hingegen kennt die Steuungen und kann daher 67/ 68 Watt Linien für Dual-Core auflegen (s. http://www.computerbase.de/news/hardware/prozessoren/amd/2006/maerz/cebit06_verbrauch_cpus_amd/9

Opteron

Redaktion

☆☆☆☆☆☆

Lustig, langsam spricht es sich rum:

http://www.theinquirer.net/default.aspx?article=33094

Hat ja nur ein paar Wochen gedauert

und gleich gut für shocking news

Naja Inquirer Standart Sprache

ciao

Alex

http://www.theinquirer.net/default.aspx?article=33094

Hat ja nur ein paar Wochen gedauert

und gleich gut für shocking news

Naja Inquirer Standart Sprache

ciao

Alex

NOFX

Grand Admiral Special

- Mitglied seit

- 02.09.2002

- Beiträge

- 4.532

- Renomée

- 287

- Standort

- Brühl

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- Spinhenge

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 5 1600 @Stock

- Mainboard

- ASUS B350M-A

- Kühlung

- Boxed-Kühler

- Speicher

- 2x 8 G.Skill RipJaws 4 rot DDR4-2800 DIMM

- Grafikprozessor

- PowerColor Radeon RX 480 Red Dragon 8GB

- Display

- LG 34UM-68 (FreeSync)

- SSD

- PowerColor Radeon RX 480 Red Dragon 8GB

- HDD

- 1x 1,5TB Seagate S-ATA

- Optisches Laufwerk

- DVD-Brenner

- Soundkarte

- onBoard

- Gehäuse

- Thermaltake Versa H15

- Netzteil

- Cougar SX 460

- Betriebssystem

- Windows 10 Pro x64

- Webbrowser

- Google Chrome

Dass der Turion64 X2 mit seinen <2GHz nicht wirklich von DualChannel-Ram profitieren kann, ist ja wirklich was völlig Neues. Der normale Turion64 kam ja auch schon gut mit SingleChannel-Ram bei DDR1 klar, worum sollte also der X2 soviel mehr benötigen; und dass schon der AM2 nicht groß von der hohen theoretischen Bandbreite profitieren kann ist ja auch längst bekannt.

Aber naja, wie du schon schreibst, Inquirer halt.

Aber naja, wie du schon schreibst, Inquirer halt.

mtb][sledgehammer

Grand Admiral Special

- Mitglied seit

- 11.11.2001

- Beiträge

- 4.375

- Renomée

- 30

- Mein Laptop

- HP Compaq nx6125

- Details zu meinem Desktop

- Prozessor

- Athlon XP 2500+

- Mainboard

- Asrock K7S8XE

- Kühlung

- AC / selfmade Wakü

- Speicher

- 1 GB PC3200 Team Memory

- Grafikprozessor

- ATI Radeon 9500

- Display

- 20,1'' Samsung SyncMaster 205BW 1680x1050

- HDD

- Samsung SV0802N

- Optisches Laufwerk

- Toshiba DVD-ROM SD-M1612

- Soundkarte

- Creative SB Live! Player 1024

- Gehäuse

- Chenbro Net Server Tower

- Netzteil

- Coba 400 Watt (silent)

- Betriebssystem

- Windows XP, Ubuntu Linux

- Webbrowser

- Mozilla Firefox

- Verschiedenes

- knc TV Station , Terratec Cinergy 1200 DVB-C

Jaja, schon lustig  Aber dennoch könnte Dual Channel im Notebook Vorteile bringen, nämlich dann wenn die im Chipsatz integrierte Grafik auf den RAM zugreift. Wäre eigentlich ein interessanter Test, um zu überprüfen, ob der Controller tatsächlih nicht das Nadelöhr ist.

Aber dennoch könnte Dual Channel im Notebook Vorteile bringen, nämlich dann wenn die im Chipsatz integrierte Grafik auf den RAM zugreift. Wäre eigentlich ein interessanter Test, um zu überprüfen, ob der Controller tatsächlih nicht das Nadelöhr ist.

Aber dennoch könnte Dual Channel im Notebook Vorteile bringen, nämlich dann wenn die im Chipsatz integrierte Grafik auf den RAM zugreift. Wäre eigentlich ein interessanter Test, um zu überprüfen, ob der Controller tatsächlih nicht das Nadelöhr ist.

Aber dennoch könnte Dual Channel im Notebook Vorteile bringen, nämlich dann wenn die im Chipsatz integrierte Grafik auf den RAM zugreift. Wäre eigentlich ein interessanter Test, um zu überprüfen, ob der Controller tatsächlih nicht das Nadelöhr ist.Opteron

Redaktion

☆☆☆☆☆☆

Hmm ja, zumindest könnte man prüfen ob die Xbar "dick" genug ist. Denn durch die müssen die Daten ja vom MC zum HTr durchgeschleust werden.mtb][sledgehammer;2811327 schrieb:Jaja, schon lustigAber dennoch könnte Dual Channel im Notebook Vorteile bringen, nämlich dann wenn die im Chipsatz integrierte Grafik auf den RAM zugreift. Wäre eigentlich ein interessanter Test, um zu überprüfen, ob der Controller tatsächlih nicht das Nadelöhr ist.

Wär auf alle Fälle interessant

Nur: Wie messen ? Gibts ein Programm, dass die VideoRam Geschwindigkeit mißt ?

ciao

Alex

mtb][sledgehammer

Grand Admiral Special

- Mitglied seit

- 11.11.2001

- Beiträge

- 4.375

- Renomée

- 30

- Mein Laptop

- HP Compaq nx6125

- Details zu meinem Desktop

- Prozessor

- Athlon XP 2500+

- Mainboard

- Asrock K7S8XE

- Kühlung

- AC / selfmade Wakü

- Speicher

- 1 GB PC3200 Team Memory

- Grafikprozessor

- ATI Radeon 9500

- Display

- 20,1'' Samsung SyncMaster 205BW 1680x1050

- HDD

- Samsung SV0802N

- Optisches Laufwerk

- Toshiba DVD-ROM SD-M1612

- Soundkarte

- Creative SB Live! Player 1024

- Gehäuse

- Chenbro Net Server Tower

- Netzteil

- Coba 400 Watt (silent)

- Betriebssystem

- Windows XP, Ubuntu Linux

- Webbrowser

- Mozilla Firefox

- Verschiedenes

- knc TV Station , Terratec Cinergy 1200 DVB-C

Um direkt die Geschwindigkeit zu messen, leider nein. Aber einfach mal eben vergleichen, wie sich die Füllrate von Single Channel nach Dual Channel verändert (z.B. mit einem älteren 3D Mark, die haben da immer ziemlich sensibel auf RAM Takt Veränderungen=mehr Bandbreite reagiert)

Opteron

Redaktion

☆☆☆☆☆☆

Vielleicht können wir uns das sparen, anscheined war/ist nur ein bisschen "Reifezeit" vonnöten:mtb][sledgehammer;2812660 schrieb:Um direkt die Geschwindigkeit zu messen, leider nein. Aber einfach mal eben vergleichen, wie sich die Füllrate von Single Channel nach Dual Channel verändert (z.B. mit einem älteren 3D Mark, die haben da immer ziemlich sensibel auf RAM Takt Veränderungen=mehr Bandbreite reagiert)

Auf anandtech gibts nen AM2 Conroe Speicher Vergleich:

http://www.anandtech.com/memory/showdoc.aspx?i=2800

Spitzenwert ist da der FX-62 mit 9,3 GB/s (Sandra buffered Werte) das ist "etwas" mehr als in den ersten Tests ...

Wäre mal interessant, an was das liegt. Neue Bios Version, klar, aber was die macht ... ?

Ausserdem muss man mal sagen, dass es ein guter anandtech Artikel ist, war ich ja schon lange nicht mehr gewohnt von denen

ciao

Alex

Dragonfly

Lieutnant

- Mitglied seit

- 23.10.2005

- Beiträge

- 52

- Renomée

- 0

- Mein Laptop

- HP 625 // HP Mini 210

- Details zu meinem Desktop

- Prozessor

- AMD FX-8120 95W

- Mainboard

- ASUS Sabertooth 990FX

- Kühlung

- Arctic Cooling Freezer 13 Pro

- Speicher

- Corsair Vengeance 8 GB DDR3-1866

- Grafikprozessor

- PowerColor Radeon HD 7950 PCS+

- Display

- HP ZR24w

- SSD

- Samsung 840 Evo 250 GB

- HDD

- WD20EARX

- Optisches Laufwerk

- DVD-RW, BD-ROM

- Gehäuse

- Lian Li PC-70

- Netzteil

- Corsair HX520

- Betriebssystem

- Windows 8.1

- Webbrowser

- Firefox

Mal ein paar Fragen...

Wie sieht es eigentlich mit den eSige Core´s aus? Wird es das nur für High End Modelle geben oder werden auch beispielsweise Semprons eSige haben.

Wann wird es denn so richtig mit Revison G losgehen? Wird dann auch endlich das TT Modell des Turions auf den Markt kommen?

Wie sieht es eigentlich mit den eSige Core´s aus? Wird es das nur für High End Modelle geben oder werden auch beispielsweise Semprons eSige haben.

Wann wird es denn so richtig mit Revison G losgehen? Wird dann auch endlich das TT Modell des Turions auf den Markt kommen?

rkinet

Grand Admiral Special

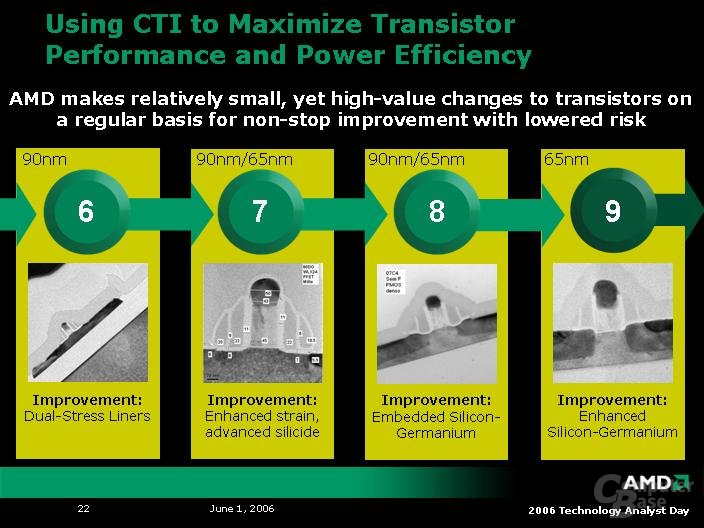

Es ist zu vermuten, daß AMD die eSiGe auch an eine bestimmte Revision 'hängt'. Schließlich sieht der ganze Transistor anders aus.Wie sieht es eigentlich mit den eSige Core´s aus?

Wird es das nur für High End Modelle geben oder werden auch beispielsweise Semprons eSige haben.

Wann wird es denn so richtig mit Revison G losgehen? Wird dann auch endlich das TT Modell des Turions auf den Markt kommen?

Allerdings könnte AMD auch noch in 90nm die eSiGe einführen und dann in der Fab30/36 und Chartered für einige Monate testen.

Der 65nm Sempron wird eSiGe bestimmt nicht benötigen, es kann aber für AMD billiger sein einheitlich zu fertigen. Da ist vieles noch unklar, aber die Zeitfenster für 90nm (läuft Mitte 2007 aus) und 65nm (ab Mitte 2008 durch 45nm ersetzt) lassen wenige Zwischenschritte erahnen.

Turion TT = 25 Watt ?

Bisher hat AMD früh neue Techniken im Mobilbereich asl erstes umgesetzt, da kann man nur hoffen, daß due 65nm Fertigung hier schnell die TT-Modelle ermöglichst.

Sonst wird AMD vom Merom am Markt noch Q4'2006 zerquetscht.

Hans Fuchs

Commander

- Mitglied seit

- 17.06.2005

- Beiträge

- 181

- Renomée

- 1

eSiGe werd doch mit 65nm eingeführt!?

rkinet

Grand Admiral Special

Das mit 'September' höre ich zum ersten mal - Quelle ?Nein, laut AMD soll SiGe in der 8ten-Transitor-Generation der 90er Struktur so um September eingeführt werden .

vgl. http://www.computerbase.de/news/wirtschaft/unternehmen/amd/2006/juni/amd_analyst_day_mitte_2008_45/

Jetzt müßte Step 7 = verbessertes strecken und Transistoren kommen,

sowohl für 90nm, als auch 65nm.

Anschließend nochmals Step 8 mit eSiGe für beide Techniken.

Könnte also Step 7 so Ende Q3 bis Anf. Q4 kommen, dannn Step 8 zusammen mit dem K8L so Q2-Q3'2007. Step 9 dann vielleicht Q4'2007.

Jetzt müßte Step 7 = verbessertes strecken und Transistoren kommen,

sowohl für 90nm, als auch 65nm.

Anschließend nochmals Step 8 mit eSiGe für beide Techniken.

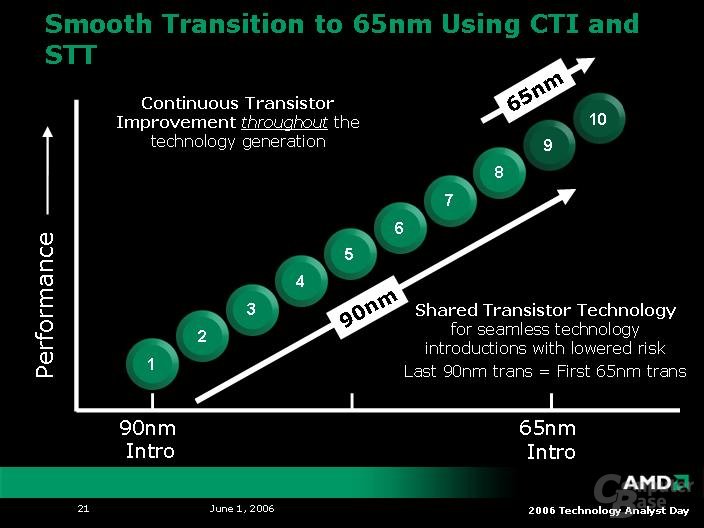

Also, ich hab es so verstanden, dass Step 7 schon in Juni eingeführt wurde und dabei werden auch die 65er-Belichtungsmaschinen vorerst in der 90er Struktur fertigen, was auch etwas hochwertige CPUs rausbringt als reine 90er-Belichtungsmaschinen.

Und wenn man generell eine Präsentation macht, in der über die Zukünftigen Generationen berichtet wird, ist es für mich logisch, auch das momentane bzw. Bestand (= 6te Generation) zu erwähnen bzw. aufzeigen.

Hier gehts um die 7 bzw. 8 Generation der 90er Struktur und nicht um die Transistor-Generation generell.

Da die 9te-Generation nicht mehr die 90er Struktur ist, wurde sie wahrscheinlich deshalb dunkelgrün gefertigt.

AMD hat ja angekündigt, dass sie SiGe vor der 65er-Struktur einführen wollen.

Und wenn AMD langsame Sprünge machen will und daher eines nach dem anderen Einführen will, dann müsste aus meiner Sicht in September SiGe kommen.

Aus dieser Grafik verstehe ich, dass die 65er-Struktur erst in der 9ten Transistor-Generation eingeführt wird.

Denn genau über dem "65er intro" ist die Zahl 9 positioniert und dieser Kreis inkl. nachfolgenden ist dazu noch in einem dunkleren Grün eingezeichnet.

Zuletzt bearbeitet:

Opteron

Redaktion

☆☆☆☆☆☆

Aus dieser Grafik verstehe ich, dass die 65er-Struktur erst in der 9ten Transistor-Generation eingeführt wird.

Denn genau über dem "65er intro" ist die Zahl 9 positioniert und dieser Kreis inkl. nachfolgenden ist dazu noch in einem dunkleren Grün eingezeichnet.[/QUOTE] Ich hoffe doch, das AMD schon weiter ist. So wie ich das verstehe sind das ja R&D roadmaps, keine retail. 65nm Chips gibts ja schließlich auch schon länger. Das erste Foto von einer CPU hat die Aufschrift "2000", falls das für 2000 MHz steht, könnte das auf einen primitiven (ohne strained, und natürlich erst recht ohne eSiGe) 65nm Prozess hinweisen.

Parallel dazu wird aber wohl ein eSiGe 90nm Prozess laufen. Vielleicht gibts dann bald neue FX Chips. Damals bei 130nm wurden ja auch die strained Si Technik ausprobiert, was dann in erste FX55 Chips mündete, obwohl auch schon 90nm produziert wurde.

Könnte ja wieder so ablaufen ...

ciao

Alex

Was ist das?

Ich schätze auch, dass SiGe zuerst in den FX-Chips ausprobiert wird, da schon roadmaps, na ja zumindestens eines, aufgetaucht sind in denen es schnelleres FX bei gleichen Wattverbrauch aufgelistet waren.Vielleicht gibts dann bald neue FX Chips.

mtb][sledgehammer

Grand Admiral Special

- Mitglied seit

- 11.11.2001

- Beiträge

- 4.375

- Renomée

- 30

- Mein Laptop

- HP Compaq nx6125

- Details zu meinem Desktop

- Prozessor

- Athlon XP 2500+

- Mainboard

- Asrock K7S8XE

- Kühlung

- AC / selfmade Wakü

- Speicher

- 1 GB PC3200 Team Memory

- Grafikprozessor

- ATI Radeon 9500

- Display

- 20,1'' Samsung SyncMaster 205BW 1680x1050

- HDD

- Samsung SV0802N

- Optisches Laufwerk

- Toshiba DVD-ROM SD-M1612

- Soundkarte

- Creative SB Live! Player 1024

- Gehäuse

- Chenbro Net Server Tower

- Netzteil

- Coba 400 Watt (silent)

- Betriebssystem

- Windows XP, Ubuntu Linux

- Webbrowser

- Mozilla Firefox

- Verschiedenes

- knc TV Station , Terratec Cinergy 1200 DVB-C

R&D = Research and Development oder zu Deutsch F&E (Forschung und Entwicklung)Was ist das?

rkinet

Grand Admiral Special

Primitiver 65nm Prozess ? Outsourcing ins Erzgebirge und Chemikalien bei Conrad eingekauft ?Ikönnte das auf einen primitiven (ohne strained, und natürlich erst recht ohne eSiGe) 65nm Prozess hinweisen.

Parallel dazu wird aber wohl ein eSiGe 90nm Prozess laufen. Vielleicht gibts dann bald neue FX Chips. Damals bei 130nm wurden ja auch die strained Si Technik ausprobiert, was dann in erste FX55 Chips mündete, obwohl auch schon 90nm produziert wurde.

Könnte ja wieder so ablaufen ...

eher: http://www.computerbase.de/news/wirtschaft/unternehmen/amd/2006/juni/amd_analyst_day_mitte_2008_45/

AMD startet zwei neue Schritte in der Fertigung parallel für 90/65nm.

Diese würden beim 90nm FX und den höher getakteten X2 sich sicherlich gut machen und AMD könnte Yieldrate und Taktrate mal in der Serienfertigung optimieren.

Die gerade neu eingeführten Opterone dürfte AMD unverändert bis zum 65nm K8L durchziehen müssen, da ist kein Platz für Experimente.

Opterone dürften dann auch bis Mitte 2007 eSiGe zusammen mit dem K8L-Design erhalten.

Der Rest ist Spekulation, nach meinem Geschmack zuviele Zwischenschritte, was zum Stepping-Wirrwar führen dürfte und die BIOS-Programmierer auf Trap halten wird.

Infos auf Bild 4So wie ich das verstehe sind das ja R&D roadmaps,...

Das bezweifel ich.

Denn wenn es R&D roadmaps wären, dann müsste die 45er und 32er-Struktur aufgelistet sein.

Opteron

Redaktion

☆☆☆☆☆☆

Ok, sorry, ich meinte R&D roadmaps für das gemeine Volk. 45 oder 32nm Infos hütet jeder Hersteller wie seinen Augapfel. Auf den ganzen 65/90nm Folien siehst Du nirgens ein Datum. Erste Prototypen 65nm Fotos gibts schon länger, AMD fängt nicht erst jetzt damit an. Was bald startet, ist die 65nm Produktion für den Endkundenmarkt.Infos auf Bild 4

Das bezweifel ich.

Denn wenn es R&D roadmaps wären, dann müsste die 45er und 32er-Struktur aufgelistet sein.

@rkinet:

Nochmal, ich mein keine Endkunden CPUs, sondern Prototypen. Ich interpretiere die parallelen "65/90nm" Auf den AMD Folien so, das neue "Sachen" wie eSiGe erst mal mit dem "guten, alten" 90nm Prozess ausprobiert werden. Parallel dazu versucht man sich an einem einfachen 65nm Prozess, ohne eSiGe, ohne strained Silicon ohne ...

Den BIOS Programmierern wäre sowas egal, es ändert sich ja nichts am Chip Aufbau, sondern nur am Material. Das hat nur Auswirkungen auf vcore und/oder Taktfrequenz.

ciao

Alex

rkinet

Grand Admiral Special

http://www.planet3dnow.de/vbulletin/showthread.php?p=2846449#post2846449@rkinet:

Nochmal, ich mein keine Endkunden CPUs, sondern Prototypen. Ich interpretiere die parallelen "65/90nm" Auf den AMD Folien so, das neue "Sachen" wie eSiGe erst mal mit dem "guten, alten" 90nm Prozess ausprobiert werden. Parallel dazu versucht man sich an einem einfachen 65nm Prozess, ohne eSiGe, ohne strained Silicon ohne ...

Den BIOS Programmierern wäre sowas egal, es ändert sich ja nichts am Chip Aufbau, sondern nur am Material. Das hat nur Auswirkungen auf vcore und/oder Taktfrequenz.

AMD hat den Quad-Core fertig und heute an die AMD-Fertigung übergeben (AMD-Pressemeldung).

Der kommt ja als K8L und dieses Design ist gemäß AMD-Roadmap eigentlich ein eSiGe Design in 65nm (wäre mit knapp 300 mm2 in 65nm eh zu groß für 90nm ... 500-600 mm2 DIE)

Opteron

Redaktion

☆☆☆☆☆☆

Öh, ja die news hab ich auch gelesen, hättest Du nicht hier nochmal posten brauchen. Nur was hat das mit dem aktuellen Thema 65/90nm Prozeß zu tun, oder war es nicht als Antwort gedacht ? Aus Wikipedia:http://www.planet3dnow.de/vbulletin/showthread.php?p=2846449#post2846449

AMD hat den Quad-Core fertig und heute an die AMD-Fertigung übergeben (AMD-Pressemeldung).

Der kommt ja als K8L und dieses Design ist gemäß AMD-Roadmap eigentlich ein eSiGe Design in 65nm (wäre mit knapp 300 mm2 in 65nm eh zu groß für 90nm ... 500-600 mm2 DIE)

Die Logikdesigner sind jetzt also fertig, das Design geht jetzt in die "Produktion"(natürlich nicht EndkundenproduktionIn electronics, tape-out is the name of the final stage of the design of an integrated circuit such as a microprocessor; the point at which the description of a circuit is sent for manufacture.

).

).ciao

Alex

Opteron

Redaktion

☆☆☆☆☆☆

Siehe P3D News:

http://www.planet3dnow.de/vbulletin/showthread.php?p=2855107

Damit können wir also hoffentlich endlich auch unsere Frage beantworten, ob 2xK8 Kerne mehr aus dem DDR2 Controller rausholen können. So schaut es bei mir aus:

Leider hab ich nur einen single core, deswegen wirds wohl nur "Thread 0" geben. Bei X2s schaut das aber hoffentlich anders aus. Wer also einen X2 hat und Versuchskaninchen spielen will ... immer vor

Edit:

Einführung & Screenshot mit "Thread 1" gibts hier:

gibts hier:

http://www.digit-life.com/articles2/cpu/rmma-general-3-add7.html

ciao

Alex

http://www.planet3dnow.de/vbulletin/showthread.php?p=2855107

Damit können wir also hoffentlich endlich auch unsere Frage beantworten, ob 2xK8 Kerne mehr aus dem DDR2 Controller rausholen können. So schaut es bei mir aus:

Leider hab ich nur einen single core, deswegen wirds wohl nur "Thread 0" geben. Bei X2s schaut das aber hoffentlich anders aus. Wer also einen X2 hat und Versuchskaninchen spielen will ... immer vor

Edit:

Einführung & Screenshot mit "Thread 1"

gibts hier:

gibts hier:http://www.digit-life.com/articles2/cpu/rmma-general-3-add7.html

ciao

Alex

Zuletzt bearbeitet:

rkinet

Grand Admiral Special

http://tecchannel.de/news/themen/technologie/446116/ (heute morgen auch an planet3dnow als Link gegeben)Öh, ja die news hab ich auch gelesen, hättest Du nicht hier nochmal posten brauchen. Nur was hat das mit dem aktuellen Thema 65/90nm Prozeß zu tun, oder war es nicht als Antwort gedacht ?

Aus Wikipedia: Die Logikdesigner sind jetzt also fertig, das Design geht jetzt in die "Produktion"(natürlich nicht Endkundenproduktion)

AMD fährt aber schon 'fleißig' Benchmarks mit dem Quad-Core incl. dem 4. Hyperlink.

Natürlich sind dies alles Beta-Steppings, aber wie man sieht funktioniert das Zusammenspiel der Cores intern und extern per Hypertransport schon sehr gut und dürfte auf Serien-Niveau liegen.

Die Rechenspiele von AMD beziehen sich offensichtlich auch nicht auf 65nm Quad vs. 90nm Dual-Core, sondern es werden Cores gleicher Technologie verglichen (? auch L3 beim Dual-Core ?).

Natürlich hatte AMD schon vor dem Tape-Out Anhaltspunkte für dessen Energiebedarf vs. Leistung, aber die Daten dürften realen, funktionsfähigen DIEs entstammen.

Für mich sieht es jetzt so aus, daß AMD Debugging inhouse und bei den OEMs betreiben muß und dann 'ready for production until mid 2007' ist.

Bem: 2004 hatte AMD auch im Sommer den Dual-Core so mit Leistungsdaten präsentiert und Q2'2005 war er dann auf dem Markt.

Ähnliche Themen

- Antworten

- 0

- Aufrufe

- 562

- Antworten

- 611

- Aufrufe

- 47K

- Antworten

- 0

- Aufrufe

- 834

- Antworten

- 0

- Aufrufe

- 2K

- Antworten

- 0

- Aufrufe

- 771