App installieren

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: This feature may not be available in some browsers.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

News Architektur-Infos zu Kaveri und Steamroller geleakt

- Ersteller Nero24

- Erstellt am

-

- Schlagworte

- gddr5 kaveri steamroller

★ Themenstarter ★

Bei <a href="http://www.brightsideofnews.com/news/2013/3/6/analysis-amd-kaveri-apu-and-steamroller-core-architectural-enhancements-unveiled.aspx" target="_blank">Bright Side of News</a> hat man kürzlich offenbar einige interne Dokumente in die Finger bekommen, aus denen man nun nach und nach Infos durchsickern lässt. Vorgestern erst die "<a href="http://www.planet3dnow.de/cgi-bin/newspub/viewnews.cgi?id=1362500242">Kaveri unterstützt GDDR5</a>" Story, und heute geht's weiter.

Angeblich aus einer Vorabversion des <i>BIOS and Kernel Developer's Guide for AMD Family 15h Models 30h-3Fh Processors</i> (derzeit noch nicht öffentlich einsehbar) stammen folgende Design-Details zum für Ende 2013 erwarteten "Bulldozer v3" alias "Steamroller" bzw. der APU mit Codenamen "Kaveri", die eben jene Steamroller-CPU-Kerne nutzen wird:<blockquote><i>- Store to load forwarding optimization

- Dispatch and retire up to 2 stores per cycle

- Improved memfile, from last 3 stores to last 8 stores, and allow tracking of dependent stack operations.

- Load queue (LDQ) size increased to 48, from 44.

- Store queue (STQ) size increased to 32, from 24.

- Increase dispatch bandwidth to 8 INT ops per cycle (4 to each core), from 4 INT ops per cycle (4 to just 1 core). 4 ops per cycle per core remains unchanged.

- Accelerate SYSCALL/SYSRET.

- Increased L2 BTB size from 5K to 10K and from 8 to 16 banks.

- Improved loop prediction.

- Increase PFB from 8 to 16 entries; the 8 additional entries can be used either for prefetch or as a loop buffer.

- Increase snoop tag throughput.

- Change from 4 to 3 FP pipe stages.</i></blockquote>Zudem soll der L1-Instruction-Cache auf 96 KB vergrößert werden. Was bereits <a href="http://www.planet3dnow.de/cgi-bin/newspub/viewnews.cgi?category=1&id=1346191456">seit Mitte 2012 bekannt</a> ist und von AMD bereits bestätigt wurde, sind die Änderungen am Front-End. So geht AMD mit Steamroller wieder einen Schritt zurück in Richtung <a href="http://www.planet3dnow.de/vbulletin/showthread.php?t=399114&garpg=24">"echtes" Multi-Core-Layout</a> und spendiert Steamroller wieder einen eigenen Dekoder pro INT-Einheit. Derzeit werden bei Bulldozer und Piledriver die "Kerne" von einem gemeinsam genutzten Dekoder pro Modul gefüttert.

<center><img src="http://www.planet3dnow.de/photoplog/file.php?n=21270&w=l" border="0" alt="Steamroller">

<img src="http://www.planet3dnow.de/photoplog/file.php?n=21271&w=l" border="0" alt="Steamroller">

<img src="http://www.planet3dnow.de/photoplog/file.php?n=21272&w=l" border="0" alt="Steamroller"></center>

Diese Änderungen sollen vor allem der Single-Thread-IPC zu Gute kommen, einer Disziplin, bei der die Bulldozer-Architektur derzeit schwächelt. Werden keine parallel arbeitenden Anwendungen und/oder Anwendungen verwendet, die nicht von den neuen Befehlssätzen profitieren, ist pro Takt gerechnet die alte K10-Architektur oft schneller als die Bulldozer-Derivate. Das soll sich mit Steamroller wieder ändern.

<center><img src="http://www.planet3dnow.de/vbulletin/attachment.php?attachmentid=27185&stc=1&d=1362664970" alt="Kaveri" border="0"><br>Quelle: <a href="http://www.brightsideofnews.com/news/2013/3/6/analysis-amd-kaveri-apu-and-steamroller-core-architectural-enhancements-unveiled.aspx" target="_blank">Bright Side of News</a></center>

Nach wie vor offen bleiben muss, ob die neuen Streamroller-Kerne lediglich in den Kaveri-APUs Verwendung finden - hier übrigens laut Leak mit bis zu 3 Compute-Units, also bis zu 6 "Kernen", wohingegen aktuelle APUs mit 2 CUs (4 "Kernen") auskommen müssen - oder ob der sogenannte Enthusiast-User nochmal mit einer Auffrischung der AM3+ Palette rechnen darf. Hierzu schweigen sich offizielle AMD Roadmaps nach wie vor aus.

<b>Links zum Thema:</b><ul><li><a href="http://www.brightsideofnews.com/news/2013/3/6/analysis-amd-kaveri-apu-and-steamroller-core-architectural-enhancements-unveiled.aspx" target="_blank">Analysis: AMD Kaveri APU and Steamroller Core Architectural Enhancements Unveiled</A></li><li><a href="http://www.planet3dnow.de/cgi-bin/newspub/viewnews.cgi?id=1362500242">Gerücht: AMD Kaveri mit Support für GDDR5?</A></li><li><a href="http://lists.freebsd.org/pipermail/freebsd-amd64/2012-July/014703.html" target="_blank">XSAVEOPT</A></li><li><a href="http://www.planet3dnow.de/cgi-bin/newspub/viewnews.cgi?category=1&id=1346191456">AMD präsentiert Steamroller-Details, 3rd Gen Bulldozer-Architektur auf Hotchips: +30% IPC?</A></li></ul>

Angeblich aus einer Vorabversion des <i>BIOS and Kernel Developer's Guide for AMD Family 15h Models 30h-3Fh Processors</i> (derzeit noch nicht öffentlich einsehbar) stammen folgende Design-Details zum für Ende 2013 erwarteten "Bulldozer v3" alias "Steamroller" bzw. der APU mit Codenamen "Kaveri", die eben jene Steamroller-CPU-Kerne nutzen wird:<blockquote><i>- Store to load forwarding optimization

- Dispatch and retire up to 2 stores per cycle

- Improved memfile, from last 3 stores to last 8 stores, and allow tracking of dependent stack operations.

- Load queue (LDQ) size increased to 48, from 44.

- Store queue (STQ) size increased to 32, from 24.

- Increase dispatch bandwidth to 8 INT ops per cycle (4 to each core), from 4 INT ops per cycle (4 to just 1 core). 4 ops per cycle per core remains unchanged.

- Accelerate SYSCALL/SYSRET.

- Increased L2 BTB size from 5K to 10K and from 8 to 16 banks.

- Improved loop prediction.

- Increase PFB from 8 to 16 entries; the 8 additional entries can be used either for prefetch or as a loop buffer.

- Increase snoop tag throughput.

- Change from 4 to 3 FP pipe stages.</i></blockquote>Zudem soll der L1-Instruction-Cache auf 96 KB vergrößert werden. Was bereits <a href="http://www.planet3dnow.de/cgi-bin/newspub/viewnews.cgi?category=1&id=1346191456">seit Mitte 2012 bekannt</a> ist und von AMD bereits bestätigt wurde, sind die Änderungen am Front-End. So geht AMD mit Steamroller wieder einen Schritt zurück in Richtung <a href="http://www.planet3dnow.de/vbulletin/showthread.php?t=399114&garpg=24">"echtes" Multi-Core-Layout</a> und spendiert Steamroller wieder einen eigenen Dekoder pro INT-Einheit. Derzeit werden bei Bulldozer und Piledriver die "Kerne" von einem gemeinsam genutzten Dekoder pro Modul gefüttert.

<center><img src="http://www.planet3dnow.de/photoplog/file.php?n=21270&w=l" border="0" alt="Steamroller">

<img src="http://www.planet3dnow.de/photoplog/file.php?n=21271&w=l" border="0" alt="Steamroller">

<img src="http://www.planet3dnow.de/photoplog/file.php?n=21272&w=l" border="0" alt="Steamroller"></center>

Diese Änderungen sollen vor allem der Single-Thread-IPC zu Gute kommen, einer Disziplin, bei der die Bulldozer-Architektur derzeit schwächelt. Werden keine parallel arbeitenden Anwendungen und/oder Anwendungen verwendet, die nicht von den neuen Befehlssätzen profitieren, ist pro Takt gerechnet die alte K10-Architektur oft schneller als die Bulldozer-Derivate. Das soll sich mit Steamroller wieder ändern.

<center><img src="http://www.planet3dnow.de/vbulletin/attachment.php?attachmentid=27185&stc=1&d=1362664970" alt="Kaveri" border="0"><br>Quelle: <a href="http://www.brightsideofnews.com/news/2013/3/6/analysis-amd-kaveri-apu-and-steamroller-core-architectural-enhancements-unveiled.aspx" target="_blank">Bright Side of News</a></center>

Nach wie vor offen bleiben muss, ob die neuen Streamroller-Kerne lediglich in den Kaveri-APUs Verwendung finden - hier übrigens laut Leak mit bis zu 3 Compute-Units, also bis zu 6 "Kernen", wohingegen aktuelle APUs mit 2 CUs (4 "Kernen") auskommen müssen - oder ob der sogenannte Enthusiast-User nochmal mit einer Auffrischung der AM3+ Palette rechnen darf. Hierzu schweigen sich offizielle AMD Roadmaps nach wie vor aus.

<b>Links zum Thema:</b><ul><li><a href="http://www.brightsideofnews.com/news/2013/3/6/analysis-amd-kaveri-apu-and-steamroller-core-architectural-enhancements-unveiled.aspx" target="_blank">Analysis: AMD Kaveri APU and Steamroller Core Architectural Enhancements Unveiled</A></li><li><a href="http://www.planet3dnow.de/cgi-bin/newspub/viewnews.cgi?id=1362500242">Gerücht: AMD Kaveri mit Support für GDDR5?</A></li><li><a href="http://lists.freebsd.org/pipermail/freebsd-amd64/2012-July/014703.html" target="_blank">XSAVEOPT</A></li><li><a href="http://www.planet3dnow.de/cgi-bin/newspub/viewnews.cgi?category=1&id=1346191456">AMD präsentiert Steamroller-Details, 3rd Gen Bulldozer-Architektur auf Hotchips: +30% IPC?</A></li></ul>

C4rp3di3m

Admiral Special

- Mitglied seit

- 14.12.2007

- Beiträge

- 1.855

- Renomée

- 193

- Standort

- Berlin

- Mein Desktopsystem

- Gigabyte FTW Storm Peak Army

- Details zu meinem Desktop

- Prozessor

- AMD THREADRiPPER 7960X

- Mainboard

- GIGABYTE TRX50 AERO D / X690

- Kühlung

- Alphacool Eisblock XPX Pro Aurora Full Brass Black Digital

- Speicher

- Kingston Fury Renegade PRO 6000 CL32-1T Quadchannel DDR5

- Grafikprozessor

- GIGABYTE AORUS Radeon RX 6900XTXH Xtreme Waterforce XT Copper Edition

- Display

- LG UltraGear 27GN800-B, HDR10, 144Hz, 1440p

- SSD

- Crucial MX100-256GB SSD, Kingston KC3000 NVME, Gigabyte Aorus M2 Gen4 NVME

- HDD

- n/a

- Optisches Laufwerk

- n/a

- Soundkarte

- Dual Chip Onboard Realtek ALC4080 & ALC897

- Gehäuse

- Be Quiet Dark Base Pro 901 Big Tower

- Netzteil

- CORSiAR HX1000i ATX v3.0 Full-Modular 80+Plus Platinium

- Tastatur

- Lioncast [Mechanisch]

- Maus

- G502 HERO

- Betriebssystem

- Windows 11 PRO x64

- Webbrowser

- FireFox

- Verschiedenes

- 3 Radiatoren ST30 120HPE+2x360HPE Fullcopper Loop, Pump: VPP755 V.3 Stufe2@95L/h, 1x140mm Sys-FAN, 7x120 Radiator FAN

- Schau Dir das System auf sysprofile.de an

- Internetanbindung

-

▼500MBit

▲100Mbit

Was ich bis Heute nicht verstehe ist, wieso die bei AMD nicht germerkt haben dass wenn sich die Kerne was Teilen müssen die Leistung mies ist. Die müssen doch selber gemerkt haben dass ihre Samples gegen den Ph2 und X6 Lausig dastehen? Traurig zu dem dass es so Lange gedauert hat von diesem Unsinn wieder abzukommen. Denke mal die neuen CPU´s werden richtig ein raus hauen. So lange der Stromverbrauch sich nicht auch Positiv entwickelt werden Sie Intel nicht einholen können.

mfg

mfg

Locuza

Commodore Special

- Mitglied seit

- 03.03.2011

- Beiträge

- 351

- Renomée

- 3

Also überrascht haben mich die 3 Module und die zwei fetten Dekoder.

Steamroller wird wohl ordentlich Piledriver und vor allem Bulldozer in vielen Disziplinen verprügeln.

Aber Geld und Zeit können limitieren, dann muss man sich entscheiden schiebt man es weiter auf oder wagt man den Schritt.

Das die ist ja mit ~ 300mm² kein kleiner Spatz.

Mit 28nm kann man sich an einigen Stellen wenigstens etwas mehr leisten.

Und Intel werden sie schon aus Prinzip nicht einholen können.

Wie will man mit 28nm planar 22/14nm Trigate in Sachen Perf/Watt einholen wollen?

Steamroller wird wohl ordentlich Piledriver und vor allem Bulldozer in vielen Disziplinen verprügeln.

Wer weiß wie hektisch es dort zuging und ob nicht jeder Bescheid wusste, dass das Design noch so viele Lücken und Engpässe hat.Was ich bis Heute nicht verstehe ist, wieso die bei AMD nicht germerkt haben dass wenn sich die Kerne was Teilen müssen die Leistung mies ist. Die müssen doch selber gemerkt haben dass ihre Samples gegen den Ph2 und X6 Lausig dastehen? Traurig zu dem dass es so Lange gedauert hat von diesem Unsinn wieder abzukommen. Denke mal die neuen CPU´s werden richtig ein raus hauen. So lange der Stromverbrauch sich nicht auch Positiv entwickelt werden Sie Intel nicht einholen können.

mfg

Aber Geld und Zeit können limitieren, dann muss man sich entscheiden schiebt man es weiter auf oder wagt man den Schritt.

Das die ist ja mit ~ 300mm² kein kleiner Spatz.

Mit 28nm kann man sich an einigen Stellen wenigstens etwas mehr leisten.

Und Intel werden sie schon aus Prinzip nicht einholen können.

Wie will man mit 28nm planar 22/14nm Trigate in Sachen Perf/Watt einholen wollen?

gruffi

Grand Admiral Special

- Mitglied seit

- 08.03.2008

- Beiträge

- 5.393

- Renomée

- 65

- Standort

- vorhanden

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 5 1600

- Mainboard

- MSI B350M PRO-VDH

- Kühlung

- Wraith Spire

- Speicher

- 2x 8 GB DDR4-2400 CL16

- Grafikprozessor

- XFX Radeon R7 260X

- Display

- LG W2361

- SSD

- Crucial CT250BX100SSD1

- HDD

- Toshiba DT01ACA200

- Optisches Laufwerk

- LG Blu-Ray-Brenner BH16NS40

- Soundkarte

- Realtek HD Audio

- Gehäuse

- Sharkoon MA-I1000

- Netzteil

- be quiet! Pure Power 9 350W

- Betriebssystem

- Windows 10 Professional 64-bit

- Webbrowser

- Mozilla Firefox

- Verschiedenes

- https://valid.x86.fr/mb4f0j

Wo bitteschön ist die mies? Etwa 80% Durchsatz ist doch genau das, was Vorgabe war. Jetzt kann man weiter optimieren, um den 100% zweier vollwertiger Kerne nahe zu kommen. Mies ist eher das, was bei Hyperthreading rauskommt, mit ~60% Durchsatz. Bulldozers Problem war weniger das Teilen, sondern mehr das exklusive Nutzen von Einheiten, also singlethreaded IPC. Dort hat man aber ebenfalls deutliche Verbesserungen vorgenommen.Was ich bis Heute nicht verstehe ist, wieso die bei AMD nicht germerkt haben dass wenn sich die Kerne was Teilen müssen die Leistung mies ist.

Orochi versägt einen X6 mal locker mit zweifacher Performance, wenn vernünftig optimiert wurde. Lausig ist was anderes.Die müssen doch selber gemerkt haben dass ihre Samples gegen den Ph2 und X6 Lausig dastehen?

Welcher Unsinn und von was abkommen? Steamroller ist weiterhin Bulldozer. Nur halt die nächste Evolutionsstufe. Am Grundprinzip hat sich nichts verändert.Traurig zu dem dass es so Lange gedauert hat von diesem Unsinn wieder abzukommen.

Die Leistungsaufnahme ist nicht so schlecht, wie sie oft hingestellt wurde. Auch mal Vergleiche abseits von FX-8150/8530 und den wenig relevanten Volllastmessungen anschauen.So lange der Stromverbrauch sich nicht auch Positiv entwickelt werden Sie Intel nicht einholen können.

Starcraftfreak

Vice Admiral Special

- Mitglied seit

- 02.04.2004

- Beiträge

- 851

- Renomée

- 7

Achso? Die Realität sieht leider anders aus. Kannst du mal Beispiele verlinken wo man entsprechend Performance gewinnt?Orochi versägt einen X6 mal locker mit zweifacher Performance, wenn vernünftig optimiert wurde. Lausig ist was anderes.

Doch, die Leitungsaufnahme ist schlecht. Klar verbrauchen die Chips unter "normalen" Anwendungen weniger als mit Prime, etc. weil die CPU nicht voll ausgelastet wird. Das gleiche gilt für die Konkurrenz allerdings auch.Die Leistungsaufnahme ist nicht so schlecht, wie sie oft hingestellt wurde. Auch mal Vergleiche abseits von FX-8150/8530 und den wenig relevanten Volllastmessungen anschauen.

gruffi

Grand Admiral Special

- Mitglied seit

- 08.03.2008

- Beiträge

- 5.393

- Renomée

- 65

- Standort

- vorhanden

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 5 1600

- Mainboard

- MSI B350M PRO-VDH

- Kühlung

- Wraith Spire

- Speicher

- 2x 8 GB DDR4-2400 CL16

- Grafikprozessor

- XFX Radeon R7 260X

- Display

- LG W2361

- SSD

- Crucial CT250BX100SSD1

- HDD

- Toshiba DT01ACA200

- Optisches Laufwerk

- LG Blu-Ray-Brenner BH16NS40

- Soundkarte

- Realtek HD Audio

- Gehäuse

- Sharkoon MA-I1000

- Netzteil

- be quiet! Pure Power 9 350W

- Betriebssystem

- Windows 10 Professional 64-bit

- Webbrowser

- Mozilla Firefox

- Verschiedenes

- https://valid.x86.fr/mb4f0j

Wurde doch nun schon oft genug gemacht. Schau dir Vergleiche an wie NAS Parallel Benchmarks oder C-Ray.Achso? Die Realität sieht leider anders aus. Kannst du mal Beispiele verlinken wo man entsprechend Performance gewinnt?

Nein, ist sie per se nicht.Doch, die Leitungsaufnahme ist schlecht.

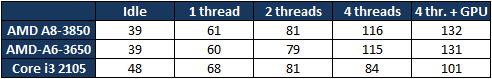

Aber nicht in gleichem Masze, da Intel zB kein Clock Grid wie Bulldozer hat und Hyperthreading auch nicht so viel Einsparungspotenzial bietet. Schau dir bei letzterem zB mal die Vergleichszahlen zwischen Llano und i3 an:Klar verbrauchen die Chips unter "normalen" Anwendungen weniger als mit Prime, etc. weil die CPU nicht voll ausgelastet wird. Das gleiche gilt für die Konkurrenz allerdings auch.

Bei voller Last liegt Llano klar über dem i3. Bei Last auf lediglich 2 Kernen sieht es hingegen schon ausgeglichen aus. Mit lediglich einem Kern ist Llano sogar sparsamer. Was in dem Fall aber sicherlich auch teils dem sparsameren Board geschuldet ist. Und das wird mit Teillast auf einem Kern noch komplizierter und schwieriger zu beurteilen. Sry, aber zu sagen, die Leistungsaufnahme sei per se zu schlecht, kann man nicht gelten lassen.

OBrian

Moderation MBDB, ,

- Mitglied seit

- 16.10.2000

- Beiträge

- 17.031

- Renomée

- 267

- Standort

- NRW

- Details zu meinem Desktop

- Prozessor

- Phenom II X4 940 BE, C2-Stepping (undervolted)

- Mainboard

- Gigabyte GA-MA69G-S3H (BIOS F7)

- Kühlung

- Noctua NH-U12F

- Speicher

- 4 GB DDR2-800 ADATA/OCZ

- Grafikprozessor

- Radeon HD 5850

- Display

- NEC MultiSync 24WMGX³

- SSD

- Samsung 840 Evo 256 GB

- HDD

- WD Caviar Green 2 TB (WD20EARX)

- Optisches Laufwerk

- Samsung SH-S183L

- Soundkarte

- Creative X-Fi EM mit YouP-PAX-Treibern, Headset: Sennheiser PC350

- Gehäuse

- Coolermaster Stacker, 120mm-Lüfter ersetzt durch Scythe S-Flex, zusätzliche Staubfilter

- Netzteil

- BeQuiet 500W PCGH-Edition

- Betriebssystem

- Windows 7 x64

- Webbrowser

- Firefox

- Verschiedenes

- Tastatur: Zowie Celeritas Caseking-Mod (weiße Tasten)

interessant, daß da "2-3 compute units" steht, aber vier Kästchen hintereinander geschachtelt sind. Sicher absichtliche Verwirrung. Machbar wäre beides, die leere Ecke bei einem 3-Moduler-Die könnte man ja mit der GPU und/oder Southbridge auffüllen.

Starcraftfreak

Vice Admiral Special

- Mitglied seit

- 02.04.2004

- Beiträge

- 851

- Renomée

- 7

@gruffi:

Dass die Leistung in Programmen/Benchmarks, die von allen Int-Kernen Gebrauch machen können und nicht durchs Modul-Design ausgebremst werden sich sehen lassen kann ist mir bekannt. Wie man so auf zweifache Performance eines X6 kommt, ist mir nach wie vor schleierhaft.

Das Beispiel der Leistungsaufnahme ist sehr plakativ. Der i3 2105 ist eine Dual-Core CPU mit HT, der Llano ein Quad-Core. Mit 2 Threads ist der i3 schon fast voll ausgelastet, das sieht man auch an dem geringen Sprung auf 4 Threads. Aber ich denke hier spielt eher das Board eine Rolle (wobei eventuell ja der Intel Chipsatz mehr Strom braucht, das weiß ich nicht).

Es ging mir außerdem um die Leistungsaufnahme der Bulldozer-Derivative. Ich wollte AMDs Leistungsaufnahme nicht generell schlechtreden. Aber bei den hohen Taktfrequenzen die man im Desktop-Bereich braucht sieht Zambezi/Vishera gegen Ivy Bridge derzeit in diesem Bereich kein Licht, weshalb AMD auch so stark über den Preis gehen muss. Wenn die Chips so toll wären würde ein 8350 nicht 200 sondern 600 Euro kosten

Dass die Leistung in Programmen/Benchmarks, die von allen Int-Kernen Gebrauch machen können und nicht durchs Modul-Design ausgebremst werden sich sehen lassen kann ist mir bekannt. Wie man so auf zweifache Performance eines X6 kommt, ist mir nach wie vor schleierhaft.

Das Beispiel der Leistungsaufnahme ist sehr plakativ. Der i3 2105 ist eine Dual-Core CPU mit HT, der Llano ein Quad-Core. Mit 2 Threads ist der i3 schon fast voll ausgelastet, das sieht man auch an dem geringen Sprung auf 4 Threads. Aber ich denke hier spielt eher das Board eine Rolle (wobei eventuell ja der Intel Chipsatz mehr Strom braucht, das weiß ich nicht).

Es ging mir außerdem um die Leistungsaufnahme der Bulldozer-Derivative. Ich wollte AMDs Leistungsaufnahme nicht generell schlechtreden. Aber bei den hohen Taktfrequenzen die man im Desktop-Bereich braucht sieht Zambezi/Vishera gegen Ivy Bridge derzeit in diesem Bereich kein Licht, weshalb AMD auch so stark über den Preis gehen muss. Wenn die Chips so toll wären würde ein 8350 nicht 200 sondern 600 Euro kosten

gruffi

Grand Admiral Special

- Mitglied seit

- 08.03.2008

- Beiträge

- 5.393

- Renomée

- 65

- Standort

- vorhanden

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 5 1600

- Mainboard

- MSI B350M PRO-VDH

- Kühlung

- Wraith Spire

- Speicher

- 2x 8 GB DDR4-2400 CL16

- Grafikprozessor

- XFX Radeon R7 260X

- Display

- LG W2361

- SSD

- Crucial CT250BX100SSD1

- HDD

- Toshiba DT01ACA200

- Optisches Laufwerk

- LG Blu-Ray-Brenner BH16NS40

- Soundkarte

- Realtek HD Audio

- Gehäuse

- Sharkoon MA-I1000

- Netzteil

- be quiet! Pure Power 9 350W

- Betriebssystem

- Windows 10 Professional 64-bit

- Webbrowser

- Mozilla Firefox

- Verschiedenes

- https://valid.x86.fr/mb4f0j

Dann schau dir die Anwendungen an. Wenn der FX8 doppelt so schnell arbeitet, dann ist das eben zweifache Performance. As simple as that!Dass die Leistung in Programmen/Benchmarks, die von allen Int-Kernen Gebrauch machen können und nicht durchs Modul-Design ausgebremst werden sich sehen lassen kann ist mir bekannt. Wie man so auf zweifache Performance eines X6 kommt, ist mir nach wie vor schleierhaft.

Deshalb habe ich es ja gebracht. Ein Prozessor verbringt nun mal die wenigste Zeit mit Vollast. Insofern sind solche Vergleiche eher nebensächlich für den Alltag. Es gibt auch nicht nur FX-8150/8350, wo Takt und TDP gut ausgereizt werden. Schau dir auch mal andere Modelle an. Und ob der i3 ein Dual-Core mit HT ist oder nicht, interessiert am Ende nicht. Er stellt 4 Threads zur Verfügung, genauso wie Llano.Das Beispiel der Leistungsaufnahme ist sehr plakativ.

Na dann sind wir uns ja einig. Denn genau das ist sie auch nicht.Es ging mir außerdem um die Leistungsaufnahme der Bulldozer-Derivative. Ich wollte AMDs Leistungsaufnahme nicht generell schlechtreden.

Der Vergleich hinkt schon deshalb, weil du hier 32 und 22nm vergleichst und weniger Bulldozer.Aber bei den hohen Taktfrequenzen die man im Desktop-Bereich braucht sieht Zambezi/Vishera gegen Ivy Bridge derzeit in diesem Bereich kein Licht

ich für meinen Teil.. bin vom FX83 positiv überrascht und kann mir gut vorstellen das die FX81 wie damals die Phenom I sind.

Was Steamroller angeht, bin ich gespannt ob AMD bei der Sockelpolitik bleibt und 2-3 Generationen auf einen Sockel laufen lassen oder nicht. (Am3+)

Meine Spekulation ist ja folgende, wenn AMD sagt sie wollen erst ende 2013 eine neue Grafikkarten Generation f. den Desktop Markt bringen.

Wird es dann ende 2013 auch ein neuen Desktop CPU Sockel (AM4) inkl. neuer Chipsätze geben? (Support f. DDR4/PCIe3.0 etc)

Auf jedenfall ist die Entwicklung die wir beobachten auf den richtigen Weg,mMn.

Weiter so AMD.

Grüße

Was Steamroller angeht, bin ich gespannt ob AMD bei der Sockelpolitik bleibt und 2-3 Generationen auf einen Sockel laufen lassen oder nicht. (Am3+)

Meine Spekulation ist ja folgende, wenn AMD sagt sie wollen erst ende 2013 eine neue Grafikkarten Generation f. den Desktop Markt bringen.

Wird es dann ende 2013 auch ein neuen Desktop CPU Sockel (AM4) inkl. neuer Chipsätze geben? (Support f. DDR4/PCIe3.0 etc)

Auf jedenfall ist die Entwicklung die wir beobachten auf den richtigen Weg,mMn.

Weiter so AMD.

Grüße

Onkel_Dithmeyer

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 22.04.2008

- Beiträge

- 12.951

- Renomée

- 4.068

- Standort

- Zlavti

- Aktuelle Projekte

- Universe@home

- Lieblingsprojekt

- Universe@home

- Meine Systeme

- cd0726792825f6f563c8fc4afd8a10b9

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- Ryzen 9 3900X @4000 MHz//1,15V

- Mainboard

- MSI X370 XPOWER GAMING TITANIUM

- Kühlung

- Custom Wasserkühlung vom So. G34

- Speicher

- 4x8 GB @ 3000 MHz

- Grafikprozessor

- Radeon R9 Nano

- Display

- HP ZR30W & HP LP3065

- SSD

- 2 TB ADATA

- Optisches Laufwerk

- LG

- Soundkarte

- Im Headset

- Gehäuse

- Xigmatek

- Netzteil

- BeQuiet Dark Pro 9

- Tastatur

- GSkill KM570

- Maus

- GSkill MX780

- Betriebssystem

- Ubuntu 20.04

- Webbrowser

- Firefox Version 94715469

- Internetanbindung

- ▼100 Mbit ▲5 Mbit

Ich denke dass AM3+ der letzte HT-fähige Sockel war. Eher wird man die beiden Dekstopsockel zusammenlegen, vermutlich als FM3 o.ä.

Ich denke dass AM3+ der letzte HT-fähige Sockel war. Eher wird man die beiden Dekstopsockel zusammenlegen, vermutlich als FM3 o.ä.

![Augen rollen (sarkastisch) :] :]](https://www.planet3dnow.de/vbulletin/images/smilies/rolleyes.gif)

na, in dem Falle hoffe u. bete ich das Du unrecht haben wirst.

na, in dem Falle hoffe u. bete ich das Du unrecht haben wirst.

Und wenn doch dann hoffe ich das sie es so beibehalten das die APU´s (FM2) auch ebenfalls Ohne Gpu Kern zu erhalten werden sind u. diese dann weiterhin auf Am3+ Sockel lauffähig sein werden.

Wobei das mit den Pins so ne sache sein wird.. bei den vielen, dickeren Am3+ Pins..

Gruß Andy

Zuletzt bearbeitet:

y33H@

Admiral Special

- Mitglied seit

- 16.05.2011

- Beiträge

- 1.768

- Renomée

- 10

Ausgehend von identischem Verbrauch im Leerlauf sind alle FX und A-Serie bei Teil- wie Vollast energiehungriger als ein SNB-Chip und je nach Workload zudem langsamer (zB Spiele).Nein, ist sie per se nicht.

Ähnliche Themen

- Antworten

- 0

- Aufrufe

- 844

- Antworten

- 0

- Aufrufe

- 987

- Antworten

- 0

- Aufrufe

- 675

- Antworten

- 0

- Aufrufe

- 457

- Antworten

- 0

- Aufrufe

- 426