App installieren

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: This feature may not be available in some browsers.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Bulldozer - AMD Fam 15h - allgemeiner Infothread

- Ersteller Opteron

- Erstellt am

Bobo_Oberon

Grand Admiral Special

- Mitglied seit

- 18.01.2007

- Beiträge

- 5.045

- Renomée

- 190

So weit war man damals dann bei AMD doch nicht.... hatte der K5 nich nen 3 Operanden FPU? ...

Die K5 FPU war auch nicht überragend. Die Integerrechenleistung war hingegen damals Spitzenklasse (bezogen auf den Takt).

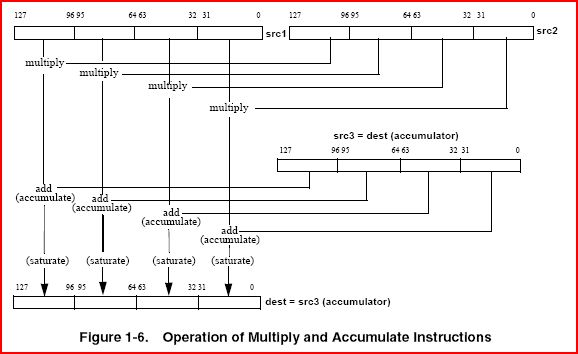

Kurz ausgedrückt ermöglicht diese neue TFP-Einheit etwas, was bis dahin auf x86-CPUs noch nicht möglich war.

Quelle

Derzeit können nur zwei Operatoren miteinander multipliziert werden. Die Addition erfordert wieder eine Rückspeicherung und Sicherung der Ergebnisse (was Zeit kostet).

Mit SSE5 will AMD diese Addition in einem Rutsch erledigen, innerhalb der Befehlspipeline.

MFG Bobo(2007)

Dresdenboy

Redaktion

☆☆☆☆☆☆

@N1truX & Bob beron

beron

Genau genommen hatte der K5 eine 3-Operanden-FPU und auch 3-Operanden-ALUs. Es ist bekannt, dass der Kern des K5 auf der Am 29000 RISC-Prozessor-Familie basierte, welche zu dieser Zeit eingestellt wurde. Diese RISC-CPU arbeitete mit 3-Operanden-Befehlen (http://www.amd.com/epd/29k/29kprog/29kprog.pdf).

Seit dem K6 (basierend auf dem Nx586) besteht kein solch offensichtlicher Zusammenhang des Kerns (nach den Decodern) zu einem vorhandenen CPU-Design. Aber schon eine effiziente Out-of-Order-Execution erfordert µOps, welche mit 3 Operanden arbeiten können.

Durch SSE5 (leider nicht schon in Form von TFP) wird so ein Feature für die x86-ISA zugänglich.

@alle

Mit ATI u. entspr. erworbenem Wissen hat SSE5 m.E. nichts zu tun. Was AMD da in die neuen Kerne bringen will, ist ja nun nichts Revolutionäres an sich. Nicht einmal für x86. Es werden im Prinzip nur die internen Möglichkeiten der Rechenwerke besser ausgenutzt u. geschickt erweitert. Eine FMAC-Operation ist nicht viel komplizierter als eine Multiplikation, da letztere ja schon ein paralleles Addieren sehr vieler Einzelwerte darstellt u. bei FMAC nun nur ein weiterer Wert hinzukommt.

Genau genommen hatte der K5 eine 3-Operanden-FPU und auch 3-Operanden-ALUs. Es ist bekannt, dass der Kern des K5 auf der Am 29000 RISC-Prozessor-Familie basierte, welche zu dieser Zeit eingestellt wurde. Diese RISC-CPU arbeitete mit 3-Operanden-Befehlen (http://www.amd.com/epd/29k/29kprog/29kprog.pdf).

Seit dem K6 (basierend auf dem Nx586) besteht kein solch offensichtlicher Zusammenhang des Kerns (nach den Decodern) zu einem vorhandenen CPU-Design. Aber schon eine effiziente Out-of-Order-Execution erfordert µOps, welche mit 3 Operanden arbeiten können.

Durch SSE5 (leider nicht schon in Form von TFP) wird so ein Feature für die x86-ISA zugänglich.

@alle

Mit ATI u. entspr. erworbenem Wissen hat SSE5 m.E. nichts zu tun. Was AMD da in die neuen Kerne bringen will, ist ja nun nichts Revolutionäres an sich. Nicht einmal für x86. Es werden im Prinzip nur die internen Möglichkeiten der Rechenwerke besser ausgenutzt u. geschickt erweitert. Eine FMAC-Operation ist nicht viel komplizierter als eine Multiplikation, da letztere ja schon ein paralleles Addieren sehr vieler Einzelwerte darstellt u. bei FMAC nun nur ein weiterer Wert hinzukommt.

cumec

Admiral Special

- Mitglied seit

- 03.05.2006

- Beiträge

- 1.305

- Renomée

- 19

- Standort

- Schüttorf / Niedersachsen

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- Simap, Spin

- Lieblingsprojekt

- Simap

- Meine Systeme

- Phenom X4 @ 3000MHz

- BOINC-Statistiken

- Folding@Home-Statistiken

- Details zu meinem Desktop

- Prozessor

- Phenom II X6 1075T @ 3900MHz

- Mainboard

- Gigabyte MA790GP-DS4H

- Kühlung

- Gelid Tranquillo

- Speicher

- 8GB PC 800

- Grafikprozessor

- Saphire HD4850 - 512mb

- Display

- ViewSonic VA2216w / Eizo Flexscan L695

- HDD

- 64GB OCZ Agility 2 / 1TB Samsung F3

- Optisches Laufwerk

- Samsung DVD-ROM 16x

- Soundkarte

- Onboard

- Gehäuse

- Chieftec Bravo BA-01

- Netzteil

- be quiet! Straight Power E5 500W

- Betriebssystem

- Win7 Professional 64bit / Ubuntu 64bit

- Webbrowser

- Fox 4

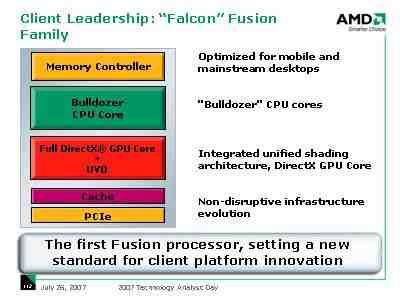

Hier nochmal Infos zum Sandtiger und die Bestätigung des octacore-designs.

Eine andere Frage die sich mir stellt ist, dass eine PCIe2.0 Anbindung direkt auf die DIE gelangen soll?

http://www.tomshardware.com/de/8-Core-CPU-Sandtiger-Falcon-AMD,news-239863.html

gruß

cumec

Eine andere Frage die sich mir stellt ist, dass eine PCIe2.0 Anbindung direkt auf die DIE gelangen soll?

http://www.tomshardware.com/de/8-Core-CPU-Sandtiger-Falcon-AMD,news-239863.html

gruß

cumec

Bobo_Oberon

Grand Admiral Special

- Mitglied seit

- 18.01.2007

- Beiträge

- 5.045

- Renomée

- 190

... Eine andere Frage die sich mir stellt ist, dass eine PCIe2.0 Anbindung direkt auf die DIE gelangen soll? ...

Quelle

MFG Bobo(2007)

Ragas

Grand Admiral Special

- Mitglied seit

- 24.05.2005

- Beiträge

- 4.470

- Renomée

- 85

- Details zu meinem Desktop

- Prozessor

- AMD Athlon 64 X2 3800+ @2520MHz; 1,4V; 53°C

- Mainboard

- Asus A8N-E

- Kühlung

- Thermaltake Sonic Tower (doppelt belüftet)

- Speicher

- 4x Infineon DDR400 512MB @207MHz

- Grafikprozessor

- Nvidia GeForce FX 7800GT

- Display

- 1.: 24", Samsung SyncMaster 2443BW, 1920x1200 TFT 2.: 19", Schneider, 1280x1024 CRT

- HDD

- Seagate Sata1 200GB 7200rpm, 2x250GB Seagate SATA2 im Raid0

- Optisches Laufwerk

- DVDBrenner LG GSA 4167

- Soundkarte

- Creative X-Fi Extreme Music

- Gehäuse

- Thermaltake Soprano Silber

- Netzteil

- Be-quiet! Darkpower 470W

- Betriebssystem

- Windows XP; Linux Mandriva 2007.1 (Kernel: 2.6.22.2 Ragas-Edition :D )

- Webbrowser

- Firefox

- Verschiedenes

- -Lüftersteuerung: Aerogate3

wird wohl für das umschalten zwischen integrierter und externet Grafikkarte benötigt.

rkinet

Grand Admiral Special

wieder: http://www.tomshardware.com/de/8-Core-CPU-Sandtiger-Falcon-AMD,news-239863.htmlDie ersten Fusion Inkarnationen werden wohl darauf hinauslaufen, dass man einfach eine per HT angebundene Ati Northbridge (mit IGP und PciE 2.0 Controller) mit auf das Cpu Package verpflanzt.

Fusion erscheint eher als Modifizierung des 'Sandtiger' & 'Shanghai'-Designs.

Statt 8-Cores eben 2, dann die 6M-L3 des Shanghai als ges. Cache für 2* CPU und 1*GPU zuordnen und PCIe 2.0 aus dem 'Sandtiger'-Design nehmen.

Da könnten durchaus kompakte DIEs enstehen.

Auch sind heutige Standard GPUs aus Nothbridge-Lösungen bzgl. Taktpotential eher mäßig ausgelegt, während 45nm/ Fusion eher bis 3 GHz ermöglichen würde.

Ich könnte mir vorstellen, daß AMD die SSE5 um SMT-Fähigkeiten erweitert und so der GPU virtuelle Recheneinheiten in größerer Zahl zur Verfügung stellen kann.

Sie mir also wie viel mehr Neudesign als nur Integration von etablierter Hardware auf einem DIE aus.

wieder: http://www.tomshardware.com/de/8-Core-CPU-Sandtiger-Falcon-AMD,news-239863.html

Fusion erscheint eher als Modifizierung des 'Sandtiger' & 'Shanghai'-Designs.

Statt 8-Cores eben 2, dann die 6M-L3 des Shanghai als ges. Cache für 2* CPU und 1*GPU zuordnen und PCIe 2.0 aus dem 'Sandtiger'-Design nehmen.

Da könnten durchaus kompakte DIEs enstehen.

Auch sind heutige Standard GPUs aus Nothbridge-Lösungen bzgl. Taktpotential eher mäßig ausgelegt, während 45nm/ Fusion eher bis 3 GHz ermöglichen würde.

Ich könnte mir vorstellen, daß AMD die SSE5 um SMT-Fähigkeiten erweitert und so der GPU virtuelle Recheneinheiten in größerer Zahl zur Verfügung stellen kann.

Sie mir also wie viel mehr Neudesign als nur Integration von etablierter Hardware auf einem DIE aus.

Später vielleicht, aber momentan ist es ziemlich sicher das zumindest Falcon ein MCM wird und das der GPU-Teil bei TSMC gefertigt wird.

http://www.digitimes.com/bits_chips/a20070806PD201.html

G

gast_003

Guest

Was soll GDD3 sein und was hat das bei ner Server CPU verloren?

Bei google habe ich das nur im Zusammenhang mit Grafikkarten gefunden und gehe deshalb mal davon aus das es GDDR3 Grafikspeicher sein soll....wo wir jetzt wieder beim Thema "Was hat das bei ner Server CPU verloren?" wären.

Entweder hat der 8 Kern einen Grafikkern ohne integrierten Grafikspeicher mit drin, es soll DDR3 Speicher sein oder es ist schlicht Blödsinn.

Bei google habe ich das nur im Zusammenhang mit Grafikkarten gefunden und gehe deshalb mal davon aus das es GDDR3 Grafikspeicher sein soll....wo wir jetzt wieder beim Thema "Was hat das bei ner Server CPU verloren?" wären.

Entweder hat der 8 Kern einen Grafikkern ohne integrierten Grafikspeicher mit drin, es soll DDR3 Speicher sein oder es ist schlicht Blödsinn.

Opteron

Redaktion

☆☆☆☆☆☆

Nachdem ich grad nach Links für das "AMD will Quimonda(Infinieon) kaufen" Gerücht gesucht hat, hat mir google noch was zu G3MX ausgespuckt:

http://www.hothardware.com/News/More_AMD_G3MX_Details_Emerge/

Darin gehts um eine "Hydra" CPU, die 4 Speicherkanäle hat und daran dann DDR3(-1600) anspricht. Hört sich nach ner geballten Ladung Bandbreite an ^^

Naja die Kerne werden sicherlich Bulldozer sein, also wollt ich das hier mal erwähnen

Weiterer Vorteil der Lösung ... die CPU ist wieder unabhängig vom Speicherstandard. Dort wird nur der modifizierte HT3 Anschluss verbaut, das DDR2/DDR3/DDR4/DDRX Interface sitzt im externen G3MX chip.

ciao

Alex

http://www.hothardware.com/News/More_AMD_G3MX_Details_Emerge/

Darin gehts um eine "Hydra" CPU, die 4 Speicherkanäle hat und daran dann DDR3(-1600) anspricht. Hört sich nach ner geballten Ladung Bandbreite an ^^

Naja die Kerne werden sicherlich Bulldozer sein, also wollt ich das hier mal erwähnen

Weiterer Vorteil der Lösung ... die CPU ist wieder unabhängig vom Speicherstandard. Dort wird nur der modifizierte HT3 Anschluss verbaut, das DDR2/DDR3/DDR4/DDRX Interface sitzt im externen G3MX chip.

ciao

Alex

Zuletzt bearbeitet:

LinuS

Vice Admiral Special

Dürfte der Vorteil der Unabhängigkeit ggü Speicherstandards aber nicht mit deutlich erhöhten Latenzen erkauft werden? Ich mein, so als Laie denk ich mal: "Super, der G3MX ist ein "Umweg" ähnlich dem externen Speichercontroler von früher" Naja, wahrscheinlich zählen im Servergeschäft Latenzen nicht so viel wie pure Bandbreite

btw: theinquirer @träummodus http://uk.theinquirer.net/?article=42282 was mich stutzig macht ist folgendes:

http://uk.theinquirer.net/?article=42282 was mich stutzig macht ist folgendes:

btw: theinquirer @träummodus

http://uk.theinquirer.net/?article=42282 was mich stutzig macht ist folgendes:

http://uk.theinquirer.net/?article=42282 was mich stutzig macht ist folgendes:

irgendwie hört sich das für mich widersprüchlichan. Zum einem soll der Fusion einen Grafikpart basierend auf r700 bekommenbut all that we can tell you now is that the AMD Fusion processor will be consisted out of one, two, three, four Bulldozer cores and a graphics part based on R700 architecture.

The name R700 was not mentioned anywhere, but has support for DirectX 10.1 API and second-generation UVD on one of the slides. AMD does not want to confirm the actual specs at the moment, but it is certain that this will not be a R600/700 design, but rather something new.

zum anderen wird dies aber wieder "dementiert":and a graphics part based on R700 architecture.

it is certain that this will not be a R600/700 design, but rather something new.

Zuletzt bearbeitet:

HenryWince

Vice Admiral Special

@Opteron

So weit geht G3MX nicht! Der Memorycontroller bleibt in der CPU, nur der DRAM-Controller wird auf die G3MX Chips ausgelagert (Siehe auch Pressemitteilung von Inphi zum IN16KXMX).

@LinuS

Bei G3MX geht es in erster Linie um hohe Memorykapazität bei moderatem Energieverbrauch. Die Konkurenz von G3MX ist FB-DIMM.

Unterschiede sind:

* FB-DIMM:

- 1 Buffer Chip pro DIMM Modul (der verbrät ganz schön Energie!)

- Die (Transfer-)Latenz steigt linear mit der Anzahl der Speicher-Module (=>Daisy-Chainig).

- Auf den FB-DIMM Modulen werden zwar DDR2/3 Chips verbaut, aber die Module selbst sind nicht Massenmarkttauglich => hoher Preis.

* G3MX:

- 1 Buffer für je 4 DIMM-Module

- Etwas höhere Latenz als direkt angebundene DDR3 Module

- Einsatz von normalen DDR3 Modulen (geringere Kosten!)

Höhere Bandbreiten, durch mehr mögliche Kanäle, sind ein gern gesehener Nebeneffekt.

Bezüglich des Grafikcores würde ich es so interpretieren: Die Grafikeinheit ist vom Aufbau her ähnlich zum R700, aber von der Implementierung nicht identisch. Das könnte z.B. einfach daran liegen, dass AMD Fusion nicht als MCM sondern als monolithischen Chip entwickelt.

Weiterer Vorteil der Lösung ... die CPU ist wieder unabhängig vom Speicherstandard.

So weit geht G3MX nicht! Der Memorycontroller bleibt in der CPU, nur der DRAM-Controller wird auf die G3MX Chips ausgelagert (Siehe auch Pressemitteilung von Inphi zum IN16KXMX).

@LinuS

Bei G3MX geht es in erster Linie um hohe Memorykapazität bei moderatem Energieverbrauch. Die Konkurenz von G3MX ist FB-DIMM.

Unterschiede sind:

* FB-DIMM:

- 1 Buffer Chip pro DIMM Modul (der verbrät ganz schön Energie!)

- Die (Transfer-)Latenz steigt linear mit der Anzahl der Speicher-Module (=>Daisy-Chainig).

- Auf den FB-DIMM Modulen werden zwar DDR2/3 Chips verbaut, aber die Module selbst sind nicht Massenmarkttauglich => hoher Preis.

* G3MX:

- 1 Buffer für je 4 DIMM-Module

- Etwas höhere Latenz als direkt angebundene DDR3 Module

- Einsatz von normalen DDR3 Modulen (geringere Kosten!)

Höhere Bandbreiten, durch mehr mögliche Kanäle, sind ein gern gesehener Nebeneffekt.

Bezüglich des Grafikcores würde ich es so interpretieren: Die Grafikeinheit ist vom Aufbau her ähnlich zum R700, aber von der Implementierung nicht identisch. Das könnte z.B. einfach daran liegen, dass AMD Fusion nicht als MCM sondern als monolithischen Chip entwickelt.

nazgul99

Grand Admiral Special

- Mitglied seit

- 01.05.2005

- Beiträge

- 3.592

- Renomée

- 224

- Standort

- Irgendwo in der Nähe

- Mein Laptop

- ThinkPad Edge E145 / 8GB / M500 480GB / Kubuntu /// Asus U38N / 6GB / Matt / Postville / Kubuntu/W8

- Details zu meinem Desktop

- Prozessor

- AMD A10-7800

- Mainboard

- MSI A88XI AC

- Kühlung

- Scythe Shuriken Rev.2

- Speicher

- 2x 8GB DDR3-2133

- Grafikprozessor

- IGP

- Display

- HP LP2465, MVA, 1920x1200, 24"

- SSD

- Samsung 850 EVO 500GB

- HDD

- ST9500325AS 500GB

- Optisches Laufwerk

- ja, so'n USB-Dings

- Soundkarte

- onboard, optisch -> SMSL Q5 PRO -> ELAC EL60

- Gehäuse

- Silverstone ML06B

- Netzteil

- SST-ST30SF

- Betriebssystem

- Kubuntu

- Webbrowser

- Firefox

- Verschiedenes

- Synology DS414slim 3x 1,5 TB RAID5

@HenryWince: stimme deinen Ausführungen zu.

Mit ungefähr gleicher Pinzahl für Ram wie bisher lassen sich so doppelt so viele Speicherkanäle anbinden -> doppelte Bandbreite je CPU-Sockel möglich (und auch sehr wichtig: doppelte Kapazität). Das ist bei 8 oder mehr Kernen je CPU auch ratsam. Wenn Suns Niagara (und IBM Power 7(?)) auf demselben Sockel laufen soll ohnehin, der nutzt heute schon 4 Speicherkanäle. Hothardware hat einen interessanten Artikel dazu.

Ich hatte auch erst gedacht, AMD würde den Memory-Controller wieder aus der CPU schmeißen, ist aber offenbar nicht der Fall. Witzig ist, daß der Downlink vom Ram 20 Lanes breit sein soll, während der Uplink nur 13 Lanes zählt. Ich vermute, daß AMD ermittelt hat, wie groß der Traffic vom/zum Ram typischerweise ist und die Lanes entsprechend asymmetrisch aufgeteilt. Groovy 8)

13 + 20 Lanes * 4 Kanäle ergibt 132 differnezielle Datenleitungen, bei 2x 64bit Ram sind's 128 solcher Paare, was jeweils noch an Steuerleitungen hinzukommt, weiß ich nicht.

* G3MX:

- 1 Buffer für je 4 DIMM-Module

- Etwas höhere Latenz als direkt angebundene DDR3 Module

- Einsatz von normalen DDR3 Modulen (geringere Kosten!)

Höhere Bandbreiten, durch mehr mögliche Kanäle, sind ein gern gesehener Nebeneffekt.

Mit ungefähr gleicher Pinzahl für Ram wie bisher lassen sich so doppelt so viele Speicherkanäle anbinden -> doppelte Bandbreite je CPU-Sockel möglich (und auch sehr wichtig: doppelte Kapazität). Das ist bei 8 oder mehr Kernen je CPU auch ratsam. Wenn Suns Niagara (und IBM Power 7(?)) auf demselben Sockel laufen soll ohnehin, der nutzt heute schon 4 Speicherkanäle. Hothardware hat einen interessanten Artikel dazu.

HotHardware-Artikel schrieb:The processors will still feature an on-die memory controller, but unlike current platforms it will be geared for DDR3 memory. The processors will interface with one or more G3MX chips, which in turn are connected to the memory ports. G3MX will act as a memory port extender for the memory controller in the CPU socket and provides a serial link to the RAM. Also, the electrical signaling between the memory controller and G3MX is based on HyperTransport 3.0.

Ich hatte auch erst gedacht, AMD würde den Memory-Controller wieder aus der CPU schmeißen, ist aber offenbar nicht der Fall. Witzig ist, daß der Downlink vom Ram 20 Lanes breit sein soll, während der Uplink nur 13 Lanes zählt. Ich vermute, daß AMD ermittelt hat, wie groß der Traffic vom/zum Ram typischerweise ist und die Lanes entsprechend asymmetrisch aufgeteilt. Groovy 8)

13 + 20 Lanes * 4 Kanäle ergibt 132 differnezielle Datenleitungen, bei 2x 64bit Ram sind's 128 solcher Paare, was jeweils noch an Steuerleitungen hinzukommt, weiß ich nicht.

Zuletzt bearbeitet:

Bobo_Oberon

Grand Admiral Special

- Mitglied seit

- 18.01.2007

- Beiträge

- 5.045

- Renomée

- 190

Der Niagara 1 und Niagara 2 sind fertige Produkte, selbst der Victoria Falls (Multisockel Niagara) ist fertig und sie werden nicht auf dem AMD-Sockel erscheinen. Sun hat für den Niagara 2 FB-DIMM eingeplant.... Wenn Suns Niagara (und IBM Power 7(?)) auf demselben Sockel laufen soll ohnehin, der nutzt heute schon 4 Speicherkanäle. ...

Auch bei IBM wird das Interesse an einem herstellerübergreifenden Sockel kaum, bis wenig vorhanden sein. Bislang hat IBM fleissig an dem PowerPC-Sockel nur an die eigenen Linien gedacht.

IBM treibt es ganz besonders bunt mit den verschiedensten Bussen/Links ... die sind auch im PCI-Express-Boot bei Intels Geneso drin.

In der damaligen Presseerklärung von Inphi ist tatsächlich von einer Seriellen Schnittstelle die Rede, die vom AMD-Prozessor zu dem 3GM-Extender verlegt ist.

MFG Bobo(2007)

nazgul99

Grand Admiral Special

- Mitglied seit

- 01.05.2005

- Beiträge

- 3.592

- Renomée

- 224

- Standort

- Irgendwo in der Nähe

- Mein Laptop

- ThinkPad Edge E145 / 8GB / M500 480GB / Kubuntu /// Asus U38N / 6GB / Matt / Postville / Kubuntu/W8

- Details zu meinem Desktop

- Prozessor

- AMD A10-7800

- Mainboard

- MSI A88XI AC

- Kühlung

- Scythe Shuriken Rev.2

- Speicher

- 2x 8GB DDR3-2133

- Grafikprozessor

- IGP

- Display

- HP LP2465, MVA, 1920x1200, 24"

- SSD

- Samsung 850 EVO 500GB

- HDD

- ST9500325AS 500GB

- Optisches Laufwerk

- ja, so'n USB-Dings

- Soundkarte

- onboard, optisch -> SMSL Q5 PRO -> ELAC EL60

- Gehäuse

- Silverstone ML06B

- Netzteil

- SST-ST30SF

- Betriebssystem

- Kubuntu

- Webbrowser

- Firefox

- Verschiedenes

- Synology DS414slim 3x 1,5 TB RAID5

Ob Sun und IBM tatsächlich Infrastruktur mit AMD teilen wollen, werden wir sehen. Bei POWER(5/6/7?) scheint mir das noch unwahrscheinlicher als bei Niagara(1/2/3?), aber über die die POWER-CPUs umgebende Infrastruktur weiß ich auch so gut wie nichts. Selbstverständlich müßten jene CPUs (zumindest bestimmte Ableger) der beiden Hersteller und AMDs auf gemeinsame Interconnects gebracht werden, dafür hätten sie IIRC noch knapp 2 Jahre Zeit. Aber ob das tatsächlich passiert, ob vielleicht doch kein gemeinsamer Sockel, sondern z.B. nur HT-Nutzung bei Sun und/oder IBM dabei rauskommt (für Multi-Sockel bei Sun nächstes Jahr bietet sich's ja wirklich an), oder alles nur heiße Luft war, wer weiß...

Interessant wär's jedenfalls! Und zwischen DEC und AMD hat's das ja auch gegeben (EV6-Bus), in Compaqs kleinsten Servern tauchte sogar AMDs Irongate-Chipsatz (ich meine, der war's) auf. Einen gemeinsamen Sockel/Slot gab's dann doch nie, wird wohl auch niemand mehr herausbekommen, ob der wirklich geplant war. Dec nannte seinen IIRC Slot-B, klingt ja immerhin sehr verwandt zum Slot-A AMDs. (Edit: Hab da was zum Thema gefunden: http://findarticles.com/p/articles/mi_m0CGN/is_3690/ai_54997669 - ein Artikel vom 25. Juni 1999. Dort munkelt man, AMD plane eine "Slot B version of Athlon late this year")

Interessant wär's jedenfalls! Und zwischen DEC und AMD hat's das ja auch gegeben (EV6-Bus), in Compaqs kleinsten Servern tauchte sogar AMDs Irongate-Chipsatz (ich meine, der war's) auf. Einen gemeinsamen Sockel/Slot gab's dann doch nie, wird wohl auch niemand mehr herausbekommen, ob der wirklich geplant war. Dec nannte seinen IIRC Slot-B, klingt ja immerhin sehr verwandt zum Slot-A AMDs. (Edit: Hab da was zum Thema gefunden: http://findarticles.com/p/articles/mi_m0CGN/is_3690/ai_54997669 - ein Artikel vom 25. Juni 1999. Dort munkelt man, AMD plane eine "Slot B version of Athlon late this year")

Aus dem oben verlinkten HotHardware-Artikel:In der damaligen Presseerklärung von Inphi ist tatsächlich von einer Seriellen Schnittstelle die Rede, die vom AMD-Prozessor zu dem 3GM-Extender verlegt ist.

Meinst du das?Also, the electrical signaling between the memory controller and G3MX is based on HyperTransport 3.0.

Zuletzt bearbeitet:

Bobo_Oberon

Grand Admiral Special

- Mitglied seit

- 18.01.2007

- Beiträge

- 5.045

- Renomée

- 190

Ich rate zur Vorsicht, ob die Zusammenarbeit im HyperTransport-Konsortium jenseits von der x86-64-Plattform weitergeht.

Sun setzt ganz auf Open Source und Zusammenarbeit zu Produkten, die die UltraSPARCs zusätzliche Fähigkeiten geben. Der Entwurf eines Niagara 1 mit einem FPGA auf dem gleichen Die ist solch ein Produkt.

Die Zusammenarbeit mit DEC ist schon deswegen nicht vergleichbar, weil AMD das EV-6 Protokoll für die K7 lizensierte und mit einer Ausgründung von DEC das HyperTransport-Protokoll zusammen entwarfen.

In dem PDF von Inphi ist nicht explizit die Rede von HyperTransport, sondern es ist dort "lediglich" die Rede von einem seriellen Datenprotokoll mit einer Bandbreite von derzeit 6 GB/s Bandbreite und mehr.

MFG Bobo(2007)

Sun setzt ganz auf Open Source und Zusammenarbeit zu Produkten, die die UltraSPARCs zusätzliche Fähigkeiten geben. Der Entwurf eines Niagara 1 mit einem FPGA auf dem gleichen Die ist solch ein Produkt.

Die Zusammenarbeit mit DEC ist schon deswegen nicht vergleichbar, weil AMD das EV-6 Protokoll für die K7 lizensierte und mit einer Ausgründung von DEC das HyperTransport-Protokoll zusammen entwarfen.

In dem PDF von Inphi ist nicht explizit die Rede von HyperTransport, sondern es ist dort "lediglich" die Rede von einem seriellen Datenprotokoll mit einer Bandbreite von derzeit 6 GB/s Bandbreite und mehr.

MFG Bobo(2007)

Zuletzt bearbeitet:

NeuerBenutzer

Fleet Captain Special

- Mitglied seit

- 09.12.2005

- Beiträge

- 324

- Renomée

- 6

- Standort

- Saarland

- Details zu meinem Desktop

- Prozessor

- Intel Pentium 4 3000 MHz

- Mainboard

- ABIT IC7-G

- Kühlung

- Intel Boxed

- Speicher

- 2 x 512 MB PC3200 MDT

- Grafikprozessor

- ATI Radeon 9200 (Sapphire)

- Display

- Samsung SyncMaster 957p

- HDD

- Seagate 120 GB

- Optisches Laufwerk

- CD-ROM

- Soundkarte

- OnBoard

- Gehäuse

- Chenbro Big-Tower

- Netzteil

- NoName 350W

- Betriebssystem

- Microsoft Windows 2000 Professional

- Webbrowser

- SeaMonkey 1.1.11

- Auf den FB-DIMM Modulen werden zwar DDR2/3 Chips verbaut, aber die Module selbst sind nicht Massenmarkttauglich => hoher Preis.

Also laut diesem Artikel verbaut Intel, IBM und Sun FB-DIMM - wie kann man da von nicht Massenmarkttauglich sprechen??

Da sind eher die Registered DDR2/3-Module von AMD nicht Massenmarkttauglich, denn die werden nur noch von AMD benutzt. Die alten Sockel 604 Xeon gibt es ja nicht mehr zu kaufen.

Opteron

Redaktion

☆☆☆☆☆☆

Ahhh Der Unterscheid zw. Memory und DRAM Kontroller ... alles klar jetzt, hatte mich schon gewundertSo weit geht G3MX nicht! Der Memorycontroller bleibt in der CPU, nur der DRAM-Controller wird auf die G3MX Chips ausgelagert ...

Mittlerweile "geht" der Preis, wobei das wohl Ansichtssache ist (ca. 20-30 Euro teurer) aber beim nem dicken Server sollte das egal sein, schlimmer ist der Punkt mit dem Energieverbraten .. ;-(Auf den FB-DIMM Modulen werden zwar DDR2/3 Chips verbaut, aber die Module selbst sind nicht Massenmarkttauglich => hoher Preis.

Prinzipiell richtig, aber jeder jammert über FBD, einziger Vorteil ist bei dem Konzept, dass man halt üppig Pins für den Speicher gegenüber einem DDR Interface spart. Aber G3MX schafft das eben jetzt auch, und hat nicht die von HenryWince genannten Nachteile. Selbst Intel will da wieder weg davon, es kommt demnächst z.B. auch ein neuer Einsiegs-Xeon-Chipsatz für reg. DDR2 raus:Also laut diesem Artikel verbaut Intel, IBM und Sun FB-DIMM - wie kann man da von nicht Massenmarkttauglich sprechen??

Da sind eher die Registered DDR2/3-Module von AMD nicht Massenmarkttauglich, denn die werden nur noch von AMD benutzt. Die alten Sockel 604 Xeon gibt es ja nicht mehr zu kaufen.

http://www.theinquirer.net/default.aspx?article=42183

@Sun, IBM, Sockel teilen:

Bin z.Zt. wieder kritischer was das anbelangt. Sun T2 hat jetzt 4 FBDIMM Kanäle und die versorgen bis zu 64 threads (8 echte Kerne). In der SMP Version Victoria Falls sinds nur 2 FBD Kanäle, nächstes Jahr kommt Rock mit 16 Kernen und 32 threads, da sollten die 4 Kanäle auch noch reichen, aber 2009 .. wenn AMD dann auch 8 Kerne haben will, da hat Sun dann doch sicherlich auch wieder mehr Kerne @45nm, da brauchen die wieder mehr RAM-Bandbreite ... ausschließen möchte ich einen gemeinsamen Sockel nicht, man könnte ja mit Suns Wünschen designen z.B. 8 Kanäle ... und bei AMD liegen dann 4 davon brach .. aber naja auch irgendwie unpraktisch.

ciao

Alex

Zuletzt bearbeitet:

Opteron

Redaktion

☆☆☆☆☆☆

Damit hier auch mal wieder was steht

http://www.theinquirer.net/default.aspx?article=42484

Fragt sich nur, ob dass das gleiche "won't" wie bei AMD64 ist. Wohl eher nicht, SSE5 ist nicht soo bedeutend, v.a. auch nur für HPC nötig, aber dennoch ne interessante Meldung.

Wenigstens die FPU Krone sollte AMD also ~2009 sicher sein, und Intel wird / muss dann wohl den Itanium dagegen setzen. Aber irgendwie kommt mir ein einzelner Nehalem Core ziemlich "groß" gegenüber einen 65nm Vertreter vor, und ich mein jetzt nicht den Cache ..

Warten wirs ab

Alex

http://www.theinquirer.net/default.aspx?article=42484

Fragt sich nur, ob dass das gleiche "won't" wie bei AMD64 ist. Wohl eher nicht, SSE5 ist nicht soo bedeutend, v.a. auch nur für HPC nötig, aber dennoch ne interessante Meldung.

Wenigstens die FPU Krone sollte AMD also ~2009 sicher sein, und Intel wird / muss dann wohl den Itanium dagegen setzen. Aber irgendwie kommt mir ein einzelner Nehalem Core ziemlich "groß" gegenüber einen 65nm Vertreter vor, und ich mein jetzt nicht den Cache ..

Warten wirs ab

Alex

p4z1f1st

Grand Admiral Special

- Mitglied seit

- 28.04.2003

- Beiträge

- 9.722

- Renomée

- 81

- Details zu meinem Desktop

- Prozessor

- AMD FX-6300

- Mainboard

- Gigabyte GA-970A-UD3

- Kühlung

- HEATKILLER® CPU Rev3.0 LC + HEATKILLER® GPU-X² 69x0 LT

- Speicher

- 2x 4096 MB G.Skill RipJawsX DDR3-1600 CL7

- Grafikprozessor

- AMD Radeon RX 480 8GB

- Display

- Dell U2312HM

- HDD

- Crucial m4 SSD 256GB

- Optisches Laufwerk

- Sony Optiarc AD-7260S

- Soundkarte

- Creative Labs SB Audigy 2 ZS

- Gehäuse

- Chieftec Scorpio TA-10B-D (BxHxT: 205x660x470mm)

- Netzteil

- Seasonic X-Series X-660

- Betriebssystem

- Microsoft Windows 10 Professional 64bit

- Webbrowser

- Mozilla Firefox

- Verschiedenes

- Watercool HTF2 Dual + 2x Papst 4412 F/2GL

Kann mir mal einer den tieferen Sinn dieses Textes erklären?

"Please pull your knob straight out of the wall to turn on water"

Ich meine, übersetzen kann ich mir den Satz schon, nur verstehe ich den das Sinnbild des Spruchs nicht

"Please pull your knob straight out of the wall to turn on water"

Ich meine, übersetzen kann ich mir den Satz schon, nur verstehe ich den das Sinnbild des Spruchs nicht

nazgul99

Grand Admiral Special

- Mitglied seit

- 01.05.2005

- Beiträge

- 3.592

- Renomée

- 224

- Standort

- Irgendwo in der Nähe

- Mein Laptop

- ThinkPad Edge E145 / 8GB / M500 480GB / Kubuntu /// Asus U38N / 6GB / Matt / Postville / Kubuntu/W8

- Details zu meinem Desktop

- Prozessor

- AMD A10-7800

- Mainboard

- MSI A88XI AC

- Kühlung

- Scythe Shuriken Rev.2

- Speicher

- 2x 8GB DDR3-2133

- Grafikprozessor

- IGP

- Display

- HP LP2465, MVA, 1920x1200, 24"

- SSD

- Samsung 850 EVO 500GB

- HDD

- ST9500325AS 500GB

- Optisches Laufwerk

- ja, so'n USB-Dings

- Soundkarte

- onboard, optisch -> SMSL Q5 PRO -> ELAC EL60

- Gehäuse

- Silverstone ML06B

- Netzteil

- SST-ST30SF

- Betriebssystem

- Kubuntu

- Webbrowser

- Firefox

- Verschiedenes

- Synology DS414slim 3x 1,5 TB RAID5

Mike erzählt gern Anekdoten. Wahrscheinlich irgendwas mit nem verfrickelten (und vom sog. "engeneer" (lies: Monktör) wieder heilgefrickelten) WasserhahnKann mir mal einer den tieferen Sinn dieses Textes erklären?

"Please pull your knob straight out of the wall to turn on water"

Ich meine, übersetzen kann ich mir den Satz schon, nur verstehe ich den das Sinnbild des Spruchs nicht

Ragas

Grand Admiral Special

- Mitglied seit

- 24.05.2005

- Beiträge

- 4.470

- Renomée

- 85

- Details zu meinem Desktop

- Prozessor

- AMD Athlon 64 X2 3800+ @2520MHz; 1,4V; 53°C

- Mainboard

- Asus A8N-E

- Kühlung

- Thermaltake Sonic Tower (doppelt belüftet)

- Speicher

- 4x Infineon DDR400 512MB @207MHz

- Grafikprozessor

- Nvidia GeForce FX 7800GT

- Display

- 1.: 24", Samsung SyncMaster 2443BW, 1920x1200 TFT 2.: 19", Schneider, 1280x1024 CRT

- HDD

- Seagate Sata1 200GB 7200rpm, 2x250GB Seagate SATA2 im Raid0

- Optisches Laufwerk

- DVDBrenner LG GSA 4167

- Soundkarte

- Creative X-Fi Extreme Music

- Gehäuse

- Thermaltake Soprano Silber

- Netzteil

- Be-quiet! Darkpower 470W

- Betriebssystem

- Windows XP; Linux Mandriva 2007.1 (Kernel: 2.6.22.2 Ragas-Edition :D )

- Webbrowser

- Firefox

- Verschiedenes

- -Lüftersteuerung: Aerogate3

So jetzt reibt die Nachricht genügend DAUs unter die Nase und Intels verkäufe fallen. XD

mtb][sledgehammer

Grand Admiral Special

- Mitglied seit

- 11.11.2001

- Beiträge

- 4.375

- Renomée

- 30

- Mein Laptop

- HP Compaq nx6125

- Details zu meinem Desktop

- Prozessor

- Athlon XP 2500+

- Mainboard

- Asrock K7S8XE

- Kühlung

- AC / selfmade Wakü

- Speicher

- 1 GB PC3200 Team Memory

- Grafikprozessor

- ATI Radeon 9500

- Display

- 20,1'' Samsung SyncMaster 205BW 1680x1050

- HDD

- Samsung SV0802N

- Optisches Laufwerk

- Toshiba DVD-ROM SD-M1612

- Soundkarte

- Creative SB Live! Player 1024

- Gehäuse

- Chenbro Net Server Tower

- Netzteil

- Coba 400 Watt (silent)

- Betriebssystem

- Windows XP, Ubuntu Linux

- Webbrowser

- Mozilla Firefox

- Verschiedenes

- knc TV Station , Terratec Cinergy 1200 DVB-C

Also Multiply-Add (MA) Operationenbraucht man eigentlich überall. Angefangen bei JPG, über MP3 und Video. In diesen drei Anwendungen gibts eigentlich ausschließlich Fast-Fourier Transformationen (FFT), die am schnellsten mit MA Befehlen durchgeführt werden.Damit hier auch mal wieder was steht

http://www.theinquirer.net/default.aspx?article=42484

Fragt sich nur, ob dass das gleiche "won't" wie bei AMD64 ist. Wohl eher nicht, SSE5 ist nicht soo bedeutend, v.a. auch nur für HPC nötig, aber dennoch ne interessante Meldung.

Bei anderen Anwendungen weiß ich leider nicht 100% bescheid. Aber auch dort ist die Kombination aus Multiplikation und Addtition IMO keine Seltenheit. Ergo bringt SSE5 auch dem Privatanwender eine Menge.

Ragas

Grand Admiral Special

- Mitglied seit

- 24.05.2005

- Beiträge

- 4.470

- Renomée

- 85

- Details zu meinem Desktop

- Prozessor

- AMD Athlon 64 X2 3800+ @2520MHz; 1,4V; 53°C

- Mainboard

- Asus A8N-E

- Kühlung

- Thermaltake Sonic Tower (doppelt belüftet)

- Speicher

- 4x Infineon DDR400 512MB @207MHz

- Grafikprozessor

- Nvidia GeForce FX 7800GT

- Display

- 1.: 24", Samsung SyncMaster 2443BW, 1920x1200 TFT 2.: 19", Schneider, 1280x1024 CRT

- HDD

- Seagate Sata1 200GB 7200rpm, 2x250GB Seagate SATA2 im Raid0

- Optisches Laufwerk

- DVDBrenner LG GSA 4167

- Soundkarte

- Creative X-Fi Extreme Music

- Gehäuse

- Thermaltake Soprano Silber

- Netzteil

- Be-quiet! Darkpower 470W

- Betriebssystem

- Windows XP; Linux Mandriva 2007.1 (Kernel: 2.6.22.2 Ragas-Edition :D )

- Webbrowser

- Firefox

- Verschiedenes

- -Lüftersteuerung: Aerogate3

Trotzdem stellt sich die Frage in wieweit AMD in der Lage sein wird die IPC des K11 gegenüber dem K10 zu verbessern.

Jetzt da man nach ersten Tests eine wesentlich bessere Übersicht hat kann man sagen, dass die bisher bekannten Verbesserungen und auch das Fusion-Konzept des K11 wohl nicht ausreichen werden um den K11 gegenüber eine neuen Intel-Architektur (mit der es der K11 auf jeden Fall zu tun bekommt, nach Intels Zeitplan Ende ´08 ) konkurrenzfähiger zu machen als es der K10 derzeit gegenüber Conroe/Penryn ist.

Da wird AMD definitiv ein bisschen mehr aus dem Stiefel zaubern müssen.

Ich glaube nicht, dass Fusion die einzige Neuerung am K11 sein wird.

Zudem macht der K10 derzeit noch keinen ausgereiften Eindruck, ich kann mir durchaus vorstellen, dass er bis zum nächsten stepping zum Conroe aufschließen kann. Natürlich auf die gefahr hin, dass Intel dann schonwieder einen schritt weiter ist.

goldmund

Fleet Captain Special

Viel Gesabbel ohne Inhalt.(keinerlei Begründung außer die derzeitge Situation) Trotz Verwendung des Konjunktivs.Trotzdem stellt sich die Frage in wieweit AMD in der Lage sein wird die IPC des K11 gegenüber dem K10 zu verbessern.

Jetzt da man nach ersten Tests eine wesentlich bessere Übersicht hat kann man sagen, dass die bisher bekannten Verbesserungen und auch das Fusion-Konzept des K11 wohl nicht ausreichen werden um den K11 gegenüber eine neuen Intel-Architektur (mit der es der K11 auf jeden Fall zu tun bekommt, nach Intels Zeitplan Ende ´08 ) konkurrenzfähiger zu machen als es der K10 derzeit gegenüber Conroe/Penryn ist.

Da wird AMD definitiv ein bisschen mehr aus dem Stiefel zaubern müssen.

Stellt sich die Frage inwieweit Intel die IPC noch verbessert.

Ähnliche Themen

- Antworten

- 1

- Aufrufe

- 292

- Antworten

- 1

- Aufrufe

- 227

- Antworten

- 1

- Aufrufe

- 492

- Antworten

- 0

- Aufrufe

- 865