App installieren

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: This feature may not be available in some browsers.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

AMD RDNA2 / Navi-2 und "Bignavi"

- Ersteller BavarianRealist

- Erstellt am

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 5.050

- Renomée

- 496

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Samsung, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

GL2a | GL2 Arbiter | == TCA (Navi10 = 4, Navi14 = 2) |

GL2c | | == TCC (Navi10 = 16, Navi14 =8 ) |

TC | Texture Cache? | |

TCC | Texture Channel Cache? |

Berniyh

Grand Admiral Special

- Mitglied seit

- 29.11.2005

- Beiträge

- 5.240

- Renomée

- 232

Ich denke es heißt "Global L2 Arbiter" und ist quasi eine Art Switch/Verwaltungseinheit für den L2 Cache, den sich bei RDNA ja alle CUs teilen. Zumindest findet man zum Thema "L2 Arbiter" Patente, u.a. von Intel. Das scheint also schon ein gängiger Begriff zu sein.

TCA dürfte dann "Texture Channel Arbiter" sein.

GL2C ist entsprechend dann "Global L2 Cache" und TCC bekanntlich "Texture Channel Cache".

GL2A gibt es auch bei Navi 10 schon, allerdings kenn wir keine Zahlen. Da Navi 21 Lite aber wohl ein Zwischenschritt hin zu RDNA2 war (für die XBox) würde ich mal vermuten, dass Navi 10 genauso wie Navi 21 Lite 4 GL2A hat und damit doppelt so viele wie Navi 22 bei gleicher Anzahl an Shader Engines (2).

Ist aber spekulativ.

Interessant übrigens auch dabei, dass die RDNA APUs gleich viele GL2A wie Navi 21 und doppelt so viele wie Navi 22 haben, bei nur einer SE.

Wird der Cache hier ggf. auch mit den CPU Cores geteilt?

[automerge]1602089501[/automerge]

TCA dürfte dann "Texture Channel Arbiter" sein.

GL2C ist entsprechend dann "Global L2 Cache" und TCC bekanntlich "Texture Channel Cache".

GL2A gibt es auch bei Navi 10 schon, allerdings kenn wir keine Zahlen. Da Navi 21 Lite aber wohl ein Zwischenschritt hin zu RDNA2 war (für die XBox) würde ich mal vermuten, dass Navi 10 genauso wie Navi 21 Lite 4 GL2A hat und damit doppelt so viele wie Navi 22 bei gleicher Anzahl an Shader Engines (2).

Ist aber spekulativ.

Interessant übrigens auch dabei, dass die RDNA APUs gleich viele GL2A wie Navi 21 und doppelt so viele wie Navi 22 haben, bei nur einer SE.

Wird der Cache hier ggf. auch mit den CPU Cores geteilt?

[automerge]1602089501[/automerge]

Hab vergessen den Link hinzuzufügen, danke fürs Nachholen.Haben wir im 3DC inzwischen aufgelöst. GL2A steht für "GL2 Arbiter". Das sagt mir zwar auch nicht sonderlich viel und "GL2" ist damit immer noch nicht geklärt, aber egal …

Dazu von coelacanth

AMDGPU関連用語略称まとめ | Coelacanth's Dream

www.coelacanth-dream.com

Er hat eh einige nette Sammlungen auch zu AMD CPUs Dali, Pollock usw.

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 5.050

- Renomée

- 496

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Samsung, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Steht doch in der Tabelle für Navi 10 und Navi 14

Berniyh

Grand Admiral Special

- Mitglied seit

- 29.11.2005

- Beiträge

- 5.240

- Renomée

- 232

Stimmt, die Zahlen hab ich mir gar nicht angeschaut. Danke dir.

Ja, dann haben sie die GL2A tatsächlich um einen Faktor 2 reduziert. Das könnte tatsächlich signifikant für diese Cache Diskussion sein.

[automerge]1602091756[/automerge]

Aus pal:

Da ist allerdings – soweit ich sehen kann – keinerlei Unterscheidung zwischen RDNA1/2 drin. Kann aber auch sein, dass das erst noch kommt.

[automerge]1602101574[/automerge]

btw, es wurden heute noch Patches für Dimgrey Cavefish (Navi 23) gepostet. Sind aber gänzlich langweilig, das Teil ist bislang bzgl. Code weitgehend gleich zu Navy Flounder.

Ja, dann haben sie die GL2A tatsächlich um einen Faktor 2 reduziert. Das könnte tatsächlich signifikant für diese Cache Diskussion sein.

[automerge]1602091756[/automerge]

Aus pal:

Code:

//

// The GL1 arbiter. The GL1 complex is per-SA by definition.

PerfCounterBlockInfo*const pGl1a = &pInfo->block[static_cast<uint32>(GpuBlock::Gl1a)];

pGl1a->distribution = PerfCounterDistribution::PerShaderArray;

pGl1a->numInstances = 1;

pGl1a->numGenericSpmModules = 1; // GL1A_PERFCOUNTER0

pGl1a->numGenericLegacyModules = 3; // GL1A_PERFCOUNTER1-3

pGl1a->numSpmWires = 2;

pGl1a->spmBlockSelect = Gfx10SpmSeBlockSelectGl1a;

pGl1a->maxEventId = maxIds[Gl1aPerfSelId];

pGl1a->regAddr = { 0, {

{ mmGL1A_PERFCOUNTER0_SELECT, mmGL1A_PERFCOUNTER0_SELECT1, mmGL1A_PERFCOUNTER0_LO, mmGL1A_PERFCOUNTER0_HI },

{ mmGL1A_PERFCOUNTER1_SELECT, 0, mmGL1A_PERFCOUNTER1_LO, mmGL1A_PERFCOUNTER1_HI },

{ mmGL1A_PERFCOUNTER2_SELECT, 0, mmGL1A_PERFCOUNTER2_LO, mmGL1A_PERFCOUNTER2_HI },

{ mmGL1A_PERFCOUNTER3_SELECT, 0, mmGL1A_PERFCOUNTER3_LO, mmGL1A_PERFCOUNTER3_HI },

}};

// The GL1 cache.

PerfCounterBlockInfo*const pGl1c = &pInfo->block[static_cast<uint32>(GpuBlock::Gl1c)];

pGl1c->distribution = PerfCounterDistribution::PerShaderArray;

pGl1c->numInstances = 4; // Each GL1A talks to four GL1C quadrants.

pGl1c->numGenericSpmModules = 1; // GL1C_PERFCOUNTER0

pGl1c->numGenericLegacyModules = 3; // GL1C_PERFCOUNTER1-3

pGl1c->numSpmWires = 2;

pGl1c->spmBlockSelect = Gfx10SpmSeBlockSelectGl1c;

pGl1c->maxEventId = maxIds[Gl1cPerfSelId];

pGl1c->regAddr = { 0, {

{ mmGL1C_PERFCOUNTER0_SELECT, mmGL1C_PERFCOUNTER0_SELECT1, mmGL1C_PERFCOUNTER0_LO, mmGL1C_PERFCOUNTER0_HI },

{ mmGL1C_PERFCOUNTER1_SELECT, 0, mmGL1C_PERFCOUNTER1_LO, mmGL1C_PERFCOUNTER1_HI },

{ mmGL1C_PERFCOUNTER2_SELECT, 0, mmGL1C_PERFCOUNTER2_LO, mmGL1C_PERFCOUNTER2_HI },

{ mmGL1C_PERFCOUNTER3_SELECT, 0, mmGL1C_PERFCOUNTER3_LO, mmGL1C_PERFCOUNTER3_HI },

}};

// The GL2A (gl2 arbiter) block is typically broken down into four quadrants - we treat them as four instances.

PerfCounterBlockInfo*const pGl2a = &pInfo->block[static_cast<uint32>(GpuBlock::Gl2a)];

pGl2a->distribution = PerfCounterDistribution::GlobalBlock;

pGl2a->numInstances = pProps->gfx9.gfx10.numGl2a;

pGl2a->numGenericSpmModules = 2; // Gl2A_PERFCOUNTER0-1

pGl2a->numGenericLegacyModules = 2; // Gl2A_PERFCOUNTER2-3

pGl2a->numSpmWires = 4;

pGl2a->spmBlockSelect = Gfx10SpmGlobalBlockSelectGl2a;

pGl2a->maxEventId = maxIds[Gl2aPerfSelId];

pGl2a->regAddr = { 0, {

{ mmGL2A_PERFCOUNTER0_SELECT, mmGL2A_PERFCOUNTER0_SELECT1, mmGL2A_PERFCOUNTER0_LO, mmGL2A_PERFCOUNTER0_HI },

{ mmGL2A_PERFCOUNTER1_SELECT, mmGL2A_PERFCOUNTER1_SELECT1, mmGL2A_PERFCOUNTER1_LO, mmGL2A_PERFCOUNTER1_HI },

{ mmGL2A_PERFCOUNTER2_SELECT, 0, mmGL2A_PERFCOUNTER2_LO, mmGL2A_PERFCOUNTER2_HI },

{ mmGL2A_PERFCOUNTER3_SELECT, 0, mmGL2A_PERFCOUNTER3_LO, mmGL2A_PERFCOUNTER3_HI },

}};

PerfCounterBlockInfo*const pGl2c = &pInfo->block[static_cast<uint32>(GpuBlock::Gl2c)];

pGl2c->distribution = PerfCounterDistribution::GlobalBlock;

pGl2c->numInstances = pProps->gfx9.gfx10.numGl2c; // This should be equal to the number of EAs.

pGl2c->numGenericSpmModules = 2; // Gl2C_PERFCOUNTER0-1

pGl2c->numGenericLegacyModules = 2; // Gl2C_PERFCOUNTER2-3

pGl2c->numSpmWires = 4;

pGl2c->spmBlockSelect = Gfx10SpmGlobalBlockSelectGl2c;

pGl2c->maxEventId = maxIds[Gl2cPerfSelId];

pGl2c->regAddr = { 0, {

{ mmGL2C_PERFCOUNTER0_SELECT, mmGL2C_PERFCOUNTER0_SELECT1, mmGL2C_PERFCOUNTER0_LO, mmGL2C_PERFCOUNTER0_HI },

{ mmGL2C_PERFCOUNTER1_SELECT, mmGL2C_PERFCOUNTER1_SELECT1, mmGL2C_PERFCOUNTER1_LO, mmGL2C_PERFCOUNTER1_HI },

{ mmGL2C_PERFCOUNTER2_SELECT, 0, mmGL2C_PERFCOUNTER2_LO, mmGL2C_PERFCOUNTER2_HI },

{ mmGL2C_PERFCOUNTER3_SELECT, 0, mmGL2C_PERFCOUNTER3_LO, mmGL2C_PERFCOUNTER3_HI },

}};

// The center hub arbiter (CHA). It's the global version of the GL1A and is used by global blocks.

PerfCounterBlockInfo*const pCha = &pInfo->block[static_cast<uint32>(GpuBlock::Cha)];

pCha->distribution = PerfCounterDistribution::GlobalBlock;

pCha->numInstances = 1;

pCha->numGenericSpmModules = 1; // CHA_PERFCOUNTER0

pCha->numGenericLegacyModules = 3; // CHA_PERFCOUNTER1-3

pCha->numSpmWires = 2;

pCha->spmBlockSelect = Gfx10SpmGlobalBlockSelectCha;

pCha->maxEventId = maxIds[ChaPerfSelId];

pCha->regAddr = { 0, {

{ mmCHA_PERFCOUNTER0_SELECT, mmCHA_PERFCOUNTER0_SELECT1, mmCHA_PERFCOUNTER0_LO, mmCHA_PERFCOUNTER0_HI },

{ mmCHA_PERFCOUNTER1_SELECT, 0, mmCHA_PERFCOUNTER1_LO, mmCHA_PERFCOUNTER1_HI },

{ mmCHA_PERFCOUNTER2_SELECT, 0, mmCHA_PERFCOUNTER2_LO, mmCHA_PERFCOUNTER2_HI },

{ mmCHA_PERFCOUNTER3_SELECT, 0, mmCHA_PERFCOUNTER3_LO, mmCHA_PERFCOUNTER3_HI },

}};

// The center hub buffer (CHC). It's the global version of the GL1C and is used by global blocks.

PerfCounterBlockInfo*const pChc = &pInfo->block[static_cast<uint32>(GpuBlock::Chc)];

pChc->distribution = PerfCounterDistribution::GlobalBlock;

pChc->numInstances = 4; // It also has four quadrants like the GL1C.

pChc->numGenericSpmModules = 1; // CHC_PERFCOUNTER0

pChc->numGenericLegacyModules = 3; // CHC_PERFCOUNTER1-3

pChc->numSpmWires = 2;

pChc->spmBlockSelect = Gfx10SpmGlobalBlockSelectChc;

pChc->maxEventId = maxIds[ChcPerfSelId];

pChc->regAddr = { 0, {

{ mmCHC_PERFCOUNTER0_SELECT, mmCHC_PERFCOUNTER0_SELECT1, mmCHC_PERFCOUNTER0_LO, mmCHC_PERFCOUNTER0_HI },

{ mmCHC_PERFCOUNTER1_SELECT, 0, mmCHC_PERFCOUNTER1_LO, mmCHC_PERFCOUNTER1_HI },

{ mmCHC_PERFCOUNTER2_SELECT, 0, mmCHC_PERFCOUNTER2_LO, mmCHC_PERFCOUNTER2_HI },

{ mmCHC_PERFCOUNTER3_SELECT, 0, mmCHC_PERFCOUNTER3_LO, mmCHC_PERFCOUNTER3_HI },

}};Da ist allerdings – soweit ich sehen kann – keinerlei Unterscheidung zwischen RDNA1/2 drin. Kann aber auch sein, dass das erst noch kommt.

[automerge]1602101574[/automerge]

btw, es wurden heute noch Patches für Dimgrey Cavefish (Navi 23) gepostet. Sind aber gänzlich langweilig, das Teil ist bislang bzgl. Code weitgehend gleich zu Navy Flounder.

Zuletzt bearbeitet:

BavarianRealist

Grand Admiral Special

★ Themenstarter ★

- Mitglied seit

- 06.02.2010

- Beiträge

- 3.385

- Renomée

- 85

Angeblich soll es noch eine Navi21-XTX-Version geben....

So oder so glaube ich langsam, dass Navi21 womöglich mehr als 80 CU hat, wenn Navi21 536mm² groß sein soll und ich das Ding mit Navi10 (251mm²) mit 40CU vergleiche: damit wäre Navi21 mehr als doppelt so groß, obwohl der Flächenintensive Speicherkanal mit 256 bit nicht größer ausfallen sollte. Der angebliche, große "Infinity Cache" wird sicher etwas Diesize verbrauchen, aber gleichzeitig spart man ja Fläche, weil man bei 256bit bleibt.

Soll zudem Navi21 den N7+ Prozess nutzen, der rund 15% Diesize einsparen soll, dann entspräche die Navi21-Diesize etwa 600-630mm² an N7-Diesize...

...80 CU war womöglich das Ziel für mindestens nutzbare CU, sodass man womöglich etwas mehr drin hat, sowie bei den neuen Konsolen-SoCs. Das Gleiche könnte für Navi22 zutreffen, also dann 48CU?

Vielleicht gibt es heute Abend noch einen kleinen Hinweis auf die kommenden GPUs, z.B. es am Schluss eine Aussage über die Präsentation vom 28.10. geben und die könnte z.B. etwa so lauten: "für den 28.10.2020 haben wir eine noch größere Freude für die Gamer..."

So oder so glaube ich langsam, dass Navi21 womöglich mehr als 80 CU hat, wenn Navi21 536mm² groß sein soll und ich das Ding mit Navi10 (251mm²) mit 40CU vergleiche: damit wäre Navi21 mehr als doppelt so groß, obwohl der Flächenintensive Speicherkanal mit 256 bit nicht größer ausfallen sollte. Der angebliche, große "Infinity Cache" wird sicher etwas Diesize verbrauchen, aber gleichzeitig spart man ja Fläche, weil man bei 256bit bleibt.

Soll zudem Navi21 den N7+ Prozess nutzen, der rund 15% Diesize einsparen soll, dann entspräche die Navi21-Diesize etwa 600-630mm² an N7-Diesize...

...80 CU war womöglich das Ziel für mindestens nutzbare CU, sodass man womöglich etwas mehr drin hat, sowie bei den neuen Konsolen-SoCs. Das Gleiche könnte für Navi22 zutreffen, also dann 48CU?

Vielleicht gibt es heute Abend noch einen kleinen Hinweis auf die kommenden GPUs, z.B. es am Schluss eine Aussage über die Präsentation vom 28.10. geben und die könnte z.B. etwa so lauten: "für den 28.10.2020 haben wir eine noch größere Freude für die Gamer..."

- Mitglied seit

- 16.10.2000

- Beiträge

- 24.486

- Renomée

- 9.834

- Standort

- East Fishkill, Minga, Xanten

- Aktuelle Projekte

- Je nach Gusto

- Meine Systeme

- Ryzen 9 5900X, Ryzen 7 3700X

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Samsung P35 (16 Jahre alt ;) )

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5900X

- Mainboard

- ASRock B550

- Speicher

- 2x 16 GB DDR4 3200

- Grafikprozessor

- GeForce GTX 1650

- Display

- 27 Zoll Acer + 24 Zoll DELL

- SSD

- Samsung 980 Pro 256 GB

- HDD

- diverse

- Soundkarte

- Onboard

- Gehäuse

- Fractal Design R5

- Netzteil

- be quiet! Straight Power 10 CM 500W

- Tastatur

- Logitech Cordless Desktop

- Maus

- Logitech G502

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox, Vivaldi

- Internetanbindung

- ▼250 MBit ▲40 MBit

Nein, die 80CU sind safe.

Ja, wenn dann sind die Non-XTX cut down. Aber ob das wirklich stimmt.

BavarianRealist

Grand Admiral Special

★ Themenstarter ★

- Mitglied seit

- 06.02.2010

- Beiträge

- 3.385

- Renomée

- 85

Nein, die 80CU sind safe.

Und wieso sollen die "safe" sein?

Berniyh

Grand Admiral Special

- Mitglied seit

- 29.11.2005

- Beiträge

- 5.240

- Renomée

- 232

Weil's in mehreren Treibern genau so steht.Nein, die 80CU sind safe.

Und wieso sollen die "safe" sein?

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 5.050

- Renomée

- 496

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Samsung, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

- Mitglied seit

- 16.10.2000

- Beiträge

- 24.486

- Renomée

- 9.834

- Standort

- East Fishkill, Minga, Xanten

- Aktuelle Projekte

- Je nach Gusto

- Meine Systeme

- Ryzen 9 5900X, Ryzen 7 3700X

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Samsung P35 (16 Jahre alt ;) )

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5900X

- Mainboard

- ASRock B550

- Speicher

- 2x 16 GB DDR4 3200

- Grafikprozessor

- GeForce GTX 1650

- Display

- 27 Zoll Acer + 24 Zoll DELL

- SSD

- Samsung 980 Pro 256 GB

- HDD

- diverse

- Soundkarte

- Onboard

- Gehäuse

- Fractal Design R5

- Netzteil

- be quiet! Straight Power 10 CM 500W

- Tastatur

- Logitech Cordless Desktop

- Maus

- Logitech G502

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox, Vivaldi

- Internetanbindung

- ▼250 MBit ▲40 MBit

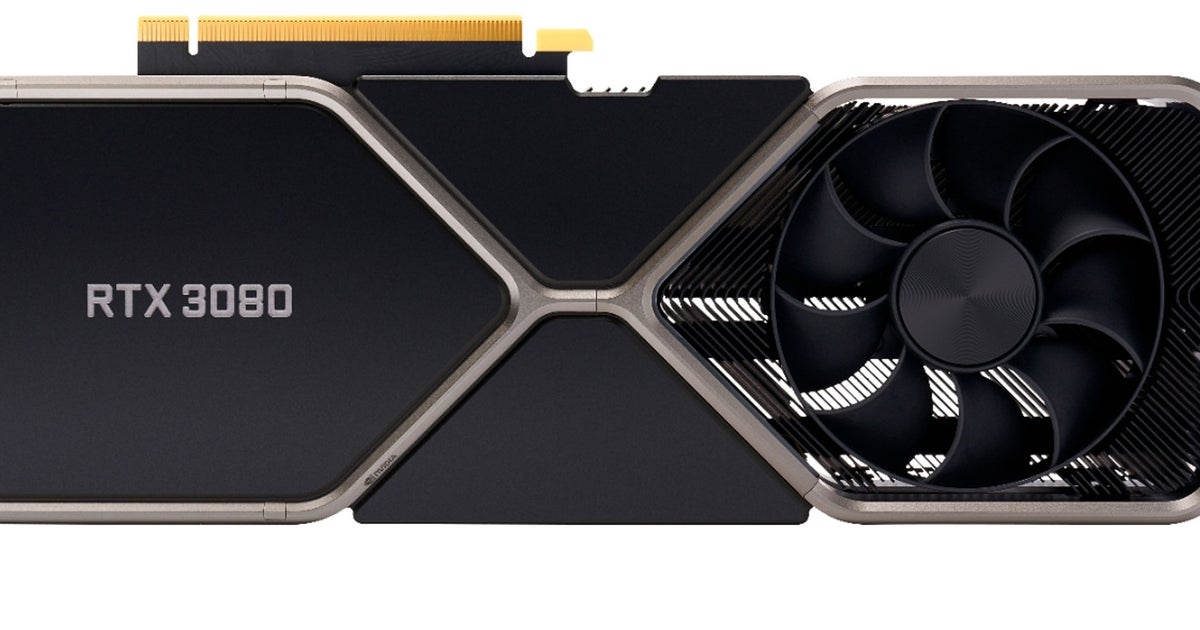

Nvidia GeForce RTX 3080 review: welcome to the next level

Digital Foundry's review of the RTX 3080, the first Ampere graphics card and one that delivers incredible performance - with some limitations.

Atombossler

Admiral Special

- Mitglied seit

- 28.04.2013

- Beiträge

- 1.423

- Renomée

- 65

- Standort

- Andere Sphären

- Mein Laptop

- Thinkpad 8

- Details zu meinem Desktop

- Prozessor

- A8-7600@3.25Ghz

- Mainboard

- Asus A88X-PRO

- Kühlung

- NoFan CR80 EH

- Speicher

- 16Gb G-Skill Trident-X DDR3 2400

- Grafikprozessor

- APU

- Display

- Acer UHD 4K2K

- SSD

- Samsung 850 PRO

- HDD

- 2xSamsung 1TB HDD (2,5")

- Optisches Laufwerk

- Plexi BD-RW

- Soundkarte

- OnBoard Geraffel

- Gehäuse

- Define R2

- Netzteil

- BeQuiet

- Betriebssystem

- Win7x64-PRO

- Webbrowser

- Chrome

Wenigstens haben sie sich von dem roten Rand verabschiedet.

Da bekam ich so'n komisches Dejavu ...

Ich sag nur "Knight Rider" ...

Da bekam ich so'n komisches Dejavu ...

Ich sag nur "Knight Rider" ...

- Mitglied seit

- 16.10.2000

- Beiträge

- 24.486

- Renomée

- 9.834

- Standort

- East Fishkill, Minga, Xanten

- Aktuelle Projekte

- Je nach Gusto

- Meine Systeme

- Ryzen 9 5900X, Ryzen 7 3700X

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Samsung P35 (16 Jahre alt ;) )

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5900X

- Mainboard

- ASRock B550

- Speicher

- 2x 16 GB DDR4 3200

- Grafikprozessor

- GeForce GTX 1650

- Display

- 27 Zoll Acer + 24 Zoll DELL

- SSD

- Samsung 980 Pro 256 GB

- HDD

- diverse

- Soundkarte

- Onboard

- Gehäuse

- Fractal Design R5

- Netzteil

- be quiet! Straight Power 10 CM 500W

- Tastatur

- Logitech Cordless Desktop

- Maus

- Logitech G502

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox, Vivaldi

- Internetanbindung

- ▼250 MBit ▲40 MBit

E555user

Grand Admiral Special

- Mitglied seit

- 05.10.2015

- Beiträge

- 2.173

- Renomée

- 938

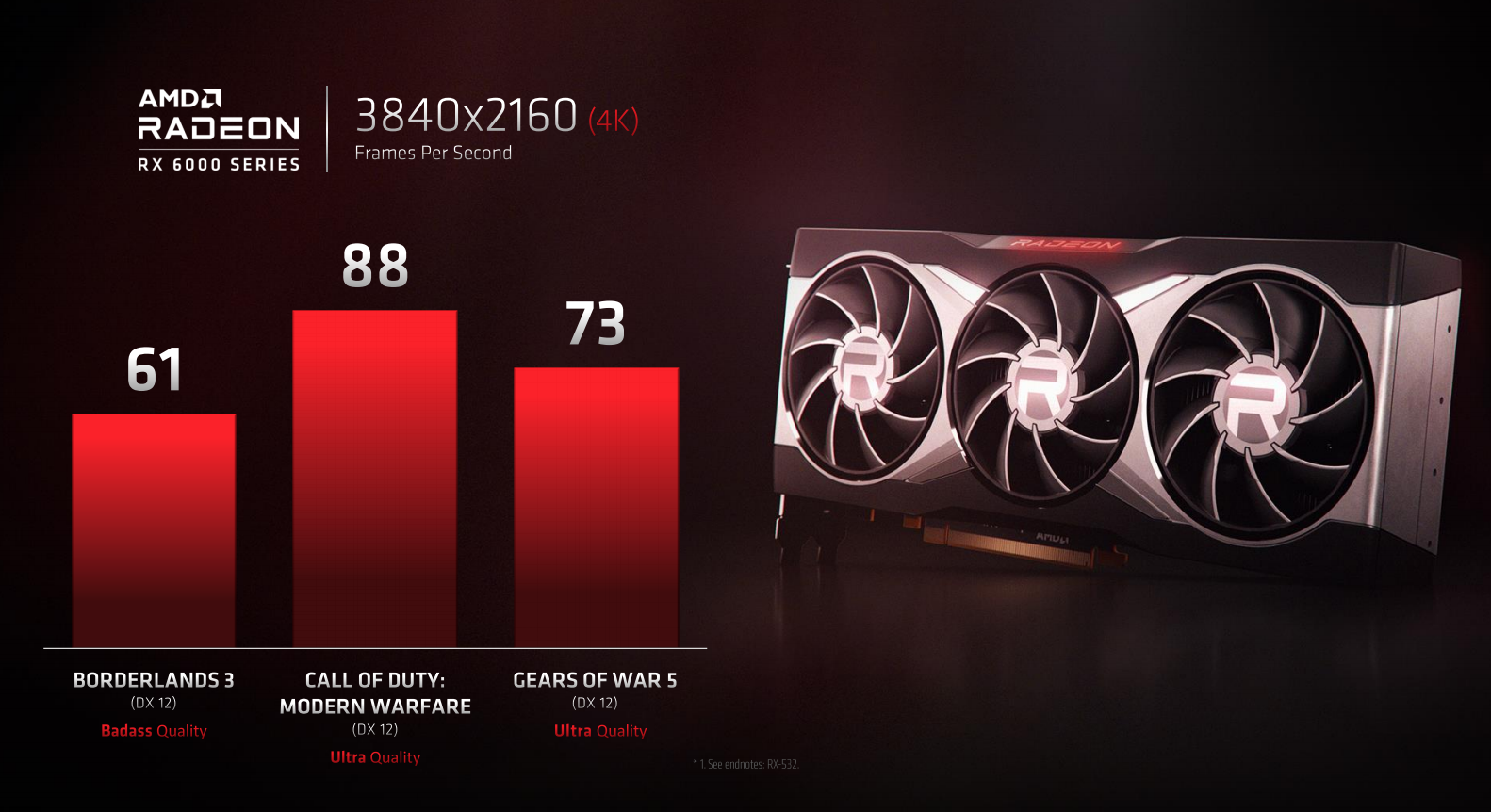

Man hat in der Präsentation mit Verweis auf die RX6000 Serie ohne klare Worte welche BigNavi gezeigt wurde noch alle Möglichkeiten für Korrekturen gelassen. Bei der CPU und dem Subsystem war der R9 5900X sicherlich ein Tick schneller als bei den Messungen der Nvidia Karten.

Es ist in meinen Augen eine Aussage gefallen, dass man dieses Niveau mindestens erreichen will, mehr ist aber eigentlich nicht passiert.

Es ist in meinen Augen eine Aussage gefallen, dass man dieses Niveau mindestens erreichen will, mehr ist aber eigentlich nicht passiert.

Highway61

Fleet Captain Special

In Borderlands z.Bsp. doppelt so schnell wie die 5700XT, ein riesiger Sprung von einer Generation zur nächsten. Dann bei der nächsten nochmals doppelt so schnell?

Also so wie es ausschaut, wirklich ganz nah bei der 3080 von der Konkurrenz, dafür 6 GB mehr Speicher. Mal schauen, wie der Preis angesetzt wird. Wenn die Konkurrenz noch eine 3080 mit 20GB herausbringen wird, dann wird die natürlich auch nochmals ein Stück mehr kosten als die mit 10GB. Energieverbrauch wird auch interessant, und wie weit man OC kann und ob die Boardpartner noch mehr Leistung herauskitzeln können. Spannend

Also so wie es ausschaut, wirklich ganz nah bei der 3080 von der Konkurrenz, dafür 6 GB mehr Speicher. Mal schauen, wie der Preis angesetzt wird. Wenn die Konkurrenz noch eine 3080 mit 20GB herausbringen wird, dann wird die natürlich auch nochmals ein Stück mehr kosten als die mit 10GB. Energieverbrauch wird auch interessant, und wie weit man OC kann und ob die Boardpartner noch mehr Leistung herauskitzeln können. Spannend

Sparky

Grand Admiral Special

- Mitglied seit

- 02.09.2004

- Beiträge

- 2.032

- Renomée

- 294

- Standort

- Wien

- Mein Laptop

- M1 Apple iPad Pro 12.9", 5.Gen (rendert brav meine Filmchen in Lumafusion)

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5950X

- Mainboard

- ASUS STRIX B550-F

- Kühlung

- Fractal Design C36

- Speicher

- 64 GB, G.Skill Trident Z Neo, 3600 MHz

- Grafikprozessor

- ASUS Prime Radeon RX 9070 XT OC

- Display

- LG UltraGear 38GN-950-B

- SSD

- ein paar...

- HDD

- einige...

- Optisches Laufwerk

- hatte ich mal...

- Soundkarte

- On board...

- Gehäuse

- Fractal Design Define R6

- Netzteil

- EVGA 850 W

- Betriebssystem

- Windows 10 Pro

- Webbrowser

- Firefox

- Internetanbindung

- ▼600 MBit ▲60 MBit

Man hat in der Präsentation mit Verweis auf die RX6000 Serie ohne klare Worte welche BigNavi gezeigt wurde noch alle Möglichkeiten für Korrekturen gelassen. Bei der CPU und dem Subsystem war der R9 5900X sicherlich ein Tick schneller als bei den Messungen der Nvidia Karten.

Sauerei sowas! Verwenden die doch glatt eine besonders schnelle in-house Eigenentwicklung einer CPU die kein Mensch hat und die die Werte der RX6000 künstlich nach oben treibt.

- Mitglied seit

- 16.10.2000

- Beiträge

- 24.486

- Renomée

- 9.834

- Standort

- East Fishkill, Minga, Xanten

- Aktuelle Projekte

- Je nach Gusto

- Meine Systeme

- Ryzen 9 5900X, Ryzen 7 3700X

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Samsung P35 (16 Jahre alt ;) )

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5900X

- Mainboard

- ASRock B550

- Speicher

- 2x 16 GB DDR4 3200

- Grafikprozessor

- GeForce GTX 1650

- Display

- 27 Zoll Acer + 24 Zoll DELL

- SSD

- Samsung 980 Pro 256 GB

- HDD

- diverse

- Soundkarte

- Onboard

- Gehäuse

- Fractal Design R5

- Netzteil

- be quiet! Straight Power 10 CM 500W

- Tastatur

- Logitech Cordless Desktop

- Maus

- Logitech G502

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox, Vivaldi

- Internetanbindung

- ▼250 MBit ▲40 MBit

Kleines Update.

Die Zahlen von Eurogamer waren teilweise etwas zu niedrig bzw. hoch.

Anhang anzeigen 41269

AMD zeigt 4K-Benchmarks einer Radeon RX 6000 - knapp unter bzw. fast im Bereich einer Nvidia GeForce RTX 3080 - Planet 3DNow!

Auf Planet 3DNow! gibt es alle wichtigen Informationen fr AMD-User: News, Downloads, Support, Tests

www.planet3dnow.de

Hier auch noch mal als Disclaimer, dass der Vergleich an vielen Stellen hinkt und nur grob die Richtung anzeigen soll.

Berniyh

Grand Admiral Special

- Mitglied seit

- 29.11.2005

- Beiträge

- 5.240

- Renomée

- 232

Borderlands ist schon interessant, denn bislang war die UE4 immer ziemlich problematisch mit AMD Karten. Mit Vega extrem krass, aber auch Navi 10 war hier im Vergleich zu Nvidia deutlich weiter zurück als in anderen Games.

Hier scheint RDNA2 deutlich verbessert.

Hier scheint RDNA2 deutlich verbessert.

E555user

Grand Admiral Special

- Mitglied seit

- 05.10.2015

- Beiträge

- 2.173

- Renomée

- 938

Berniyh

Grand Admiral Special

- Mitglied seit

- 29.11.2005

- Beiträge

- 5.240

- Renomée

- 232

@pipin: weißt du zufällig ob das hier die aktuelle Version der Tabelle ist bzw. hast nen Link zu einer neueren?

by https://twitter.com/KOMACHI_ENSAKA

by https://twitter.com/KOMACHI_ENSAKA

Zuletzt bearbeitet von einem Moderator:

- Mitglied seit

- 16.10.2000

- Beiträge

- 24.486

- Renomée

- 9.834

- Standort

- East Fishkill, Minga, Xanten

- Aktuelle Projekte

- Je nach Gusto

- Meine Systeme

- Ryzen 9 5900X, Ryzen 7 3700X

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Samsung P35 (16 Jahre alt ;) )

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5900X

- Mainboard

- ASRock B550

- Speicher

- 2x 16 GB DDR4 3200

- Grafikprozessor

- GeForce GTX 1650

- Display

- 27 Zoll Acer + 24 Zoll DELL

- SSD

- Samsung 980 Pro 256 GB

- HDD

- diverse

- Soundkarte

- Onboard

- Gehäuse

- Fractal Design R5

- Netzteil

- be quiet! Straight Power 10 CM 500W

- Tastatur

- Logitech Cordless Desktop

- Maus

- Logitech G502

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox, Vivaldi

- Internetanbindung

- ▼250 MBit ▲40 MBit

@pipin: weißt du zufällig ob das hier die aktuelle Version der Tabelle ist bzw. hast nen Link zu einer neueren?

Öh ich kenn auf jeden Fall keine neuere. Hat Komachi nicht auch irgendwo ne Webseite?

Ich kann ihn aber sonst mal fragen.

Ich hab oben auch mal seinen Twitter Account verlinkt. Urheberrecht und so.

Berniyh

Grand Admiral Special

- Mitglied seit

- 29.11.2005

- Beiträge

- 5.240

- Renomée

- 232

Danke, ich wollte eigentlich den Twitter Post als URL hinterlegen, aber hab wohl den falschen Link eingefügt, aber so geht es auch.

Du meinst diese Webseite hier?

Tatsächlich schreibt er hier:

komachizaregoto.blogspot.com

komachizaregoto.blogspot.com

Das wusste ich jetzt noch nicht.

Du meinst diese Webseite hier?

Tatsächlich schreibt er hier:

[#小町戯言シリーズ] AMD GFX-ID : Which generation is the chip?

Here is a partial list of GFX_IDs that I usually use. You should be able to clearly understand which chip is which generation. You can also ...

Code:

ASIC ID : GFX11 = RDNA3?

: GFX1100 = Reserved = NAVI31.Das wusste ich jetzt noch nicht.

- Mitglied seit

- 16.10.2000

- Beiträge

- 24.486

- Renomée

- 9.834

- Standort

- East Fishkill, Minga, Xanten

- Aktuelle Projekte

- Je nach Gusto

- Meine Systeme

- Ryzen 9 5900X, Ryzen 7 3700X

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Samsung P35 (16 Jahre alt ;) )

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5900X

- Mainboard

- ASRock B550

- Speicher

- 2x 16 GB DDR4 3200

- Grafikprozessor

- GeForce GTX 1650

- Display

- 27 Zoll Acer + 24 Zoll DELL

- SSD

- Samsung 980 Pro 256 GB

- HDD

- diverse

- Soundkarte

- Onboard

- Gehäuse

- Fractal Design R5

- Netzteil

- be quiet! Straight Power 10 CM 500W

- Tastatur

- Logitech Cordless Desktop

- Maus

- Logitech G502

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox, Vivaldi

- Internetanbindung

- ▼250 MBit ▲40 MBit

Danke, ich wollte eigentlich den Twitter Post als URL hinterlegen, aber hab wohl den falschen Link eingefügt, aber so geht es auch.

Du meinst diese Webseite hier?

Jepp, genau die Seite hab ich auch in den Bookmarks.

E555user

Grand Admiral Special

- Mitglied seit

- 05.10.2015

- Beiträge

- 2.173

- Renomée

- 938

Die Webseite von AMD bleibt zu RDNA2 noch an der Oberfläche.

Mit Bezug auf den Infinity Cache hat man folgendes geschrieben:

Für mich liest sich das wie ein LLC hinter dem gemeinsamen L2, der vergleichbar zu Zen als Victim Cache realisiert wurde. Die Speicherobjekte im gemeinsamen Zugriff fliegen nicht ganz runter vom Chip sondern werden transparent für alle Units auf der GPU vorgehalten. Eine Cache Verwaltung erkennt Speicherbereiche, die keine Hits generieren und lässt diese nicht den LLC trashen. Das könnte automatisch und optional via ISA gesteuert sein.

Es wird auch Smart Access Memory auf der Webseite erläutert. Es wird nicht nur in ein (256MB?) Fenster geschrieben und zugegriffen, dessen Inhalt auf der GPU wieder local/private weg kopiert wird. Das könnte etwa mit PCIe Resizable BAR Support zu tun haben weil eine 256MB Grenze aufgehoben werden soll. Allerdings ist das mit Windows theoretisch seit 2017 möglich, es verwundert daher wenn dazu erst heute ganz bestimmte Kombinationen von Chips notwendig sein sollen.

Bei den ausgelobten Preisen zur 6900XT erstaunt etwas, dass man für eine sonst identische GPU bei 11% mehr CUs dann doch über 50% mehr bezahlen soll, das ist wohl der überbordenden Preispolitik von Nvidia zu verdanken. Auch wenn es nicht in den Specs steht sollte wegen des besseren Binnings hoffentlich auch der Takt dauerhaft höher gehalten werden können als bei der 6800XT.

Mit Bezug auf den Infinity Cache hat man folgendes geschrieben:

Quote: 1664 GB/s EffectiveAMD Infinity Cache for Power Efficient Performance

AMD RDNA 2 Architecture is even more efficient than before with the introduction of AMD Infinity Cache, an all-new cache level that enables high bandwidth performance at low power and low latency. This global cache is seen by the entire graphics core, capturing temporal re-use and enabling data to be accessed instantaneously. Leveraging the best high frequency approaches from "Zen" architecture, AMD Infinity Cache enables scalable performance for the future.

Für mich liest sich das wie ein LLC hinter dem gemeinsamen L2, der vergleichbar zu Zen als Victim Cache realisiert wurde. Die Speicherobjekte im gemeinsamen Zugriff fliegen nicht ganz runter vom Chip sondern werden transparent für alle Units auf der GPU vorgehalten. Eine Cache Verwaltung erkennt Speicherbereiche, die keine Hits generieren und lässt diese nicht den LLC trashen. Das könnte automatisch und optional via ISA gesteuert sein.

Es wird auch Smart Access Memory auf der Webseite erläutert. Es wird nicht nur in ein (256MB?) Fenster geschrieben und zugegriffen, dessen Inhalt auf der GPU wieder local/private weg kopiert wird. Das könnte etwa mit PCIe Resizable BAR Support zu tun haben weil eine 256MB Grenze aufgehoben werden soll. Allerdings ist das mit Windows theoretisch seit 2017 möglich, es verwundert daher wenn dazu erst heute ganz bestimmte Kombinationen von Chips notwendig sein sollen.

Bei den ausgelobten Preisen zur 6900XT erstaunt etwas, dass man für eine sonst identische GPU bei 11% mehr CUs dann doch über 50% mehr bezahlen soll, das ist wohl der überbordenden Preispolitik von Nvidia zu verdanken. Auch wenn es nicht in den Specs steht sollte wegen des besseren Binnings hoffentlich auch der Takt dauerhaft höher gehalten werden können als bei der 6800XT.

Zuletzt bearbeitet:

BavarianRealist

Grand Admiral Special

★ Themenstarter ★

- Mitglied seit

- 06.02.2010

- Beiträge

- 3.385

- Renomée

- 85

Die 6800XT finde ich zu günstig im Preis: für lediglich 70$ mehr gibt es 72 statt 60 CU, also 20% mehr CUs und zudem nochmals 10% mehr Game-Takt dazu, also gut rund +33% mehr Leistung für lediglich 11% mehr Kosten...

Gleichzeitig wird spekuliert, dass Navi21 noch weit höher takten kann, rund 10% mehr. Ebenso hat AMD von +30% Takt gegenüber RDNA1 gesprochen, was dann wären 2280Mhz Game-Takt (statt nur 2015Mhz) bzw. 2475Mhz Boost (statt 2250Mhz), wenn ich die "Standard" 5700XT als Basis nehme.

Mit Ausreizen des wohl noch verfügbaren Takt-Spielraums hätte eine Custum-6800XT-OC dann etwa die Leistung einer 6900XT, die satte 999$ kosten soll. Zuletzt scheint Navi21 in der 6900XT kaum ausgereizt zu sein, wenn er dort die gleiche TDP wie die 6800XT hat...und eine vermutlich später kommende Custom-6900XT dürfte die 3090 ziemlich nass machen...

Meine Vermutung:

die heute ausgegebenen Preise für die non-Custum-Versionen von AMD sind künstlich niedrig und gleichzeitig hat man hier die GPUs noch nicht ganz ausgereizt, sodass noch viel Luft für die Custom-Versionen ist und die dann entsprechend teuerer werden können. Die heute vorgestellen non-Custom-Versionen wird man wohl schnell auslaufen lassen. Eine gute Custom-6800XT-OC dürfte wohl eher so in Richtung 800€ gehen.

Insbersondere die 6800 non-Custom von AMD ist meines Erachtens künstlich nierdrig getaktet, um sie uninteressant zu machen. Gerade die auf 60CU (also um jede 4. CU) gekappten GPUs sollten von der Wärme her die maximalen Takte (2,5Ghz?) noch eher erreichen...und wenn das dann auch 2,5Ghz statt nur 2,1Ghz sind, wäre hier noch 20% Plus für Custom-Versionen mit weit höherem Preis drin.

Gleichzeitig wird spekuliert, dass Navi21 noch weit höher takten kann, rund 10% mehr. Ebenso hat AMD von +30% Takt gegenüber RDNA1 gesprochen, was dann wären 2280Mhz Game-Takt (statt nur 2015Mhz) bzw. 2475Mhz Boost (statt 2250Mhz), wenn ich die "Standard" 5700XT als Basis nehme.

Mit Ausreizen des wohl noch verfügbaren Takt-Spielraums hätte eine Custum-6800XT-OC dann etwa die Leistung einer 6900XT, die satte 999$ kosten soll. Zuletzt scheint Navi21 in der 6900XT kaum ausgereizt zu sein, wenn er dort die gleiche TDP wie die 6800XT hat...und eine vermutlich später kommende Custom-6900XT dürfte die 3090 ziemlich nass machen...

Meine Vermutung:

die heute ausgegebenen Preise für die non-Custum-Versionen von AMD sind künstlich niedrig und gleichzeitig hat man hier die GPUs noch nicht ganz ausgereizt, sodass noch viel Luft für die Custom-Versionen ist und die dann entsprechend teuerer werden können. Die heute vorgestellen non-Custom-Versionen wird man wohl schnell auslaufen lassen. Eine gute Custom-6800XT-OC dürfte wohl eher so in Richtung 800€ gehen.

Insbersondere die 6800 non-Custom von AMD ist meines Erachtens künstlich nierdrig getaktet, um sie uninteressant zu machen. Gerade die auf 60CU (also um jede 4. CU) gekappten GPUs sollten von der Wärme her die maximalen Takte (2,5Ghz?) noch eher erreichen...und wenn das dann auch 2,5Ghz statt nur 2,1Ghz sind, wäre hier noch 20% Plus für Custom-Versionen mit weit höherem Preis drin.

Zuletzt bearbeitet:

Ähnliche Themen

- Antworten

- 2

- Aufrufe

- 225

- Antworten

- 0

- Aufrufe

- 31

- Antworten

- 0

- Aufrufe

- 36