App installieren

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: This feature may not be available in some browsers.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Kaveri - der Trinity Nachfolger

- Ersteller FredD

- Erstellt am

Andy06

Grand Admiral Special

- Mitglied seit

- 02.05.2006

- Beiträge

- 2.318

- Renomée

- 9

- Standort

- Berlin

- Mein Laptop

- Acer Aspire 1410

- Details zu meinem Desktop

- Prozessor

- AMD FX 8350

- Mainboard

- MSI 760GA-P43 (FX)

- Kühlung

- Alpenföhn Matterhorn 2x120er Lüfter

- Speicher

- 16 GB DDR3 @1894

- Grafikprozessor

- Gigabyte R9 280X Rev.2

- Display

- 27" iiyama ProLite E2773HDS

- SSD

- Samsung SSD 840 1TB

- Optisches Laufwerk

- Lite iHOS104 BluRay Laufwerk

- Soundkarte

- onBoard

- Netzteil

- 500 Watt OCZ ModXStream-Pro

- Betriebssystem

- Windows 7 HP 64bit

- Webbrowser

- Google Chrome

Ja ist mir schon klar. Aber warum darauf beziehen, wenn man ihn vor einer Verwechslung warnen muss? Da macht es vielleicht eher klick im Köpfchen.

derDruide

Grand Admiral Special

- Mitglied seit

- 09.08.2004

- Beiträge

- 2.724

- Renomée

- 433

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 3900X

- Mainboard

- Asus Strix B450-F Gaming

- Kühlung

- Noctua NH-C14

- Speicher

- 32 GB DDR4-3200 CL14 FlareX

- Grafikprozessor

- Radeon RX 590

- Display

- 31.5" Eizo FlexScan EV3285

- SSD

- Corsair MP510 2 TB, Samsung 970 Evo 512 GB

- HDD

- Seagate Ironwulf 6 TB

- Optisches Laufwerk

- Plextor PX-880SA

- Soundkarte

- Creative SoundblasterX AE-7

- Gehäuse

- Antec P280

- Netzteil

- be quiet! Straight Power E9 400W

- Maus

- Logitech Trackman Marble (Trackball)

- Betriebssystem

- openSUSE 15.2

- Webbrowser

- Firefox

- Internetanbindung

- ▼50 MBit ▲10 MBit

Ja ist mir schon klar. Aber warum darauf beziehen, wenn man ihn vor einer Verwechslung warnen muss? Da macht es vielleicht eher klick im Köpfchen.

Die Frage bezieht sich auf den rank und soll bitte nicht auf "dual sided" bezogen werden. Traurig, dass man das dazu schreiben muss, aber ist wohl so. Wer weiß wer da bei Corsair die Fragen beantwortet.

MMH

Lieutnant

- Mitglied seit

- 04.01.2014

- Beiträge

- 57

- Renomée

- 4

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen™ 7 PRO 5750GE

- Mainboard

- ASUS Pro WS X570-ACE

- Kühlung

- BeQuiet! ShadowRock LP

- Speicher

- G.Skill 32GB 3600 14-14-14-36-46 1T

- Grafikprozessor

- Sapphire RX 5500XT 8G

- Display

- Samsung CHG70

- SSD

- Viele

- HDD

- Viele

- Optisches Laufwerk

- Pioneer BDR-S12U

- Soundkarte

- ASUS STX-II 7.1

- Gehäuse

- Corsair 550D gedämmt

- Netzteil

- BeQuiet! Stright Power 11 450W

- Maus

- Roccat KoneXT

- Betriebssystem

- Win10 Pro 1709

Corsair bleibt dabei!Corsair: NO. Not in a by-8 configuration. In a by-8 configuration, it takes 8 RAMs to make a rank. In a by-8 configuration a module with 1 side of 8 RAMs is SS or SR. In a by-8 configuration a module with 16 RAMs is DS or DR. I am sorry but I am pressed for time. This information is freely available on the internet.

Heist es einfach das in einer by-8 Configuration die mit 8 Chips auf einer Seite generell SS bzw SR sind und die mit 16 automatisch generell DS bzw DR.

Ob das jetzt so ist oder nicht ist mir jetzt auch egal. Ich geh jetzt ins Bett sonst steigt mir mein brünetter RAM noch aufs Dach! Gute Nacht.

Zuletzt bearbeitet:

1) Der TLB-Bug wird gemeinhin als Problem der ersten Quadcore-Phenoms gesehen - nicht als typisches "Bulldozer-Problem".

2) Dir ist das Projekt Timna offenbar nicht bekannt (1999). Und überhaupt - Eine integrierte Grafik in einem CPU-Produkt ist keine "Erfindung" von Intel, oder AMD. Das gabs auch von anderen Chipentwicklerküchen.[...]

1) siehe unten

2) Nein, das "Projekt" Timna ist mir wirklich nicht bekannt gewesen (aber auch nicht verwunderlich wenn es nie das Licht der Welt erblickt hatte[...]). Mag sein, dass es das auch schon von anderen Chipentwicklern gegeben hat - Fakt ist, dass AMD das "als erster" durchsetzen wollte und sogar den Firmenslogan darauf getrimmt / geändert hat. Diesbzgl. sind wir also nicht einer Meinung.

--> wohlgemerkt: ich habe nie gesagt, dass es eine Erfindung von AMD gewesen wäre - wenn dem so sein sollte hätten sie vermutlich ein Patent darauf... haben sie aber nicht... das sagt doch schon alles, oder?

Wie Bobo schon sagte, der TLB-Bug hat nicht das geringste mit Bulldozer zu tun. Damals war das Problem längst beseitigt. Der TLB-Bug trat beim BA/B2 Barcelona auf, welcher der erste Quad-Core von AMD auf Basis der "Stars" Architektur war. Intel hatte übrigens bei Nehalem auch seinen TLB-Bug. Wurde dort nur nicht so breitgetreten.

Ich danke euch beiden für den Hinweis. Da hat sich in meinem Kopf was grundsätzlich Verschiedenes vermischt. Will heißen: Nein, es war absolut kein Bulldozer Problem (--> ich hab voll den Codenamen verwechselt, passiert leider häufig wenn die finalen Produkte draußen sind - ich entschuldige mich dafür).

Dennoch lese ich aus Bobo's Aussage (--> "nicht als typisches Bulldozer-Problem") nicht explizit heraus, dass es absolut nichts mit Bulldozer zu tun hatte - danke für die klarere Ausdrucksweise. Als ich (wieder) realisiert habe, dass die Bulldozer (nur) die FX-CPUs sind, war mir sofort klar, dass ich absoluten Mist geredet habe.

Zuletzt bearbeitet:

BoMbY

Grand Admiral Special

- Mitglied seit

- 22.11.2001

- Beiträge

- 7.468

- Renomée

- 293

- Standort

- Aachen

- Details zu meinem Desktop

- Prozessor

- Ryzen 3700X

- Mainboard

- Gigabyte X570 Aorus Elite

- Kühlung

- Noctua NH-U12A

- Speicher

- 2x16 GB, G.Skill F4-3200C14D-32GVK @ 3600 16-16-16-32-48-1T

- Grafikprozessor

- RX 5700 XTX

- Display

- Samsung CHG70, 32", 2560x1440@144Hz, FreeSync2

- SSD

- AORUS NVMe Gen4 SSD 2TB, Samsung 960 EVO 1TB, Samsung 840 EVO 1TB, Samsung 850 EVO 512GB

- Optisches Laufwerk

- Sony BD-5300S-0B (eSATA)

- Gehäuse

- Phanteks Evolv ATX

- Netzteil

- Enermax Platimax D.F. 750W

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox

Corsair bleibt dabei!

Heist es einfach das in einer by-8 Configuration die mit 8 Chips auf einer Seite generell SS bzw SR sind und die mit 16 automatisch generell DS bzw DR.

Ob das jetzt so ist oder nicht ist mir jetzt auch egal. Ich geh jetzt ins Bett sonst steigt mir mein brünetter RAM noch aufs Dach! Gute Nacht.

Wenn ein Chip ein 8 Bit Interface hat, dann hast Du pro Rank 8 Chips. Wenn der Chip ein 4 Bit Interface hat, dann 16 pro Rank, und bei 16 Bit halt entsprechend 4 pro Rank ... Scheinbar sind die meisten RAM-Chips heutzutage welche mit 8-Bit Interface.

Opteron

Redaktion

☆☆☆☆☆☆

Wenn ein Chip ein 8 Bit Interface hat, dann hast Du pro Rank 8 Chips. Wenn der Chip ein 4 Bit Interface hat, dann 16 pro Rank, und bei 16 Bit halt entsprechend 4 pro Rank ... Scheinbar sind die meisten RAM-Chips heutzutage welche mit 8-Bit Interface.

Nö da gibts verschiedene ... deswegen finde ich die Supportaussage schon etwas gewöhnungsbedürftig.

Ja mit "by 8" = x8 hat er recht .. aber es gibt viele DRAMs. Einigermaßen Sinn würde die Supporteraussage nur machen, wenn Corsair generell nur x8-Chips verbaut.

nVoodoo

Vice Admiral Special

- Mitglied seit

- 16.03.2007

- Beiträge

- 531

- Renomée

- 1

- Standort

- Nördliches Emsland

- Meine Systeme

- R7 1700;2xX5650;i7 4700MQ;2x E5430;Athlon 5350

- BOINC-Statistiken

Bei Kingston ist das ganze relativ gut Dokumentiert und alles per Homepage zu bekommen bei den HyperX hier im PC z.B. (1Rx8 memory modules, based on eight 512M x 8-bit DDR3 FBGA components per module.) Bei G.Skill wiederrum ist da garnix auf der Homepage zu finden...

MMH

Lieutnant

- Mitglied seit

- 04.01.2014

- Beiträge

- 57

- Renomée

- 4

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen™ 7 PRO 5750GE

- Mainboard

- ASUS Pro WS X570-ACE

- Kühlung

- BeQuiet! ShadowRock LP

- Speicher

- G.Skill 32GB 3600 14-14-14-36-46 1T

- Grafikprozessor

- Sapphire RX 5500XT 8G

- Display

- Samsung CHG70

- SSD

- Viele

- HDD

- Viele

- Optisches Laufwerk

- Pioneer BDR-S12U

- Soundkarte

- ASUS STX-II 7.1

- Gehäuse

- Corsair 550D gedämmt

- Netzteil

- BeQuiet! Stright Power 11 450W

- Maus

- Roccat KoneXT

- Betriebssystem

- Win10 Pro 1709

Wenn ein Chip ein 8 Bit Interface hat, dann hast Du pro Rank 8 Chips. Wenn der Chip ein 4 Bit Interface hat, dann 16 pro Rank, und bei 16 Bit halt entsprechend 4 pro Rank ... Scheinbar sind die meisten RAM-Chips heutzutage welche mit 8-Bit Interface.

Ja mit "by 8" = x8 hat er recht .. aber es gibt viele DRAMs. Einigermaßen Sinn würde die Supporteraussage nur machen, wenn Corsair generell nur x8-Chips verbaut.

Ich denke auch, dass Corsair damit sagen wollte, dass sie nur die by-8 Konfiguration bauen und SS dann auch automatisch SR sind. Er hat aber auch geschrieben, dass es innerhalb der gleichen Frequenzbereichs z.B. 1866er SS und DS gibt und man nur 100% sicher sein kann, wenn man die Möglichkeit hat sich den Speicher vor dem Kauf anzusehen.

Meine Dominator Platinum sind alle DS also auch DR! Mein 1866er Corsair vengeance ist SS also sprich nur SR. Und damit hat man doch schon für Corsair-Module eine feste Aussage! Denn Hinweise in der Seriennummer wollte Corsair oder kann Corsair nicht bestätigen und so bleibt bloß nachschaun. Deswegen auch keine Festlegung in den Datenblättern.

nazgul99

Grand Admiral Special

- Mitglied seit

- 01.05.2005

- Beiträge

- 3.592

- Renomée

- 224

- Standort

- Irgendwo in der Nähe

- Mein Laptop

- ThinkPad Edge E145 / 8GB / M500 480GB / Kubuntu /// Asus U38N / 6GB / Matt / Postville / Kubuntu/W8

- Details zu meinem Desktop

- Prozessor

- AMD A10-7800

- Mainboard

- MSI A88XI AC

- Kühlung

- Scythe Shuriken Rev.2

- Speicher

- 2x 8GB DDR3-2133

- Grafikprozessor

- IGP

- Display

- HP LP2465, MVA, 1920x1200, 24"

- SSD

- Samsung 850 EVO 500GB

- HDD

- ST9500325AS 500GB

- Optisches Laufwerk

- ja, so'n USB-Dings

- Soundkarte

- onboard, optisch -> SMSL Q5 PRO -> ELAC EL60

- Gehäuse

- Silverstone ML06B

- Netzteil

- SST-ST30SF

- Betriebssystem

- Kubuntu

- Webbrowser

- Firefox

- Verschiedenes

- Synology DS414slim 3x 1,5 TB RAID5

Phoronix: AMD Kaveri OpenCL Compared To Radeon & GeForce GPUs On Linux

Sehr unterschiedliche Ergebnisse: Beim ersten Test ("Parboil v2.5 OpenCL Histo") ist Kaveri kaum besser als eine Radeon HD 6450 und beleibt weit hinter einer GeForce GT 240 zurück, schon im zweiten Test ("Parboil v2.5 OpenCL TPACF") besiegt Kaveri eine Radeon HD 6870 mit doppelter Performance und liegt zwischen GeForce GTX 770 und GTX 760. Was auch immer "Parboil" für Zeugs ist

Sehr unterschiedliche Ergebnisse: Beim ersten Test ("Parboil v2.5 OpenCL Histo") ist Kaveri kaum besser als eine Radeon HD 6450 und beleibt weit hinter einer GeForce GT 240 zurück, schon im zweiten Test ("Parboil v2.5 OpenCL TPACF") besiegt Kaveri eine Radeon HD 6870 mit doppelter Performance und liegt zwischen GeForce GTX 770 und GTX 760. Was auch immer "Parboil" für Zeugs ist

bbott

Grand Admiral Special

- Mitglied seit

- 11.11.2001

- Beiträge

- 4.363

- Renomée

- 60

- Mein Laptop

- HP Compaq 8510p

- Details zu meinem Desktop

- Prozessor

- AMD FX-8370

- Mainboard

- Asus M5A99X

- Kühlung

- Corsair H60

- Speicher

- 16GB DDR3-1866 Crucial

- Grafikprozessor

- Sapphire HD5770

- Display

- 4k 27" DELL

- SSD

- Samsung Evo 850

- HDD

- 2x Seagate 7200.12

- Optisches Laufwerk

- Pioneer, Plextor

- Soundkarte

- Creative X-Fi Xtreme Music

- Gehäuse

- Silverstone TJ-02S

- Netzteil

- Enermax 450W

- Betriebssystem

- Windows 7

Meine 1866er Corsair Vengeance (4GB - CMZ8GX3M2A1866C9) haben DR (Ranks = 2) laut HWinfo64.

Pirx

Admiral Special

- Mitglied seit

- 11.11.2001

- Beiträge

- 1.234

- Renomée

- 11

- Standort

- Mädels auf Bäumen wachsen

- Mein Laptop

- Samsung NC20

- Details zu meinem Desktop

Wenn ein Chip ein 8 Bit Interface hat, dann hast Du pro Rank 8 Chips. Wenn der Chip ein 4 Bit Interface hat, dann 16 pro Rank, und bei 16 Bit halt entsprechend 4 pro Rank ... Scheinbar sind die meisten RAM-Chips heutzutage welche mit 8-Bit Interface.

Dann wären die Teamgroup Vulcan 4 GB - Riegel - lt. Webseite 256x8/512x8 also auf jeden Fall mal 8 - single rank (sind single sided).

Frage mich bloss, wie die mit 8 Chips und 256/512x8 auf 4 oder 8 GB kommen wollen. edit: durch beidseitige Bestückung

http://www.teamgroup.com.tw/filterable_product/tabs_detail/data/en/9/643/zfKsFi.html

also sind die 8 GB Teamgroup Vulcan dual rank

Zuletzt bearbeitet:

gruffi

Grand Admiral Special

- Mitglied seit

- 08.03.2008

- Beiträge

- 5.393

- Renomée

- 65

- Standort

- vorhanden

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 5 1600

- Mainboard

- MSI B350M PRO-VDH

- Kühlung

- Wraith Spire

- Speicher

- 2x 8 GB DDR4-2400 CL16

- Grafikprozessor

- XFX Radeon R7 260X

- Display

- LG W2361

- SSD

- Crucial CT250BX100SSD1

- HDD

- Toshiba DT01ACA200

- Optisches Laufwerk

- LG Blu-Ray-Brenner BH16NS40

- Soundkarte

- Realtek HD Audio

- Gehäuse

- Sharkoon MA-I1000

- Netzteil

- be quiet! Pure Power 9 350W

- Betriebssystem

- Windows 10 Professional 64-bit

- Webbrowser

- Mozilla Firefox

- Verschiedenes

- https://valid.x86.fr/mb4f0j

Naja, ob man die Sachen wirklich ernst nehmen kann, darf bezweifelt werden. In dem ersten Parboil Test liegt selbst eine R9 290 noch leicht hinter der HD 6450. Ist natürlich Quatsch. Da würde ich eher mal auf Treiberprobleme tippen.Phoronix: AMD Kaveri OpenCL Compared To Radeon & GeForce GPUs On Linux

Sehr unterschiedliche Ergebnisse: Beim ersten Test ("Parboil v2.5 OpenCL Histo") ist Kaveri kaum besser als eine Radeon HD 6450 und beleibt weit hinter einer GeForce GT 240 zurück, schon im zweiten Test ("Parboil v2.5 OpenCL TPACF") besiegt Kaveri eine Radeon HD 6870 mit doppelter Performance und liegt zwischen GeForce GTX 770 und GTX 760. Was auch immer "Parboil" für Zeugs ist

Kaveri

Cadet

Nur zur Info: Bei Computerbase im Forum entsteht zurzeit ein Sammler für DualRank Ram.

Bisher ist Kingston soweit komplett dokumentiert.

mfg

Bisher ist Kingston soweit komplett dokumentiert.

mfg

Meine 1866er Corsair Vengeance (4GB - CMZ8GX3M2A1866C9) haben DR (Ranks = 2) laut HWinfo64.

Gut, dann gilt das für meine CMZ8GX3M2A1866C9 auch!

Danke für's Nachschauen.

Danke für's Nachschauen.SPINA

Grand Admiral Special

- Mitglied seit

- 07.12.2003

- Beiträge

- 18.122

- Renomée

- 985

- Mein Laptop

- Lenovo IdeaPad Gaming 3 (15ARH05-82EY003NGE)

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- ASUS PRIME X370-PRO

- Kühlung

- AMD Wraith Prism

- Speicher

- 2x Micron 32GB PC4-25600E (MTA18ASF4G72AZ-3G2R)

- Grafikprozessor

- Sapphire Pulse Radeon RX 7600 8GB

- Display

- LG Electronics 27UD58P-B

- SSD

- Samsung 980 PRO (MZ-V8P1T0CW)

- HDD

- 2x Samsung 870 QVO (MZ-77Q2T0BW)

- Optisches Laufwerk

- HL Data Storage BH16NS55

- Gehäuse

- Lian Li PC-7NB

- Netzteil

- Seasonic PRIME Gold 650W

- Betriebssystem

- Debian 12.x (x86-64)

- Verschiedenes

- ASUS TPM-M R2.0

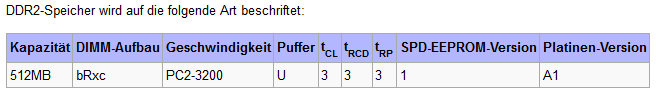

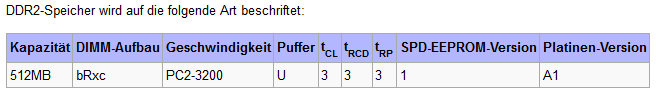

Dabei gibt es an für sich klare Vorschriften für das Beschriften von Speichermodulen:

Bildquelle: Wikipedia

Die meisten meiner Speichermodule halten sich auch mehr oder weniger an diese Vorschrift.

Manche sogar exakt. Zum Beispiel dieses DIMM von Hewlett-Packard/Micron:

"1RX8" bedeutet dabei 1 Rank, x8 Chips. So kann man sie leicht von dual-ranked und quad-ranked unterscheiden.

Bildquelle: Wikipedia

Die meisten meiner Speichermodule halten sich auch mehr oder weniger an diese Vorschrift.

Manche sogar exakt. Zum Beispiel dieses DIMM von Hewlett-Packard/Micron:

"1RX8" bedeutet dabei 1 Rank, x8 Chips. So kann man sie leicht von dual-ranked und quad-ranked unterscheiden.

bbott

Grand Admiral Special

- Mitglied seit

- 11.11.2001

- Beiträge

- 4.363

- Renomée

- 60

- Mein Laptop

- HP Compaq 8510p

- Details zu meinem Desktop

- Prozessor

- AMD FX-8370

- Mainboard

- Asus M5A99X

- Kühlung

- Corsair H60

- Speicher

- 16GB DDR3-1866 Crucial

- Grafikprozessor

- Sapphire HD5770

- Display

- 4k 27" DELL

- SSD

- Samsung Evo 850

- HDD

- 2x Seagate 7200.12

- Optisches Laufwerk

- Pioneer, Plextor

- Soundkarte

- Creative X-Fi Xtreme Music

- Gehäuse

- Silverstone TJ-02S

- Netzteil

- Enermax 450W

- Betriebssystem

- Windows 7

Im Endeffekt sind alle größten Module d. h. zur Zeit 8GB Module DR, da 16 Chips benötigt werden um die Kapazität zu erlangen 1Gbit Chips gibt es noch nicht, zumindestens nicht in bezahlbaren Regionen bzw. nonRegECC , sonst gäb es schon 16GB Module

Damals als ich die Vengeance kaufte waren 4GB maximal möglich, die 8GB Module waren erst angekündigt, evtl. auch schon zu exorbitant teuren Preisen verfügbar.

Um Single-Side (SR) zu bekommen muss man also mindestens eine Speichergrößen-Ordnung kleiner kaufen als es zu dem Zeitpunkt gibt (z. B. 4GB statt 8GB Pro Modul) und dann muss man neue Module suchen da dann eher von 16 Chips auf 8 verringert wird. Denn alte DR-Module einfach auf SR umzustellen würden sehr wahrscheinlich zu Kompatibilitäts-Problemen führen, welche jeder RAM Hersteller vermeiden möchte.

Ich persönlich wüsste nicht wann ich mal Privat einen SR in den Händen gehalten hätte, da mir Speicherkapazität wichtig ist und SR mir nie genug bietet

Es ist aber schon echt traurig zu sehen, das die SR/DR Angaben faktisch nicht mit angegeben werden, siehe Geizhals.de.

Damals als ich die Vengeance kaufte waren 4GB maximal möglich, die 8GB Module waren erst angekündigt, evtl. auch schon zu exorbitant teuren Preisen verfügbar.

Um Single-Side (SR) zu bekommen muss man also mindestens eine Speichergrößen-Ordnung kleiner kaufen als es zu dem Zeitpunkt gibt (z. B. 4GB statt 8GB Pro Modul) und dann muss man neue Module suchen da dann eher von 16 Chips auf 8 verringert wird. Denn alte DR-Module einfach auf SR umzustellen würden sehr wahrscheinlich zu Kompatibilitäts-Problemen führen, welche jeder RAM Hersteller vermeiden möchte.

Ich persönlich wüsste nicht wann ich mal Privat einen SR in den Händen gehalten hätte, da mir Speicherkapazität wichtig ist und SR mir nie genug bietet

Es ist aber schon echt traurig zu sehen, das die SR/DR Angaben faktisch nicht mit angegeben werden, siehe Geizhals.de.

SPINA

Grand Admiral Special

- Mitglied seit

- 07.12.2003

- Beiträge

- 18.122

- Renomée

- 985

- Mein Laptop

- Lenovo IdeaPad Gaming 3 (15ARH05-82EY003NGE)

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- ASUS PRIME X370-PRO

- Kühlung

- AMD Wraith Prism

- Speicher

- 2x Micron 32GB PC4-25600E (MTA18ASF4G72AZ-3G2R)

- Grafikprozessor

- Sapphire Pulse Radeon RX 7600 8GB

- Display

- LG Electronics 27UD58P-B

- SSD

- Samsung 980 PRO (MZ-V8P1T0CW)

- HDD

- 2x Samsung 870 QVO (MZ-77Q2T0BW)

- Optisches Laufwerk

- HL Data Storage BH16NS55

- Gehäuse

- Lian Li PC-7NB

- Netzteil

- Seasonic PRIME Gold 650W

- Betriebssystem

- Debian 12.x (x86-64)

- Verschiedenes

- ASUS TPM-M R2.0

Es hat bisher faktisch keine Rolle gespielt. Auf dem Desktop mit nur vier DIMM Slots kann man das Rank-Limit des IMC nicht erreichen. Und bei der Geschwindigkeit gab es nur marginale Unterschiede. Deswegen hat man sich die Angabe oft wegen Desinteresse der Kunden daran gespart. Man musste schließlich seit dem Aussterben des i815(E) Chipsatzes nicht mehr mit den Ranks haushalten. Bei Servern sah das schon immer anders aus. Deswegen treibt man dort nun den ganzen Aufwand mit den LR-DIMMs, die sich gegenüber dem IMC unabhängig von ihrem internen Aufbau stets als single-ranked ausgeben. Das ermöglicht die Adressierung deutlich größerer Speichermengen als bei den nur teilweise gepufferten Registered-DIMMs.Es ist aber schon echt traurig zu sehen, das die SR/DR Angaben faktisch nicht mit angegeben werden.

Schade nur, dass man dabei aus Gründen der Abwärtskompatibilität nicht weiter zu FB-DIMMs aufgeschlossen und zum Beispiel nicht deren exzellente Fehlerkorrektur übernommen hat. FB-DIMMs waren ihrer Zeit einfach zu weit voraus. Zum Beispiel durch die Abkehr von einem parellelen Bus hin zu einer seriellen Schnittstelle. Außerdem hat man den Stromhunger der AMBs zu spät in den Griff bekommen. Als diese Hürde endlich überwunden war und es sparsame und kühle FB-DIMMs gab (übrigens ein Verdienst von Qimonda), war der Niedergang von FB-DIMMs bereits beschlossene Sache.

Aber womöglich kehren FB-DIMMs irgendwann zurück. Man müsste nur die Kosten in den Griff bekommen und sie würden durch ihre nicht zu leugnende Vorteile bei der Leistungsfähigkeit und Zuverlässigkeit alle derzeit gängigen Standards von Heute auf Morgen alt aussehen lassen. Schade, dass sich AMD damals mit seinen Opterons aus rein politischen Gründen gegen den technisch überlegenen, jedoch von Intel forcierten Standard gestellt hat. Das hatte bei RD-RAM (Rambus) noch Sinn gemacht, aber bei FB-DIMMs hat es einen Rückschritt erzwungen. Das hat letztendlich allen geschadet.

Zuletzt bearbeitet:

Shadowtrooper

Grand Admiral Special

- Mitglied seit

- 02.02.2009

- Beiträge

- 2.476

- Renomée

- 35

- Standort

- Krefeld

- Mein Laptop

- Lenovo ThinkPad E130 (i3 3217U)

- Details zu meinem Desktop

- Prozessor

- AMD Phenom II X4 955BE @3,6 GHz 1,375V

- Mainboard

- Gigabyte MA770T UD3P

- Kühlung

- EKL Groß Clockner

- Speicher

- 4*2GB DDR3 1333

- Grafikprozessor

- Gigabyte GTX 750 Ti Windforce OC

- Display

- HP Pavilion 22 Xi

- SSD

- 240GB Kingston HyperX

- HDD

- 3 TB Seagate 7200.14

- Optisches Laufwerk

- LG DVD Brenner

- Soundkarte

- Xonar DX+ AKG K 242 HD

- Gehäuse

- CM 690

- Netzteil

- Seasonic G-360

- Betriebssystem

- Win 7 Prof. 64Bit Sp1

- Webbrowser

- Chrome

Eben bisher war das einfach vollkommen egal lediglich bei einigen Boards mit H61 Chipsatz und 4 Ram bänken musste man das wissen weil man nur 2 DR oder 4 SR Module verbauen konnte.

SPINA

Grand Admiral Special

- Mitglied seit

- 07.12.2003

- Beiträge

- 18.122

- Renomée

- 985

- Mein Laptop

- Lenovo IdeaPad Gaming 3 (15ARH05-82EY003NGE)

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- ASUS PRIME X370-PRO

- Kühlung

- AMD Wraith Prism

- Speicher

- 2x Micron 32GB PC4-25600E (MTA18ASF4G72AZ-3G2R)

- Grafikprozessor

- Sapphire Pulse Radeon RX 7600 8GB

- Display

- LG Electronics 27UD58P-B

- SSD

- Samsung 980 PRO (MZ-V8P1T0CW)

- HDD

- 2x Samsung 870 QVO (MZ-77Q2T0BW)

- Optisches Laufwerk

- HL Data Storage BH16NS55

- Gehäuse

- Lian Li PC-7NB

- Netzteil

- Seasonic PRIME Gold 650W

- Betriebssystem

- Debian 12.x (x86-64)

- Verschiedenes

- ASUS TPM-M R2.0

Ich habe mir gerade einmal die Liste im ComputerBase Forum angeschaut. Schon verrückt was dort alles für DRAM-Module Eingang gefunden haben. Die Aufnahme in die Liste erfolgt natürlich ungefiltert, aber das birgt durchaus Gefahren für den unbedarften Anwender, der sie ohne zu hinterfragen als Kaufempfehlung sieht. Vielen ist gar nicht bewusst welche Gefahren DDR3-2133 oder DDR3-2400 Speicher durch seine hohe Fehlerrate zur Zeit noch birgt. Die Häufigkeit von gekippten Bits wird bei der hohen Frequenz um Größenordnungen über solidem DDR3-1600 Speicher liegen. Und wenn man sich dann noch die Aufpreise anschaut, merkt man erst wie verfehlt es ist einen Kaveri damit zu beschleunigen. Das gesparte Geld steckt man lieber in eine Radeon R7 260X. Die lässt die integrierte Grafik des Kaveri ziemlich alt aussehen und man spielt obendrein kein russisches Roulett mehr mit den eigenen Daten.

bbott

Grand Admiral Special

- Mitglied seit

- 11.11.2001

- Beiträge

- 4.363

- Renomée

- 60

- Mein Laptop

- HP Compaq 8510p

- Details zu meinem Desktop

- Prozessor

- AMD FX-8370

- Mainboard

- Asus M5A99X

- Kühlung

- Corsair H60

- Speicher

- 16GB DDR3-1866 Crucial

- Grafikprozessor

- Sapphire HD5770

- Display

- 4k 27" DELL

- SSD

- Samsung Evo 850

- HDD

- 2x Seagate 7200.12

- Optisches Laufwerk

- Pioneer, Plextor

- Soundkarte

- Creative X-Fi Xtreme Music

- Gehäuse

- Silverstone TJ-02S

- Netzteil

- Enermax 450W

- Betriebssystem

- Windows 7

@SPINA

Ob SR/DR spielt bei der Maximal Bestückung sehr wohl eine Rolle, wenn auch deutlich seltener als früher. Wenn erstmals 8 bzw. 16GB SR RAM Riegel heraus kommen werden einige Mainboards Probleme haben, das Modul überhaupt oder die gesamte Kapazität zu erkennen.

FB-DIMM War einfach viel zu teuer, was wohl daran lag das man zu viel auf einmal wollte, wie man aus deinem Post auch herauslesen kann Aber immerhin einige Dinge hat man doch schon von FB-DIMM in DDR2-4 einfließen lassen.

Aber immerhin einige Dinge hat man doch schon von FB-DIMM in DDR2-4 einfließen lassen.

Um wieder näher an das Kaveri heranzuführen. Müssen Programme für hUMA neu bzw. extra Programmiert werden? Oder reicht es den Compiler hUMA beizubringen und neu zu kompilieren?

Im ersteren Fall würde das durchsetzen von hUMA wohl deutlich länger dauern, wohl fast so lange wie AMD64

Ob SR/DR spielt bei der Maximal Bestückung sehr wohl eine Rolle, wenn auch deutlich seltener als früher. Wenn erstmals 8 bzw. 16GB SR RAM Riegel heraus kommen werden einige Mainboards Probleme haben, das Modul überhaupt oder die gesamte Kapazität zu erkennen.

FB-DIMM War einfach viel zu teuer, was wohl daran lag das man zu viel auf einmal wollte, wie man aus deinem Post auch herauslesen kann

Um wieder näher an das Kaveri heranzuführen. Müssen Programme für hUMA neu bzw. extra Programmiert werden? Oder reicht es den Compiler hUMA beizubringen und neu zu kompilieren?

Im ersteren Fall würde das durchsetzen von hUMA wohl deutlich länger dauern, wohl fast so lange wie AMD64

Dr@

Grand Admiral Special

- Mitglied seit

- 19.05.2009

- Beiträge

- 12.791

- Renomée

- 4.066

- Standort

- Baden-Württemberg

- Aktuelle Projekte

- Collatz Conjecture

- Meine Systeme

- Zacate E-350 APU

- BOINC-Statistiken

- Mein Laptop

- FSC Lifebook S2110, HP Pavilion dm3-1010eg

- Details zu meinem Laptop

- Prozessor

- Turion 64 MT37, Neo X2 L335, E-350

- Mainboard

- E35M1-I DELUXE

- Speicher

- 2x1 GiB DDR-333, 2x2 GiB DDR2-800, 2x2 GiB DDR3-1333

- Grafikprozessor

- RADEON XPRESS 200m, HD 3200, HD 4330, HD 6310

- Display

- 13,3", 13,3" , Dell UltraSharp U2311H

- HDD

- 100 GB, 320 GB, 120 GB +500 GB

- Optisches Laufwerk

- DVD-Brenner

- Betriebssystem

- WinXP SP3, Vista SP2, Win7 SP1 64-bit

- Webbrowser

- Firefox 13

So wie ich es verstehe, muss hUMA explizit verwendet werden. Die Dokumentation hierzu hat AMD noch nicht veröffentlicht.

BoMbY

Grand Admiral Special

- Mitglied seit

- 22.11.2001

- Beiträge

- 7.468

- Renomée

- 293

- Standort

- Aachen

- Details zu meinem Desktop

- Prozessor

- Ryzen 3700X

- Mainboard

- Gigabyte X570 Aorus Elite

- Kühlung

- Noctua NH-U12A

- Speicher

- 2x16 GB, G.Skill F4-3200C14D-32GVK @ 3600 16-16-16-32-48-1T

- Grafikprozessor

- RX 5700 XTX

- Display

- Samsung CHG70, 32", 2560x1440@144Hz, FreeSync2

- SSD

- AORUS NVMe Gen4 SSD 2TB, Samsung 960 EVO 1TB, Samsung 840 EVO 1TB, Samsung 850 EVO 512GB

- Optisches Laufwerk

- Sony BD-5300S-0B (eSATA)

- Gehäuse

- Phanteks Evolv ATX

- Netzteil

- Enermax Platimax D.F. 750W

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox

Also mein letzter Stand war, dass z.B. OpenCL- und Direct Compute Programme theoretisch direkt mit hUMA funktionieren können, sobald der Treiber das unterstützt.

Von: http://hsafoundation.com/f-a-q/

Edit: Natürlich wird man da noch mehr rausholen können, wenn man das direkt anspricht.

You can begin developing application today for HSA via OpenCL and C++AMP, this application will automatically take advantage of the infrastructure when HSA enabled device come to market.

Von: http://hsafoundation.com/f-a-q/

Edit: Natürlich wird man da noch mehr rausholen können, wenn man das direkt anspricht.

Zuletzt bearbeitet:

Dr@

Grand Admiral Special

- Mitglied seit

- 19.05.2009

- Beiträge

- 12.791

- Renomée

- 4.066

- Standort

- Baden-Württemberg

- Aktuelle Projekte

- Collatz Conjecture

- Meine Systeme

- Zacate E-350 APU

- BOINC-Statistiken

- Mein Laptop

- FSC Lifebook S2110, HP Pavilion dm3-1010eg

- Details zu meinem Laptop

- Prozessor

- Turion 64 MT37, Neo X2 L335, E-350

- Mainboard

- E35M1-I DELUXE

- Speicher

- 2x1 GiB DDR-333, 2x2 GiB DDR2-800, 2x2 GiB DDR3-1333

- Grafikprozessor

- RADEON XPRESS 200m, HD 3200, HD 4330, HD 6310

- Display

- 13,3", 13,3" , Dell UltraSharp U2311H

- HDD

- 100 GB, 320 GB, 120 GB +500 GB

- Optisches Laufwerk

- DVD-Brenner

- Betriebssystem

- WinXP SP3, Vista SP2, Win7 SP1 64-bit

- Webbrowser

- Firefox 13

HSA beschleunigt laut AMD einige OpenCL-Fähigkeiten auch ohne expliziten HUMA-Support.

Ich könnte mir vorstellen, dass dies für die Zero-Copy-Sachen gilt. Genaueres weiß man aber nicht.

gruffi

Grand Admiral Special

- Mitglied seit

- 08.03.2008

- Beiträge

- 5.393

- Renomée

- 65

- Standort

- vorhanden

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 5 1600

- Mainboard

- MSI B350M PRO-VDH

- Kühlung

- Wraith Spire

- Speicher

- 2x 8 GB DDR4-2400 CL16

- Grafikprozessor

- XFX Radeon R7 260X

- Display

- LG W2361

- SSD

- Crucial CT250BX100SSD1

- HDD

- Toshiba DT01ACA200

- Optisches Laufwerk

- LG Blu-Ray-Brenner BH16NS40

- Soundkarte

- Realtek HD Audio

- Gehäuse

- Sharkoon MA-I1000

- Netzteil

- be quiet! Pure Power 9 350W

- Betriebssystem

- Windows 10 Professional 64-bit

- Webbrowser

- Mozilla Firefox

- Verschiedenes

- https://valid.x86.fr/mb4f0j

Ich denke nicht mal, dass ein Treiber notwendig ist. In deinem zitierten Text steht ja auch nur "HSA enabled device". hUMA ist ein Hardwarefeature. Das sollte also auch ohne expliziten Softwaresupport funktionieren. Das ist was anderes als zB ISA-Erweiterungen wie SSE oder AVX, die wiederum expliziten Softwaresupport erfordern. Man kann hUMA vielleicht am besten mit einem shared Cache vergleichen. Auf diesen können mehrere Kerne auch direkt zugreifen, ohne dass erst was von einem zum anderen Cache kopiert werden muss. Völlig unabhängig von der verwendeten Software.Also mein letzter Stand war, dass z.B. OpenCL- und Direct Compute Programme theoretisch direkt mit hUMA funktionieren können, sobald der Treiber das unterstützt.

Ähnliche Themen

- Antworten

- 638

- Aufrufe

- 141K

- Antworten

- 12

- Aufrufe

- 6K

- Antworten

- 0

- Aufrufe

- 44K