App installieren

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: This feature may not be available in some browsers.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Bulldozer rollt an....

- Ersteller neax

- Erstellt am

- Status

- Für weitere Antworten geschlossen.

Dr@

Grand Admiral Special

- Mitglied seit

- 19.05.2009

- Beiträge

- 12.791

- Renomée

- 4.066

- Standort

- Baden-Württemberg

- Aktuelle Projekte

- Collatz Conjecture

- Meine Systeme

- Zacate E-350 APU

- BOINC-Statistiken

- Mein Laptop

- FSC Lifebook S2110, HP Pavilion dm3-1010eg

- Details zu meinem Laptop

- Prozessor

- Turion 64 MT37, Neo X2 L335, E-350

- Mainboard

- E35M1-I DELUXE

- Speicher

- 2x1 GiB DDR-333, 2x2 GiB DDR2-800, 2x2 GiB DDR3-1333

- Grafikprozessor

- RADEON XPRESS 200m, HD 3200, HD 4330, HD 6310

- Display

- 13,3", 13,3" , Dell UltraSharp U2311H

- HDD

- 100 GB, 320 GB, 120 GB +500 GB

- Optisches Laufwerk

- DVD-Brenner

- Betriebssystem

- WinXP SP3, Vista SP2, Win7 SP1 64-bit

- Webbrowser

- Firefox 13

Jetzt bleibt nur noch die Frage zu erörtern, warum man dann vor Monaten seinen Kunden ein gutes Argument genommen hat, eine AM3-Plattform zu kaufen.

Ich bin bereits auf die Erklärung gespannt.

Ich bin bereits auf die Erklärung gespannt.

Opteron

Redaktion

☆☆☆☆☆☆

Erst mal schauen, obs wirklich stimmt ^^Jetzt bleibt nur noch die Frage zu erörtern, warum man dann vor Monaten seinen Kunden ein gutes Argument genommen hat, eine AM3-Plattform zu kaufen.

Ich bin bereits auf die Erklärung gespannt.

Aber falls ja - ja dann wirds lustig .. da müßte man AMD ja fast für den Darwin Award nominieren, so wie die ihr eigenes Geschäft gekillt haben

Tiefere Diskussionen dann hier, hab mal schnell ne Usernews getippselt.

http://www.planet3dnow.de/vbulletin/showthread.php?t=392236

Die Sache bei AsRock ist nämlich auch mysteriös .. wieso haben sie dort beim Namen das "Plus" wieder entfernt ... dabei hat das eindeutig nen AM3b Sockel ...

Markus Everson

Grand Admiral Special

.. da müßte man AMD ja fast für den Darwin Award nominieren, so wie die ihr eigenes Geschäft gekillt haben

Amen Bruder!

Markus komm dieser Geniestreich des AMD-Marketings. Du hast es doch die ganze Zeit gewusst tief in deinem innersten. Wenn du glaubst es geht nicht mehr schlimmer AMD legt noch einen ordentlich Oben drauf.

Ich bin jedenfalls sollte das stimmen, mehr als nur tief beeindruckt(und vielleicht ganz froh letztes Jahr ein 870 Mobo gekauft zu haben aber ich bekomme bestimmt kein BIOS von Gigabunt).

Ich bin jedenfalls sollte das stimmen, mehr als nur tief beeindruckt(und vielleicht ganz froh letztes Jahr ein 870 Mobo gekauft zu haben aber ich bekomme bestimmt kein BIOS von Gigabunt).

Duplex

Admiral Special

wenns stimmt kann ich mein Crosshair IV F. behalten, es hat sogar DDR3-2000 Support laut Asus

Die Features die ich dann nicht nutzen kann interessieren mich sowieso nicht, die CPU wird ja dadurch nicht langsamer, über den Referenztakt wird die CPU bis zum Anschlag übertaktet mein Thuban 1055T macht 300x14 @1.5v (50% mehr Takt)

mein Thuban 1055T macht 300x14 @1.5v (50% mehr Takt)

Die Features die ich dann nicht nutzen kann interessieren mich sowieso nicht, die CPU wird ja dadurch nicht langsamer, über den Referenztakt wird die CPU bis zum Anschlag übertaktet

mein Thuban 1055T macht 300x14 @1.5v (50% mehr Takt)

mein Thuban 1055T macht 300x14 @1.5v (50% mehr Takt)gruffi

Grand Admiral Special

- Mitglied seit

- 08.03.2008

- Beiträge

- 5.393

- Renomée

- 65

- Standort

- vorhanden

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 5 1600

- Mainboard

- MSI B350M PRO-VDH

- Kühlung

- Wraith Spire

- Speicher

- 2x 8 GB DDR4-2400 CL16

- Grafikprozessor

- XFX Radeon R7 260X

- Display

- LG W2361

- SSD

- Crucial CT250BX100SSD1

- HDD

- Toshiba DT01ACA200

- Optisches Laufwerk

- LG Blu-Ray-Brenner BH16NS40

- Soundkarte

- Realtek HD Audio

- Gehäuse

- Sharkoon MA-I1000

- Netzteil

- be quiet! Pure Power 9 350W

- Betriebssystem

- Windows 10 Professional 64-bit

- Webbrowser

- Mozilla Firefox

- Verschiedenes

- https://valid.x86.fr/mb4f0j

Nö, mit Wikipedia kommen wir hier nicht weiter. Das ist zwar nett in einem allgemeinen Kontext. Wir reden aber ganz konkret von AMD und deren Architekturen. Also bleibe auch bitte bei der AMD Terminologie. Ansonsten blickt hier irgendwann gar keiner mehr durch.Nö, da kommen wir nicht weiter, die Wikis fußen auf wissenschaftlicher, anerkannter Basis. Unendlich viel besser als irgendwelchem Marketinggeschurbel. V.a. wenn die Argumentation wie bei den K10<>BD Pipelines nicht stringent ist, siehe unten.

Mache es doch nicht unnötig kompliziert. Alles was nach dem Scheduler kommt, bezeichnet AMD als Pipes. Das sind im Wesentlichen die "Leiterbahnen" zu den Ausführungseinheiten und die Ausführungseinheiten selbst. Wenn du noch mehr Details wissen willst, und was eventuell noch dazu gehört, dann solltest du am besten bei AMD nachfragen. Viel mehr geht aus den Docs, die ich kenne, nicht hervor.Aktueller Stand ist jetzt "Pipe = Anbindung + X", bitte das "X" genauer spezifizieren.

Ach mann, lies dir doch bitte erstmal die AMD Docs dazu durch. Du scheinst die Terminologie überhaupt nicht zu kennen. Ich kann zB den Software Optimization Guide für 10h empfehlen. Ansonsten macht diese Diskussion überhaupt keinen Sinn, wenn du nicht mal die Begrifflichkeiten richtig zuordnen kannst. Vielleicht hilft dir für den Anfang ein kleiner Auszug:Ok, wenn Du von der (einen)"Integer Execution Pipeline" redest, bist Du genau im Problemgebiet. Wieso solls da nur eine geben ?

Mit Integer Execution Pipeline ist die gesamte Logik gemeint, also alle Pipes. Bitte setze den Begriff Pipe nicht mit Pipeline gleich. Den Fehler hast du ja nun schon mit den Ausführungseinheiten gemacht.The integer execution pipeline consists of three identical pipes (0, 1, and 2).

Doch.Ne die Pipes beinhalten keine Ausführungseinheiten

Each integer pipe consists of an arithmetic-logic unit (ALU) and an address generation unit (AGU).

Nein. Ausführungseinheiten sind keine Pipeline(s) bzw durch diese implementiert. Begreife das doch endlich mal. Ausführungseinheiten sind Teil der Pipeline, nicht mehr und nicht weniger. Stell dir das wie ein Fliessband in der Industrie vor. Die Pipeline ist das Fliessband. Die Ausführungseinheiten sind nun eine oder mehrere Bearbeitungsstationen an bestimmten Positionen des Fliessbandes. Nur weil du ein Fliessband baust, hast du noch lange keine Bearbeitungsstationen. Die Bearbeitungsstationen müssen separat gebaut und angebunden werden.die Ausführungseinheiten sind durch Pipelines/Pipelining implementiert.

Während der Cebit unterhielt sich PC Games Hardware auch mit dem Mainboard-Hersteller Asrock. Das eigenständige Tochterunternehmen von Asus dementierte die Lauffähigkeit von Bulldozer-CPUs auf dem Sockel AM3 (ohne Plus!).

http://www.pcgameshardware.de/aid,8...mentiert-plus-Sockelvergleich/Mainboard/News/Verlässliche Informationen mit gut informierten Quellen, zu denen wir Kontakt halten, sprechen derzeit davon, dass AMD an der AM3-Kompatibilität von Bulldozer arbeitet.

Es bleibt verwirrend.

Ganz simpel gedacht ist ja Programm Kontrollcode eher Integer lastig mit einigen FP oder SIMD Befehlen zur Berechung. Da könnte vom Gefühl her der AMD Ansatz ja durchaus funktionieren.

...Was aber z.B.: bei Software Renderern, Distributed Computing oder Matlab? Wenn die Performance eher von den erreichbaren FLOPs abhängt, könnte die gemeinsame FP Einheit schnell limitieren. Dann habe ich mit Zambezi keinen 8Core Prozessor, sondern doch wieder eher einen Quadcore mit einer relativ schnellen FP Unit.

Ich weiß nicht, ob das noch aktuell ist, aber uns wurde im Studium erzählt, dass die FPU von einem Thread selbst bei sehr FP-lastigen Programmen kaum mehr als zu ~60% ausgelastet wird. Das liegt wohl daran, dass man immer noch Kontrollfluss, Adressgenerierung usw. mit drin hat, was die Domäne der Int-Einheiten ist. Das da was dran ist, sieht man auch daran, dass MT bei FP-Code wirkungsvoller ist als bei Int-Code. Unter Berücksichtigung dieser Tatsache ist das MT nur für die FPU, wie es BD macht vielleicht gar keine so schlechte Idee. Außerdem hat man ja im Vergleich zum Vorgänger ja den gleichen max. Durchsatz (1x 128Bit / Kern). Auch Sandy Bridge bietet da nicht mehr. Nur, wenn man mit 256Bit Befehlen arbeitet, hat SB mehr theoretischen Durchsatz pro Kern, was aber wieder anders aussieht, wenn man FMA benutzt.

mtb][sledgehammer

Grand Admiral Special

- Mitglied seit

- 11.11.2001

- Beiträge

- 4.375

- Renomée

- 30

- Mein Laptop

- HP Compaq nx6125

- Details zu meinem Desktop

- Prozessor

- Athlon XP 2500+

- Mainboard

- Asrock K7S8XE

- Kühlung

- AC / selfmade Wakü

- Speicher

- 1 GB PC3200 Team Memory

- Grafikprozessor

- ATI Radeon 9500

- Display

- 20,1'' Samsung SyncMaster 205BW 1680x1050

- HDD

- Samsung SV0802N

- Optisches Laufwerk

- Toshiba DVD-ROM SD-M1612

- Soundkarte

- Creative SB Live! Player 1024

- Gehäuse

- Chenbro Net Server Tower

- Netzteil

- Coba 400 Watt (silent)

- Betriebssystem

- Windows XP, Ubuntu Linux

- Webbrowser

- Mozilla Firefox

- Verschiedenes

- knc TV Station , Terratec Cinergy 1200 DVB-C

Habe das ein bischen mitverfolgt: Es geht doch darum, ob ein BD Kern am Ende mehr oder weniger ALUs hat als der Phenom?Nein. Ausführungseinheiten sind keine Pipeline(s) bzw durch diese implementiert. Begreife das doch endlich mal. Ausführungseinheiten sind Teil der Pipeline, nicht mehr und nicht weniger. Stell dir das wie ein Fliessband in der Industrie vor. Die Pipeline ist das Fliessband. Die Ausführungseinheiten sind nun eine oder mehrere Bearbeitungsstationen an bestimmten Positionen des Fliessbandes. Nur weil du ein Fliessband baust, hast du noch lange keine Bearbeitungsstationen. Die Bearbeitungsstationen müssen separat gebaut und angebunden werden.

Zum Phenom: Ich würde mich was AMDs vokabular angeht an dem orientieren, was man im

"Software Optimization Guide for AMD Family 10h and 12h Processors (40546 Rev. 3.13 February 2011)" steht:

Und natürlich das Bild (siehe Anhang, Quelle AMD.com, "Software Optimization Guide for AMD Family 10h and 12h Processors (40546 Rev. 3.13 February 2011)") Demnach ist Phenom laut AMD's aktuellem Sprachgebrauch ein 3 ALU Design.Three-way integer execution; Three-way address generation

Zum Bulldozer gibts sowiet ich das verfolgt habe nur die Marketingslides? Oder noch mehr? Ich glaube Dresdenboy's Artikel enthält keine verlässlichen Aussagen dazu?

Dresdenboy

Redaktion

☆☆☆☆☆☆

Stimmt, verlässlich war da noch nicht möglich. Wird wohl Zeit für ein Updatemtb][sledgehammer;4388215 schrieb:Zum Bulldozer gibts sowiet ich das verfolgt habe nur die Marketingslides? Oder noch mehr? Ich glaube Dresdenboy's Artikel enthält keine verlässlichen Aussagen dazu?

Jetzt steht im Manual übrigens two-way integer execution, two-way address generation.

.

EDIT :

.

Hiroshige Goto hat seinen ISSCC Bulldozer-Artikel online: http://pc.watch.impress.co.jp/docs/column/kaigai/20110301_430044.html

gruffi

Grand Admiral Special

- Mitglied seit

- 08.03.2008

- Beiträge

- 5.393

- Renomée

- 65

- Standort

- vorhanden

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 5 1600

- Mainboard

- MSI B350M PRO-VDH

- Kühlung

- Wraith Spire

- Speicher

- 2x 8 GB DDR4-2400 CL16

- Grafikprozessor

- XFX Radeon R7 260X

- Display

- LG W2361

- SSD

- Crucial CT250BX100SSD1

- HDD

- Toshiba DT01ACA200

- Optisches Laufwerk

- LG Blu-Ray-Brenner BH16NS40

- Soundkarte

- Realtek HD Audio

- Gehäuse

- Sharkoon MA-I1000

- Netzteil

- be quiet! Pure Power 9 350W

- Betriebssystem

- Windows 10 Professional 64-bit

- Webbrowser

- Mozilla Firefox

- Verschiedenes

- https://valid.x86.fr/mb4f0j

Nein, es ging eigentlich um die Begrifflichkeiten. Die Anzahl der Ausführungseinheiten dürfte ja mittlerweile bekannt sein. Bisher waren es ALU/AGU Pärchen, jeweils eines an insgesamt 3 Pipes. Bei Bulldozer sind es 2 ALUs und 2 AGUs, jeweils eine Einheit an insgesamt 4 Pipes.mtb][sledgehammer;4388215 schrieb:Habe das ein bischen mitverfolgt: Es geht doch darum, ob ein BD Kern am Ende mehr oder weniger ALUs hat als der Phenom?

Ge0rgy

Grand Admiral Special

- Mitglied seit

- 14.07.2006

- Beiträge

- 4.322

- Renomée

- 82

- Mein Laptop

- Lenovo Thinkpad X60s

- Details zu meinem Desktop

- Prozessor

- Phenom II 955 BE

- Mainboard

- DFI LanParty DK 790FXB-M3H5

- Kühlung

- Noctua NH-U12P

- Speicher

- 4GB OCZ Platinum DDR1600 7-7-7 @ 1333 6-6-6

- Grafikprozessor

- Radeon 4850 1GB

- HDD

- Western Digital Caviar Black 1TB

- Netzteil

- Enermax Modu 525W

- Betriebssystem

- Linux, Vista x64

- Webbrowser

- Firefox 3.5

Anders ausgedrückt, die Gesamt-Anzahl mag weniger werden, dafür sind sie flexibler verwendbar.

Wenn mir jetzt aber hier noch einer mit dem bereits bis zum erbrechen durchgekauten Argument kommt BD müsse bei INT-Code langsamer sein als K10 (taktbereinigt) nur weil er 1/3 weniger ALUs hat, der soll sich bitte als Schreiberling bei der Computer-Bild bewerben. Die brauchen solche Leute um ihr "Niveau" zu halten...![Augen rollen (sarkastisch) :] :]](https://www.planet3dnow.de/vbulletin/images/smilies/rolleyes.gif)

Wenn mir jetzt aber hier noch einer mit dem bereits bis zum erbrechen durchgekauten Argument kommt BD müsse bei INT-Code langsamer sein als K10 (taktbereinigt) nur weil er 1/3 weniger ALUs hat, der soll sich bitte als Schreiberling bei der Computer-Bild bewerben. Die brauchen solche Leute um ihr "Niveau" zu halten...

![Augen rollen (sarkastisch) :] :]](https://www.planet3dnow.de/vbulletin/images/smilies/rolleyes.gif)

Opteron

Redaktion

☆☆☆☆☆☆

Wie besagt, der Wiki Artikel ist 100% i.O. selbiges kann man vom Marketingschmierereien ganz sicher nicht behaupten.Nö, mit Wikipedia kommen wir hier nicht weiter. Das ist zwar nett in einem allgemeinen Kontext. Wir reden aber ganz konkret von AMD und deren Architekturen. Also bleibe auch bitte bei der AMD Terminologie. Ansonsten blickt hier irgendwann gar keiner mehr durch.

AMD ist mir egal, ich rede mit Dir, und ich will wissen, was Du darunter verstehst. Du wirst ja wohl wissen, worüber Du redest, oder nicht ?Mache es doch nicht unnötig kompliziert. Alles was nach dem Scheduler kommt, bezeichnet AMD als Pipes. Das sind im Wesentlichen die "Leiterbahnen" zu den Ausführungseinheiten und die Ausführungseinheiten selbst. Wenn du noch mehr Details wissen willst, und was eventuell noch dazu gehört, dann solltest du am besten bei AMD nachfragen.

Ok, AMD DOCs, sind etwas besser als Marketing, würde ich unter Umständen auch akzeptieren, wenn alles eindeutig und genau definiert ist.Ach mann, lies dir doch bitte erstmal die AMD Docs dazu durch. Du scheinst die Terminologie überhaupt nicht zu kennen. Ich kann zB den Software Optimization Guide für 10h empfehlen. Ansonsten macht diese Diskussion überhaupt keinen Sinn, wenn du nicht mal die Begrifflichkeiten richtig zuordnen kannst. Vielleicht hilft dir für den Anfang ein kleiner Auszug:

Jo, aber wer sagt denn, dass die Bearbeitungsstation eine Pipe sein muss ? Bzw. wieso überhaupt ein Fließband bauen ?Nein. Ausführungseinheiten sind keine Pipeline(s) bzw durch diese implementiert. Begreife das doch endlich mal. Ausführungseinheiten sind Teil der Pipeline, nicht mehr und nicht weniger. Stell dir das wie ein Fliessband in der Industrie vor. Die Pipeline ist das Fliessband. Die Ausführungseinheiten sind nun eine oder mehrere Bearbeitungsstationen an bestimmten Positionen des Fliessbandes. Nur weil du ein Fliessband baust, hast du noch lange keine Bearbeitungsstationen. Die Bearbeitungsstationen müssen separat gebaut und angebunden werden.

Die Sichtweise ist sehr eingeschränkt. Wenn Du eine CPU mittels Pipelining implementierst, dann ist sind die FU=Ausführungseinheiten ganz selbstverständlich Teil der Pipeline, das ist ne Binsenweißheit. Wenn Du oben genannte Licht& Wärmequelle mittels Kernfusion implementierst, dann fusioniert da natürlich Wasserstoff, was denn auch sonst ?

Aber Functional Units gibts schon viel länger als es Pipelining oder Pipeline gibt. Grab mal ein paar Schaltpläne aus den 70/80ern heraus, da findest Du massenhaft Functional Units, ALUs, FPUs, ICUs, etc. pp. aber kein Wort von Pipe oder Pipeline.

Selbst der K10 ist nicht fully pipelined:

Wie willst Du nun die Div Einheit benennen ? Ist das noch ne "Div-pipe" ? Falls ja wieso ? Was macht eine Pipe aus ? Muss sie nun pipelined sein, oder nicht ? Reichts es, wenn das Fließbandkonzept außenherum benützt wird ?For AMD Family 12h it is recommended to use the division instructions DIV or IDIV (refer to Appendix C to review the latency of DIV/ IDIV instructions). DIV and IDIV instructions are now fastpath instructions. The divider is not pipelined and can only execute one div instruction at any given point of time. The latency of unit to produce the quotient is 8+ ceil(num quotient bits/2). The remainder is available 2 cycles later.

Achso ? Aber welche Pipes denn nun ? Was sind alle ? Jetzt mit oder ohne AGUs ?Mit Integer Execution Pipeline ist die gesamte Logik gemeint, also alle Pipes. Bitte setze den Begriff Pipe nicht mit Pipeline gleich.The integer execution pipeline consists of three identical pipes (0, 1, and 2).

Das ist jetzt die Frage ... schauen wir mal, was das AMD PDF dazu sagt und komplettieren wir mal Deine Definition um den nachfolgenden Satz:

Ok, also jede Pipe besteht aus ner ALU und ner AGU. Soweit so gut. Unterstreicht Deinen Punkt, dass die Darstellung der MC FUs richtig wäre.The integer execution pipeline consists of three identical pipes (0, 1, and 2). Each integer pipe consists of an arithmetic-logic unit (ALU) and an address generation unit (AGU).

Aber wenn man etwas weiter herumblättern dann kommt man auch auf diese Textstelle:

Toll .. also diesmal ohne AGUs ? Einmal eine Textstelle mit einmal ohne AGU Pipe ? Prima Definition, und auf sowas auf dieser tollen "AMD Terminologie" willst Du Deine Argumentation aufbauen ? Ja, wenn wir die benützen blickt wirklich keiner mehr durch.The processors move integer instructions through the integer execution pipeline, which consists of the integer scheduler and the ALUs, as shown in Figure 8.

Kein Wunder, dass dann die Argumentatino so gut klappt, die erste Textstelle paßt zum K10, die zweite zum BD. Da die AGUs in der 2. Def. nicht unter INT Pipeline zusammengefaßt werden, "darf" mans in dem Fall anscheinend extra zählen.

Deine Argumentation ist im Moment somit Folgende:

AMD definiert Pipes einmal so und einmal so, aber das macht ja nichts, denn in beiden Fällen sind es "Pipes".

Selbstreden ein irrer Standpunkt

Da bin dann selbst ich mit meiner Geduld am Ende.

Auf die ganze Pipeline und Pipe Definition kann man mMn pfeiffen. Wichtig ist zu wissen, ob ein Prozessor nun die Fließbandtechnik / Pipelining anwendet, oder nicht, dann die Anzahl/Typ der FUs und zum Schluß deren Superskalarität.

Alles andere ist dann doch nur wieder Wortklauberei und Marketinggedöns, selbst im Optimization Handbuch mit der "AMD Terminologie".

mtb][sledgehammers Beitrag bringt das ganze dann auch auf dem Punkt, dort wird die Superskalarität mittels der "x-way" Bezeichnung benannt, einmal 3way einmal 2way. Mehr muss man nicht wissen.

Wenn Du Dir jetzt von AMD ein X für ein U vormachen lassen willst, da sie mal schnell die "Pipe" Definition auswechseln, dann bitteschön. Das wäre dann der Diskussionsendpunkt.

Ich verlass mich lieber auf technischen Details und felsenfeste, anerkannte Definitionen.

Zuletzt bearbeitet:

gruffi

Grand Admiral Special

- Mitglied seit

- 08.03.2008

- Beiträge

- 5.393

- Renomée

- 65

- Standort

- vorhanden

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 5 1600

- Mainboard

- MSI B350M PRO-VDH

- Kühlung

- Wraith Spire

- Speicher

- 2x 8 GB DDR4-2400 CL16

- Grafikprozessor

- XFX Radeon R7 260X

- Display

- LG W2361

- SSD

- Crucial CT250BX100SSD1

- HDD

- Toshiba DT01ACA200

- Optisches Laufwerk

- LG Blu-Ray-Brenner BH16NS40

- Soundkarte

- Realtek HD Audio

- Gehäuse

- Sharkoon MA-I1000

- Netzteil

- be quiet! Pure Power 9 350W

- Betriebssystem

- Windows 10 Professional 64-bit

- Webbrowser

- Mozilla Firefox

- Verschiedenes

- https://valid.x86.fr/mb4f0j

Ja, kann man so sagen.Anders ausgedrückt, die Gesamt-Anzahl mag weniger werden, dafür sind sie flexibler verwendbar.

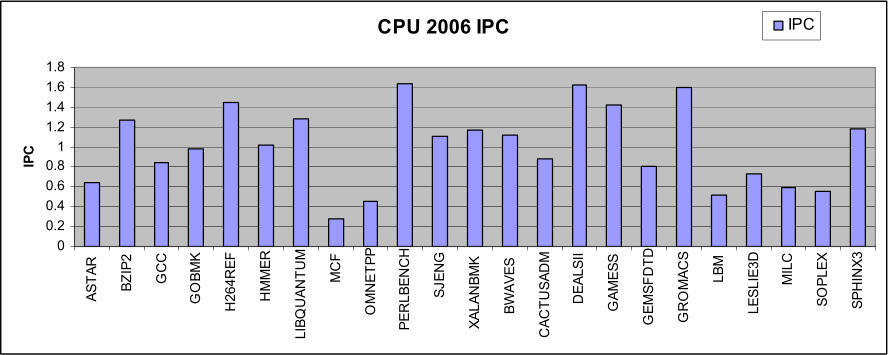

Um das mal noch etwas genauer zu erläutern, eine amerikanische Universität hatte vor einiger Zeit eine Analyse der IPC eines Core 2 Duo Prozessors anhand von SPEC CPU2006 gemacht (PERFORMANCE ANALYSIS OF INTEL CORE 2 DUO PROCESSOR). Die Core Architektur liegt ja, was IPC betrifft, nicht so weit entfernt vom K10. Dabei herausgekommen ist, dass die durchschnittliche IPC irgendwo bei 1 liegt.Wenn mir jetzt aber hier noch einer mit dem bereits bis zum erbrechen durchgekauten Argument kommt BD müsse bei INT-Code langsamer sein als K10 (taktbereinigt) nur weil er 1/3 weniger ALUs hat, der soll sich bitte als Schreiberling bei der Computer-Bild bewerben. Die brauchen solche Leute um ihr "Niveau" zu halten...

Der verwendete Microsoft C/C++ Compiler ist sicherlich nicht für besonders gute Optimierung bekannt. Dennoch, selbst mit 2 ALUs und 2 AGUs hat man noch ausreichend Spielraum für Verbesserung der IPC. Die Frage wird einfach sein, wie effizient arbeitet die Bulldozer Pipeline bis dahin und um wie viel besser kann sie die Ausführungseinheiten auslasten.

Dresdenboy

Redaktion

☆☆☆☆☆☆

Hiroshige Goto hat noch einen Artikel veröffentlicht:

http://pc.watch.impress.co.jp/docs/column/kaigai/20110302_430341.html

bzw.

http://translate.google.com/transla...co.jp/docs/column/kaigai/20110302_430341.html

http://pc.watch.impress.co.jp/docs/column/kaigai/20110302_430341.html

bzw.

http://translate.google.com/transla...co.jp/docs/column/kaigai/20110302_430341.html

gruffi

Grand Admiral Special

- Mitglied seit

- 08.03.2008

- Beiträge

- 5.393

- Renomée

- 65

- Standort

- vorhanden

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 5 1600

- Mainboard

- MSI B350M PRO-VDH

- Kühlung

- Wraith Spire

- Speicher

- 2x 8 GB DDR4-2400 CL16

- Grafikprozessor

- XFX Radeon R7 260X

- Display

- LG W2361

- SSD

- Crucial CT250BX100SSD1

- HDD

- Toshiba DT01ACA200

- Optisches Laufwerk

- LG Blu-Ray-Brenner BH16NS40

- Soundkarte

- Realtek HD Audio

- Gehäuse

- Sharkoon MA-I1000

- Netzteil

- be quiet! Pure Power 9 350W

- Betriebssystem

- Windows 10 Professional 64-bit

- Webbrowser

- Mozilla Firefox

- Verschiedenes

- https://valid.x86.fr/mb4f0j

Es geht nicht darum, ob der Wikipedia Artikel iO ist oder nicht. Er ist schlichtweg nicht von Belang bei der Diskussion.Wie besagt, der Wiki Artikel ist 100% i.O. selbiges kann man vom Marketingschmierereien ganz sicher nicht behaupten.

Dein Problem. Ich spreche von dem, was AMD an technischer Dokumentation rausgibt. Wenn dich das nicht interessiert, sprichst du auch nicht mit mir. Der Rest deines Beitrages ist damit obsolet. Offenbar hast du bisher noch nicht wirklich viel mit technischen Dokumentationen zu tun gehabt. Du steigerst dich wieder mal in etwas hinein, was völlig nebensächlich ist. Fakt ist, eine Pipe ist kein Synonym für eine Ausführungseinheit, wie von dir behauptet. Darum ging es doch. EOD.AMD ist mir egal

Markus Everson

Grand Admiral Special

"Bulldozer Orochi-basierte 300 mm ² Die-Größe geschätzt geschnitten werden. AMD Istanbul(Thuban) 45nm 346mm AMDs aktuelle Six-Core "Istanbul (Istanbul) / Thuban (Tuban)" ist ein 45-nm-Die-Größe von 346 mm ² in den Prozess, so dass die Produktionskosten niedriger ist als die 6-Kern-Prinzip."

-> 8core Bulldozer 10% weniger Fläche als Thuban, vermutlich etwas geringere Herstellungskosten (höhere Kosten pro Wafer-Rohling, Yieldrate)

Nix aufregendes, aber für mich ein Indiz das AMD die Preise nicht zu hoch treiben muß um finanziell wieder etwas Luft zu bekommen

-> 8core Bulldozer 10% weniger Fläche als Thuban, vermutlich etwas geringere Herstellungskosten (höhere Kosten pro Wafer-Rohling, Yieldrate)

Nix aufregendes, aber für mich ein Indiz das AMD die Preise nicht zu hoch treiben muß um finanziell wieder etwas Luft zu bekommen

denjo

Grand Admiral Special

- Mitglied seit

- 28.12.2005

- Beiträge

- 3.746

- Renomée

- 116

- Standort

- Kellinghusen

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- PDM <--- sowas gabs mal :(

- Lieblingsprojekt

- all

- Meine Systeme

- Ryzen 7 1700, 3.60GHz

- BOINC-Statistiken

- Folding@Home-Statistiken

- Details zu meinem Desktop

- Prozessor

- Ryzen 9 3900X, 4,1Ghz All Core VID 1.13

- Mainboard

- ASUS ROG Strix B550-E Gaming

- Kühlung

- Thermalright Le Grand Macho RT

- Speicher

- Gskill F4-3600C16-8GTZNC -> 4*8 GB 3733Mhz (16-19-19-19-35)

- Grafikprozessor

- 5700XT Nitro+

- Display

- LG UltraGear 27GL850-B

- SSD

- Samsung 970 NVMe 1 TB

- HDD

- Western Digital Blue 4TB + 500 Samsung

- Optisches Laufwerk

- gehören der Vergangenheit an.

- Soundkarte

- Onboard

- Gehäuse

- bequite! PURE BASE 500

- Netzteil

- Enermax Revolution87+ 550 W GOLD -> Thx p3d

- Betriebssystem

- Windows X

- Webbrowser

- Chrome, Firefox

- Verschiedenes

- MEHR POWER ^^

- Internetanbindung

- ▼600 ▲50

wie gross wäre Thuban in 32 nm ?!

Onkel_Dithmeyer

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 22.04.2008

- Beiträge

- 12.943

- Renomée

- 4.014

- Standort

- Zlavti

- Aktuelle Projekte

- Universe@home

- Lieblingsprojekt

- Universe@home

- Meine Systeme

- cd0726792825f6f563c8fc4afd8a10b9

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- Ryzen 9 3900X @4000 MHz//1,15V

- Mainboard

- MSI X370 XPOWER GAMING TITANIUM

- Kühlung

- Custom Wasserkühlung vom So. G34

- Speicher

- 4x8 GB @ 3000 MHz

- Grafikprozessor

- Radeon R9 Nano

- Display

- HP ZR30W & HP LP3065

- SSD

- 2 TB ADATA

- Optisches Laufwerk

- LG

- Soundkarte

- Im Headset

- Gehäuse

- Xigmatek

- Netzteil

- BeQuiet Dark Pro 9

- Tastatur

- GSkill KM570

- Maus

- GSkill MX780

- Betriebssystem

- Ubuntu 20.04

- Webbrowser

- Firefox Version 94715469

- Internetanbindung

- ▼100 Mbit ▲5 Mbit

wie gross wäre Thuban in 32 nm ?!

Wenn mein Dreisatz stimmt:

346*32/45=246mm²

denjo

Grand Admiral Special

- Mitglied seit

- 28.12.2005

- Beiträge

- 3.746

- Renomée

- 116

- Standort

- Kellinghusen

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- PDM <--- sowas gabs mal :(

- Lieblingsprojekt

- all

- Meine Systeme

- Ryzen 7 1700, 3.60GHz

- BOINC-Statistiken

- Folding@Home-Statistiken

- Details zu meinem Desktop

- Prozessor

- Ryzen 9 3900X, 4,1Ghz All Core VID 1.13

- Mainboard

- ASUS ROG Strix B550-E Gaming

- Kühlung

- Thermalright Le Grand Macho RT

- Speicher

- Gskill F4-3600C16-8GTZNC -> 4*8 GB 3733Mhz (16-19-19-19-35)

- Grafikprozessor

- 5700XT Nitro+

- Display

- LG UltraGear 27GL850-B

- SSD

- Samsung 970 NVMe 1 TB

- HDD

- Western Digital Blue 4TB + 500 Samsung

- Optisches Laufwerk

- gehören der Vergangenheit an.

- Soundkarte

- Onboard

- Gehäuse

- bequite! PURE BASE 500

- Netzteil

- Enermax Revolution87+ 550 W GOLD -> Thx p3d

- Betriebssystem

- Windows X

- Webbrowser

- Chrome, Firefox

- Verschiedenes

- MEHR POWER ^^

- Internetanbindung

- ▼600 ▲50

Wenn mein Dreisatz stimmt:

346*32/45=246mm²

Ja so hätte ich auch gerechnet

aber irgendwie denke ich das es noch faktoren gibt die eine eins zu eins umrechnung nicht so ohne weiteres ermöglichen.

aber irgendwie denke ich das es noch faktoren gibt die eine eins zu eins umrechnung nicht so ohne weiteres ermöglichen.

Zuletzt bearbeitet:

gruffi

Grand Admiral Special

- Mitglied seit

- 08.03.2008

- Beiträge

- 5.393

- Renomée

- 65

- Standort

- vorhanden

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 5 1600

- Mainboard

- MSI B350M PRO-VDH

- Kühlung

- Wraith Spire

- Speicher

- 2x 8 GB DDR4-2400 CL16

- Grafikprozessor

- XFX Radeon R7 260X

- Display

- LG W2361

- SSD

- Crucial CT250BX100SSD1

- HDD

- Toshiba DT01ACA200

- Optisches Laufwerk

- LG Blu-Ray-Brenner BH16NS40

- Soundkarte

- Realtek HD Audio

- Gehäuse

- Sharkoon MA-I1000

- Netzteil

- be quiet! Pure Power 9 350W

- Betriebssystem

- Windows 10 Professional 64-bit

- Webbrowser

- Mozilla Firefox

- Verschiedenes

- https://valid.x86.fr/mb4f0j

Da Flächen immer noch zweidimensional sind, müsste es schon 346*32²/45² heissen. Da die Verkleinerung aber sowieso nicht linear ist, ist das recht theoretisch. Ausgehend von Shanghai und Llano Kern käme man auf folgendes:

346 / 15,3 * 9,7 = ~220 mm²

346 / 15,3 * 9,7 = ~220 mm²

Onkel_Dithmeyer

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 22.04.2008

- Beiträge

- 12.943

- Renomée

- 4.014

- Standort

- Zlavti

- Aktuelle Projekte

- Universe@home

- Lieblingsprojekt

- Universe@home

- Meine Systeme

- cd0726792825f6f563c8fc4afd8a10b9

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- Ryzen 9 3900X @4000 MHz//1,15V

- Mainboard

- MSI X370 XPOWER GAMING TITANIUM

- Kühlung

- Custom Wasserkühlung vom So. G34

- Speicher

- 4x8 GB @ 3000 MHz

- Grafikprozessor

- Radeon R9 Nano

- Display

- HP ZR30W & HP LP3065

- SSD

- 2 TB ADATA

- Optisches Laufwerk

- LG

- Soundkarte

- Im Headset

- Gehäuse

- Xigmatek

- Netzteil

- BeQuiet Dark Pro 9

- Tastatur

- GSkill KM570

- Maus

- GSkill MX780

- Betriebssystem

- Ubuntu 20.04

- Webbrowser

- Firefox Version 94715469

- Internetanbindung

- ▼100 Mbit ▲5 Mbit

Ja so hätte ich auch gerechnet. Allerdings bezweifel ich irgendwie das sich das einfach 1 zu 1 umrechnen lässt

War auch nicht gaaaanz ernst gemein

Da Flächen immer noch zweidimensional sind, müsste es schon 346*32²/45² heissen. Da die Verkleinerung aber sowieso nicht linear ist, ist das recht theoretisch. Ausgehend von Shanghai und Llano Kern käme man auf folgendes:

346 / 15,3 * 9,7 = ~220 mm²

Klingt logischer, aber ich hab mir mal andere Shrinkgrößen angeguckt, die Wahrheit dürfte irgendwo zwischen unseren Ergebnissen liegen ^^

Zuletzt bearbeitet:

nazgul99

Grand Admiral Special

- Mitglied seit

- 01.05.2005

- Beiträge

- 3.592

- Renomée

- 224

- Standort

- Irgendwo in der Nähe

- Mein Laptop

- ThinkPad Edge E145 / 8GB / M500 480GB / Kubuntu /// Asus U38N / 6GB / Matt / Postville / Kubuntu/W8

- Details zu meinem Desktop

- Prozessor

- AMD A10-7800

- Mainboard

- MSI A88XI AC

- Kühlung

- Scythe Shuriken Rev.2

- Speicher

- 2x 8GB DDR3-2133

- Grafikprozessor

- IGP

- Display

- HP LP2465, MVA, 1920x1200, 24"

- SSD

- Samsung 850 EVO 500GB

- HDD

- ST9500325AS 500GB

- Optisches Laufwerk

- ja, so'n USB-Dings

- Soundkarte

- onboard, optisch -> SMSL Q5 PRO -> ELAC EL60

- Gehäuse

- Silverstone ML06B

- Netzteil

- SST-ST30SF

- Betriebssystem

- Kubuntu

- Webbrowser

- Firefox

- Verschiedenes

- Synology DS414slim 3x 1,5 TB RAID5

Flächen rechnet man exponetiell fester Exponent, also quadratisch:

346mm² * 32² 45² = 174mm²,

Ein Full-Node ist immer 1/Wurzel-2 der alten Strukturgröße, in der Fläche macht das (theoretisch) genau 1/2 [ 1 / (Wurzel-2)² ].

Das wäre (obiges Beispiel knapp über) die Hälfte. Besonders wegen der Bump-Areas, die von der Bump-Technik abhängen und nur bei Verbesserungen in dem Bereich schrumpfen, ist dort schonmal deutlich weniger zu erwarten, die Transistoren schrumpfen aber ebenfalls erfahrungsgemäß nicht 1:2 zum Prozess. Ich werf mal nen Pfeil und der landet bei 200mm²

346mm² * 32² 45² = 174mm²,

Ein Full-Node ist immer 1/Wurzel-2 der alten Strukturgröße, in der Fläche macht das (theoretisch) genau 1/2 [ 1 / (Wurzel-2)² ].

Das wäre (obiges Beispiel knapp über) die Hälfte. Besonders wegen der Bump-Areas, die von der Bump-Technik abhängen und nur bei Verbesserungen in dem Bereich schrumpfen, ist dort schonmal deutlich weniger zu erwarten, die Transistoren schrumpfen aber ebenfalls erfahrungsgemäß nicht 1:2 zum Prozess. Ich werf mal nen Pfeil und der landet bei 200mm²

Onkel_Dithmeyer

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 22.04.2008

- Beiträge

- 12.943

- Renomée

- 4.014

- Standort

- Zlavti

- Aktuelle Projekte

- Universe@home

- Lieblingsprojekt

- Universe@home

- Meine Systeme

- cd0726792825f6f563c8fc4afd8a10b9

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- Ryzen 9 3900X @4000 MHz//1,15V

- Mainboard

- MSI X370 XPOWER GAMING TITANIUM

- Kühlung

- Custom Wasserkühlung vom So. G34

- Speicher

- 4x8 GB @ 3000 MHz

- Grafikprozessor

- Radeon R9 Nano

- Display

- HP ZR30W & HP LP3065

- SSD

- 2 TB ADATA

- Optisches Laufwerk

- LG

- Soundkarte

- Im Headset

- Gehäuse

- Xigmatek

- Netzteil

- BeQuiet Dark Pro 9

- Tastatur

- GSkill KM570

- Maus

- GSkill MX780

- Betriebssystem

- Ubuntu 20.04

- Webbrowser

- Firefox Version 94715469

- Internetanbindung

- ▼100 Mbit ▲5 Mbit

Stimmt, das sind ja mm² -.-

Manchmal wunder ich mich, wie ich durch meinen Physik-LK gekommen bin

Manchmal wunder ich mich, wie ich durch meinen Physik-LK gekommen bin

denjo

Grand Admiral Special

- Mitglied seit

- 28.12.2005

- Beiträge

- 3.746

- Renomée

- 116

- Standort

- Kellinghusen

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- PDM <--- sowas gabs mal :(

- Lieblingsprojekt

- all

- Meine Systeme

- Ryzen 7 1700, 3.60GHz

- BOINC-Statistiken

- Folding@Home-Statistiken

- Details zu meinem Desktop

- Prozessor

- Ryzen 9 3900X, 4,1Ghz All Core VID 1.13

- Mainboard

- ASUS ROG Strix B550-E Gaming

- Kühlung

- Thermalright Le Grand Macho RT

- Speicher

- Gskill F4-3600C16-8GTZNC -> 4*8 GB 3733Mhz (16-19-19-19-35)

- Grafikprozessor

- 5700XT Nitro+

- Display

- LG UltraGear 27GL850-B

- SSD

- Samsung 970 NVMe 1 TB

- HDD

- Western Digital Blue 4TB + 500 Samsung

- Optisches Laufwerk

- gehören der Vergangenheit an.

- Soundkarte

- Onboard

- Gehäuse

- bequite! PURE BASE 500

- Netzteil

- Enermax Revolution87+ 550 W GOLD -> Thx p3d

- Betriebssystem

- Windows X

- Webbrowser

- Chrome, Firefox

- Verschiedenes

- MEHR POWER ^^

- Internetanbindung

- ▼600 ▲50

Stimmt, das sind ja mm² -.-

Manchmal wunder ich mich, wie ich durch meinen Physik-LK gekommen bin

Ich erinnere mich da böse an plagiierte Formeln auf der Rückseite eines Taschenrechners

Dann wäre BD ca. 1/3 größer als ein thuban@32nm.

- Status

- Für weitere Antworten geschlossen.

Ähnliche Themen

- Antworten

- 96

- Aufrufe

- 9K

- Antworten

- 102

- Aufrufe

- 11K

- Antworten

- 6

- Aufrufe

- 1K