App installieren

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: This feature may not be available in some browsers.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Spekulationen zu aktuellen und zukünftigen Prozessen bei GlobalFoundries (<= 32nm)

- Ersteller Lynxeye

- Erstellt am

OBrian

Moderation MBDB, ,

- Mitglied seit

- 16.10.2000

- Beiträge

- 17.032

- Renomée

- 267

- Standort

- NRW

- Details zu meinem Desktop

- Prozessor

- Phenom II X4 940 BE, C2-Stepping (undervolted)

- Mainboard

- Gigabyte GA-MA69G-S3H (BIOS F7)

- Kühlung

- Noctua NH-U12F

- Speicher

- 4 GB DDR2-800 ADATA/OCZ

- Grafikprozessor

- Radeon HD 5850

- Display

- NEC MultiSync 24WMGX³

- SSD

- Samsung 840 Evo 256 GB

- HDD

- WD Caviar Green 2 TB (WD20EARX)

- Optisches Laufwerk

- Samsung SH-S183L

- Soundkarte

- Creative X-Fi EM mit YouP-PAX-Treibern, Headset: Sennheiser PC350

- Gehäuse

- Coolermaster Stacker, 120mm-Lüfter ersetzt durch Scythe S-Flex, zusätzliche Staubfilter

- Netzteil

- BeQuiet 500W PCGH-Edition

- Betriebssystem

- Windows 7 x64

- Webbrowser

- Firefox

- Verschiedenes

- Tastatur: Zowie Celeritas Caseking-Mod (weiße Tasten)

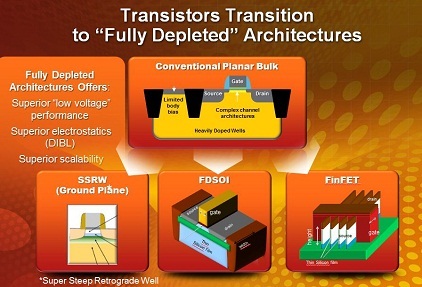

Mal dumm gefragt: Erfordert fdSOI überhaupt SOI-Wafer, oder baut man die SOI-Schicht erst bei der Produktion im Bereich des Transistors auf? Wenn letzteres, dann würde das erklären, warum einerseits Soitec rumweint und andererseits GF und ST so darauf herumreiten, wie ähnlich fdSOI doch zu bulk wäre (wobei das auch nur so sein kann, weil man angesichts gesunkener AMD-Waferkäufe neue Kunden gewinnen will, die bisher immer auf bulk waren).

Opteron

Redaktion

☆☆☆☆☆☆

Ja das braucht SOI-Wafer, mit ner hauchzarten SOI-Schicht drauf. Das ist auch der Grund, weswegen man Masken spart, da man bei bulk für die Isolationsschicht extra was Ätzen muss, was man sich bei SOI sparen kann.Mal dumm gefragt: Erfordert fdSOI überhaupt SOI-Wafer, oder baut man die SOI-Schicht erst bei der Produktion im Bereich des Transistors auf?

Ne Übersicht über die Produkte und SOI-Schichtdicke gibts hier bei Soitec:

http://www.soitec.com/en/products-and-services/microelectronics/fd-2d/

FD-2D ist das "normale" zweidimensionale FD-SOI über das wir hier reden, FD-3D ist FD-SOI mit Finfets.

ONH

Grand Admiral Special

nüchtern betrachtet spricht nachwievor der negative Soitec-Ausblick dagegen

Wieso? Soitec hat sich doch nur auf max 3q hinaus geäussert, womit man die Aussage nicht auf AMDs 28nm Produkte beziehen, wenn die erst irgendwann im 2 - 3q 2014 Herauskommen. Kann aber auch sein das ich da die PM Falsch verstanden habe. ein weiterer Ausblick macht auch kein Sinn wenn man AMD anschaut niemand sagt was wie kommen soll.

Opteron

Redaktion

☆☆☆☆☆☆

Naja, aber wenn AMD das Anfang 2014 verkaufen möchte, sollten sie schon Mitte 2013 zum produzieren anfangen. Das läge noch innerhalb der 3Quartale. Außerdem ist die Frage, wielange man seine SOI-Wafer-Bestellung im vorraus tätigen muss. Keine Ahnung, wie lange es dauert nen FD-SOI-Wafer zu fabrizieren. Aber so ein ~halbes Jahr kann ich mir schon vorstellen. Falls es jemand weiss bitte bescheid geben.Wieso? Soitec hat sich doch nur auf max 3q hinaus geäussert, womit man die Aussage nicht auf AMDs 28nm Produkte beziehen, wenn die erst irgendwann im 2 - 3q 2014 Herauskommen. Kann aber auch sein das ich da die PM Falsch verstanden habe. ein weiterer Ausblick macht auch kein Sinn wenn man AMD anschaut niemand sagt was wie kommen soll.

Ansonsten, die FOlien vom SOI Treffen sind online:

http://www.soiconsortium.org/corners/fully-depleted-soi/december-2012/

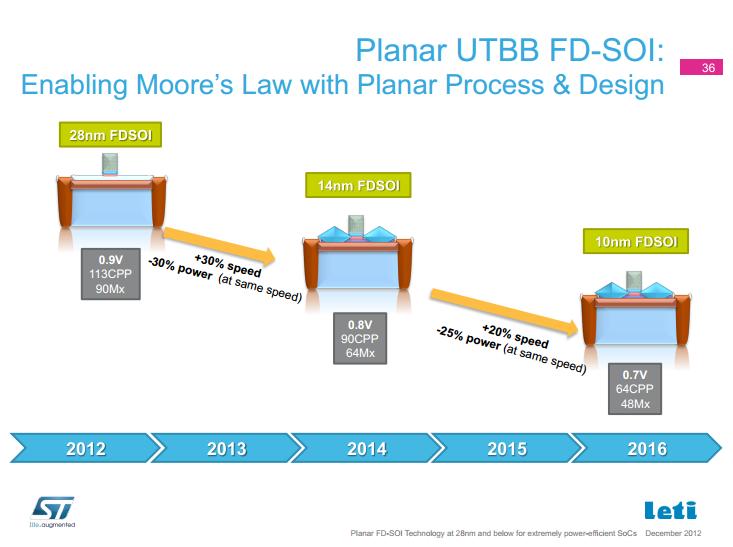

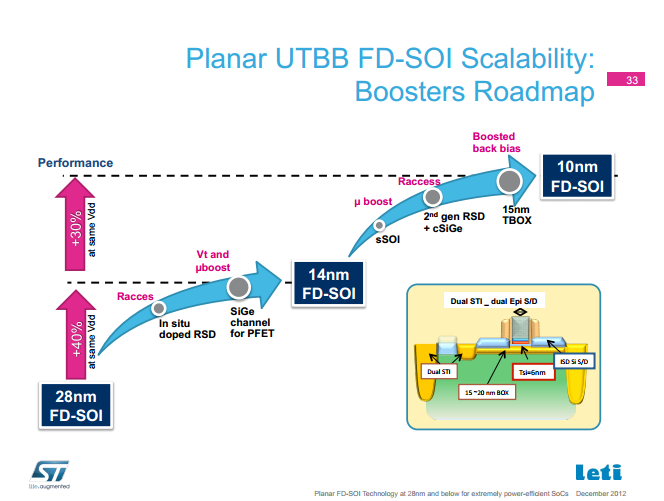

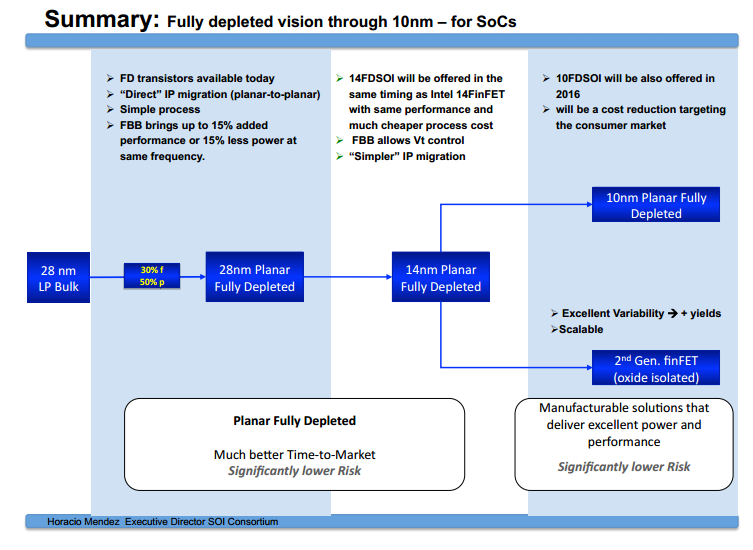

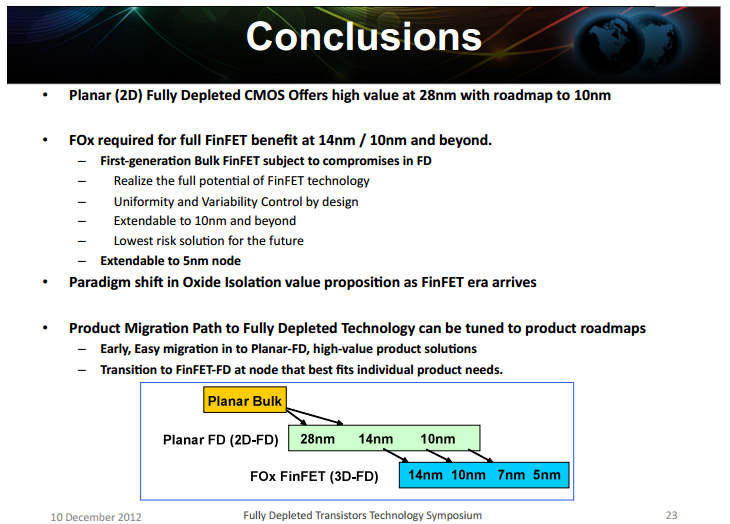

Alles ganz interessant, gab auch ne neue Roadmap:

Na was fällt auf? 20nm sind gestrichen. Jetzt ist die Preisfrage, ob GF den 14nm FD-SOI Prozess auch bekommt. Die meinten letztens ja irgendwo, dass der 14XM Prozess garantiert bulk wäre.

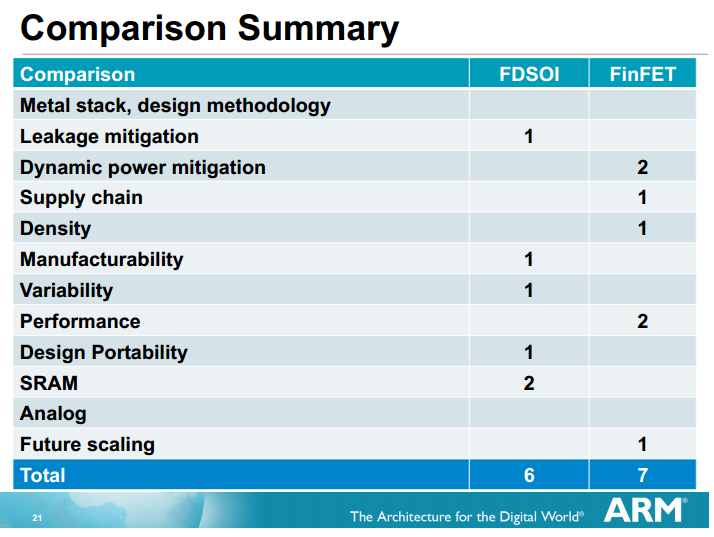

Interessant ist auch die unabhängige Einschätzung der FD-SOI vs. Finfet Geschichte von nem ARM Ingenieur. Das geht seiner Meinung nach leicht pro Finfet aus:

Aber wie unsicher er sich ist, sieht man daran, dass er auch das Publikum fragt. Was da rausgekommen ist, wissen wir leider nicht. Ein Punkt fällt mir aber ein, den er anscheinend vergessen hat, die Kosten. Finfet soll da ja deutlich teurer sein als FD-SOI. Das Thema hatten wir ja gerade mit den Masken.

Bin jetzt mal gespannt, ob GF und TSMC 20nm nicht auch streichen ^^

GF schießt nach nem Jahr ja sowieso schon 14XM nach und 20nm bulk bringt nicht viele Vorteile und ist nur teuer, außerdem soll 28nm lange halten...

LoRDxRaVeN

Grand Admiral Special

- Mitglied seit

- 20.01.2009

- Beiträge

- 4.169

- Renomée

- 64

- Standort

- Oberösterreich - Studium in Wien

- Mein Laptop

- Lenovo Thinkpad Edge 11

- Details zu meinem Desktop

- Prozessor

- Phenom II X4 955 C3

- Mainboard

- Gigabyte GA-MA790X-DS4

- Kühlung

- Xigmatek Thor's Hammer + Enermax Twister Lüfter

- Speicher

- 4 x 1GB DDR2-800 Samsung

- Grafikprozessor

- Sapphire HD4870 512MB mit Referenzkühler

- Display

- 22'' Samung SyncMaster 2233BW 1680x1050

- HDD

- Hitachi Deskstar 250GB, Western Digital Caviar Green EADS 1TB

- Optisches Laufwerk

- Plextor PX-130A, Plextor Px-716SA

- Soundkarte

- onboard

- Gehäuse

- Aspire

- Netzteil

- Enermax PRO82+ II 425W ATX 2.3

- Betriebssystem

- Windows 7 Professional Studentenversion

- Webbrowser

- Firefox siebenunddreißigsttausend

- Schau Dir das System auf sysprofile.de an

Inwiefern interpretierst du den "Performance"-Begriff auf der letzten Folie? Da sieht ja FDSOI u.A. eher mager aus bei seiner Einschätzung

Mal dumm gefragt: Erfordert fdSOI überhaupt SOI-Wafer, oder baut man die SOI-Schicht erst bei der Produktion im Bereich des Transistors auf?

Das SOI ist ein genau ausgerichtete Schicht einkristallines Silizium auf dem Oxid. Das kann man nicht hinterher wachsen lassen. Woher soll das ankommende Silizium "wissen", wie es aufwachsen soll?

Für die Transistoren ist es ganz entscheidend in welche (Kristall-)Richtung der Strom fliesst. Die Beweglichkeiten sind stark richtungsabhängig.

Ganz zu schweigen, das auch der Epitaxyprozess für die Silizium-Germanium-Technik um Stress zu erzeugen, eine einheitliche Grundlage braucht.

.

EDIT :

.

Falsch, die aktiven Gebiete müssen bei SOI genauso geätzt und mit Oxid aufgefüllt werden.Das ist auch der Grund, weswegen man Masken spart, da man bei bulk für die Isolationsschicht extra was Ätzen muss, was man sich bei SOI sparen kann.

Woerns

Grand Admiral Special

- Mitglied seit

- 05.02.2003

- Beiträge

- 2.983

- Renomée

- 232

Hm, 20nm fdSOI ist gestrichen?

Soweit ich weiß, sollte 20nm fdSOI gate-last werden.

Insofern würde er keinen grußen Flächenvorteil gegnüber 28nm mit gate-first haben und wurde deshalb vielleicht nicht akzeptiert.

Aber das will ich erst mal in Granit gemeißelt sehen. Da reicht mir die eine Folie als Grundlage nicht. Wer weiß schon, was der entsprechende Praktikant am Vorabend getrieben hat?

MfG

.

EDIT :

.

Es mehren sich die Hinweise, dass 20nm SOI gestrichen wurde.

MfG

.

EDIT :

.

Allerdings sind die fdSOI FinFets anscheinend von 14nm auf 10nm verschoben worden

MfG

.

EDIT :

.

Hier noch ein Link, was Globalfoundries anbieten will.

Habs selbst noch nicht lesen können und komme auch gerade nicht dazu, mich zu vertiefen.

MfG

Soweit ich weiß, sollte 20nm fdSOI gate-last werden.

Insofern würde er keinen grußen Flächenvorteil gegnüber 28nm mit gate-first haben und wurde deshalb vielleicht nicht akzeptiert.

Aber das will ich erst mal in Granit gemeißelt sehen. Da reicht mir die eine Folie als Grundlage nicht. Wer weiß schon, was der entsprechende Praktikant am Vorabend getrieben hat?

MfG

.

EDIT :

.

Es mehren sich die Hinweise, dass 20nm SOI gestrichen wurde.

MfG

.

EDIT :

.

Allerdings sind die fdSOI FinFets anscheinend von 14nm auf 10nm verschoben worden

MfG

.

EDIT :

.

Hier noch ein Link, was Globalfoundries anbieten will.

Habs selbst noch nicht lesen können und komme auch gerade nicht dazu, mich zu vertiefen.

MfG

Ja, es sieht eher so aus, dass 20nm durch 14nm FDSOI ersetzt wurde, wenn der tatsächlich schon 2014 kommen soll. Oder hat man den Prozess schlicht umbenannt....?

Zumindest lässt das darauf schließen:

Komische Sache das. Marketing im Foundry Business, irgendwie ulkig.

Zumindest lässt das darauf schließen:

(link von Woerns)The implication is that parties interested in the FDSOI roadmap are renaming what was the 20-nm node so they can be seen to be at an equivalent node to Intel 14-nm FinFET process and FinFET processes from foundries such as Taiwan Semiconductor Manufacturing Co. Ltd. and Globalfoundries.

Komische Sache das. Marketing im Foundry Business, irgendwie ulkig.

Opteron

Redaktion

☆☆☆☆☆☆

Aber mit FD-SOI spart man doch Masken und Masken braucht man nur zum Ätzen, oder nicht?Falsch, die aktiven Gebiete müssen bei SOI genauso geätzt und mit Oxid aufgefüllt werden.

So stehts da...2014 wollen die schon 14nm FDSOI fertigen?

Na da gabs noch zwei weitere Folie. Eine aus dem gleichen Vortrag, nur ausführlicher, und eine von Horacio Mendez (Executive Director at SOI consortium)Hm, 20nm fdSOI ist gestrichen?

Soweit ich weiß, sollte 20nm fdSOI gate-last werden.

Insofern würde er keinen grußen Flächenvorteil gegnüber 28nm mit gate-first haben und wurde deshalb vielleicht nicht akzeptiert.

Aber das will ich erst mal in Granit gemeißelt sehen. Da reicht mir die eine Folie als Grundlage nicht. Wer weiß schon, was der entsprechende Praktikant am Vorabend getrieben hat?

Die Erste:

Die Zweite:

Ich glaub das kann man wählen, gibt noch ne 3. Roadmap vom IBM Beitrag:Allerdings sind die fdSOI FinFets anscheinend von 14nm auf 10nm verschoben worden

GF geht nach dem Artikel auch auf 10nm Finfet in 2015.Hier noch ein Link, was Globalfoundries anbieten will.

Habs selbst noch nicht lesen können und komme auch gerade nicht dazu, mich zu vertiefen.

Überraschung ist SSRW( super-steep retrograde well), dass sie auch noch anbieten wollen, neben bulk planar, fully depleted silicon-on-insulator (minimum), fully depleted silicon-on-insulator (maximum) und finFET.

Aja und es wird 2 FD-SOI Prozesse geben:

Maximum ist also stark getunt und minimum ist schlampig von bulk portiert, oder wie muss man das verstehen? Naja, wär dann sicherlich billig, wäre was für AMD.As part of its technology offerings, GlobalFoundries plans to offer two versions of FD-SOI: minimum and maximum. The maximum version is a technology tuned for a specific application. IBM and STMicroelectronics are examples of companies that would utilize maximum versions of FD-SOI. Meanwhile, the minimum version is a simple and an “out of the box” FD-SOI technology, said Subramani Kengeri, head of advanced technology architecture at GlobalFoundries.

Aja und lustige Bemerkung am Rande, der GF-Chef hat auch den anderen Fundry-Chef widersprochen, die meinten dass das klassische Auftragsfertigergeschäft tod wäre, da die Chip-Hersteller enger mit den Chip-Designern kooperieren müssten, da die Probleme immer komplexer und teurer werden. Gut das AMD seine Chipfertigung nicht ausgeglieder hat

Frag mich nur, ob der GF Chef deshalb dem Standpunkt der anderen widersprecht, oder ob seine Argumente valide sind, hab sie noch nicht so genau angeschaut.

P.S: Wieso ist die GF-HP eigentlich so schlecht ... der Chef hält ne Presentation mit ner neuen Roadmap, und nirgends gibts die ...

Edit2:

Ahhh eetimes sei dank:

http://www.rfdesignline.com/electro...dead--just-evolving-says-Globalfoundries-CEO-

(Achtung, hat 2 Seiten)

GF streicht also die 20nm nicht. Wundert mich jetzt aber auch nicht mehr, der 14xm Prozess verwendet ja BEOL vom 20nm Prozess, das ginge schlecht ohne ^^

Bei der Riesenauswahl war die Entscheidung von AMD aber auch richtig, dass sie keinen Spezialprozess mehr brauchen, einer der 4-5 Versionen wird ja wohl ihren Geschmack treffen *G*

XBitLabs: AMD: We Would Like to Use Process Technologies for Longer Periods of Time

AMD möchte also das Erfolgsmodell von Ontario/Zacate ausweiten und zukünftig den fertigen Brei mehrmals aufkochen, i.e. die Produktionsprozesse länger nutzen als bisher.

Das deutet wiederum in Richtung Mainstream- und Embedded-Produkte (passt also zur kommunizierten Strategie) und Verabschiedung aus dem LeadingEdge- und damit HighEnd-Bereich. Es bedeutet mMn letztlich aber auch, AMD setzt tatsächlich auf "gut genug aber wenigstens billig und zuverlässig". Das Modell fährt z.B. Nvidia ja auch recht erfolgreich mit dem Tegra3, der wie Ontario noch auf 40nm setzt.

Was zunächst gut aussieht, wenn man auf Ontario schaut, funktioniert wohl nur in einem kleinen Markt-Bereich; nämlich da, wo Intel aufgrund möglicherweise schwindender Margen nicht mitspielen will. Das wiederum heißt, AMD gerät insgesamt noch stärker unter Druck, weil man in die Masse gehen muss, um die sinkenden Margen aufzufangen. Aber auch hier macht das Modell Sinn, denn bei eingefahrenen Prozessen stehen die Kapazitäten leichter zur Verfügung als bei top-aktuellen.

AMD möchte also das Erfolgsmodell von Ontario/Zacate ausweiten und zukünftig den fertigen Brei mehrmals aufkochen, i.e. die Produktionsprozesse länger nutzen als bisher.

Das deutet wiederum in Richtung Mainstream- und Embedded-Produkte (passt also zur kommunizierten Strategie) und Verabschiedung aus dem LeadingEdge- und damit HighEnd-Bereich. Es bedeutet mMn letztlich aber auch, AMD setzt tatsächlich auf "gut genug aber wenigstens billig und zuverlässig". Das Modell fährt z.B. Nvidia ja auch recht erfolgreich mit dem Tegra3, der wie Ontario noch auf 40nm setzt.

Was zunächst gut aussieht, wenn man auf Ontario schaut, funktioniert wohl nur in einem kleinen Markt-Bereich; nämlich da, wo Intel aufgrund möglicherweise schwindender Margen nicht mitspielen will. Das wiederum heißt, AMD gerät insgesamt noch stärker unter Druck, weil man in die Masse gehen muss, um die sinkenden Margen aufzufangen. Aber auch hier macht das Modell Sinn, denn bei eingefahrenen Prozessen stehen die Kapazitäten leichter zur Verfügung als bei top-aktuellen.

Zuletzt bearbeitet:

Opteron

Redaktion

☆☆☆☆☆☆

Naja, sagen wirs deutlich, das geht nur dann, wenn man die bessere Architektur hat. Jaguar ist schön und gut, aber Bulldozer ..Was zunächst gut aussieht, wenn man auf Ontario schaut, funktioniert wohl nur in einem kleinen Markt-Bereich; nämlich da, wo Intel aufgrund möglicherweise schwindender Margen nicht mitspielen will.

Edit: Ach, das war übrigens der Vortrag, den ich hier unter "Podiumsdiskussion" meinte:

http://www.planet3dnow.de/vbulletin/showthread.php?p=4704201#post4704201

Das Thema kam mir doch gleich so bekannt vor ^^

Markus Everson

Grand Admiral Special

Lest ihr eigentlich die Infos zum FD-SoI Prozess? Gegenüber 28nm bulk bietet FD-SoI 28nm entweder 30% höhere Taktraten bei gleichem Verbrauch oder bis zu 50% niedrigeren Verbrauch bei gleicher Taktrate, je nachdem auf was man ihn trimmt

Wie soll man diese Frage beantworten ohne auch die Fertigungskosten zu kennen? Ein Steamroller der weniger kostet und weniger oder ebensowenig wie sein Konkurrent kostet wäre mir als Aktionär durchaus recht. Die Wilde Horde (*) der Übertakter und Extremgamer mag das gerne anders sehen.

(*) es sind nur Einhundert - aber sie kreischen und zetern als wären es Tausende

.

EDIT :

.

Ich biete einen 4Ghz Steamroller mit +30% IPC gegenüber Vishera und 768 GCN 3.0 Shadern als APU für Sockel FM3 (DDR4) im ersten Quartal 2014 - Wer bietet mehr?

Vielleicht sollten wir BR bitten uns die Kosten pro Die auszurechnen bevor wir entscheiden ob wir auf 4,5 GHz gehen?

BavarianRealist

Grand Admiral Special

- Mitglied seit

- 06.02.2010

- Beiträge

- 3.358

- Renomée

- 80

...Vielleicht sollten wir BR bitten uns die Kosten pro Die auszurechnen bevor wir entscheiden ob wir auf 4,5 GHz gehen?

Wenn BD keine deutlich bessere Leistung erreichen wird, ist die Antwort einfach: die Kosten werden dann für den zu erzielenden Erlöse weiterhin schlichtweg zu hoch sein. Die GM würde dann tendenziell eher noch schlechter ausfallen als sie eh schon ist. Geringere Wafer-Zahlen machen die Rechnung eher noch schlechter...

Opteron

Redaktion

☆☆☆☆☆☆

Das ist ja gerade der Witz an der Sache, in jedem Paper steht, dass es billiger ist, da die Yields anfangs höher wären und man weniger Masken bräuchte ...Wie soll man diese Frage beantworten ohne auch die Fertigungskosten zu kennen? Ein Steamroller der weniger kostet und weniger oder ebensowenig wie sein Konkurrent kostet wäre mir als Aktionär durchaus recht. Die Wilde Horde (*) der Übertakter und Extremgamer mag das gerne anders sehen.

Das sollte die Aktionäre ja interessieren, v.a. aht RRead ja erst was von " Zahl der Masken verringern" erzählt. Das würde gut passen. Könnte aber eben auch sein, dass er das einfach so meint, dass AMD in Zukunft nur noch Billigteile mit Jaguar herstellt

Apropos .. .wieviel Metalllagen hat Kabini eigentlich, gabs da schon Zahlen? Mal bei Ontario schauen. Edit: 10 Lagen für Hondo: http://www.planet3dnow.de/vbulletin/showthread.php?p=4675385#post4675385

Wink mit dem Zaunpfahl, dass der Standort Dresden ein Auslaufmodell ist.

http://www.theregister.co.uk/2012/12/14/ajit_manocha_on_eu_competitiveness/

http://www.theregister.co.uk/2012/12/14/ajit_manocha_on_eu_competitiveness/

Markus Everson

Grand Admiral Special

Ich lese da nur die Forderung nach mehr Subvention. Das übliche Spiel.

Aber mit FD-SOI spart man doch Masken und Masken braucht man nur zum Ätzen, oder nicht?

Naja mindestens die Hälfte geht für Implants/Dotierung drauf.

Du hast ja mind. 3 Implantschritte.1. Wannen 2. Extension und Halos. 3. die S/D Gebiete.

Mit SOI spart man nur bei den Wannen.

Woerns

Grand Admiral Special

- Mitglied seit

- 05.02.2003

- Beiträge

- 2.983

- Renomée

- 232

Es wird kolportiert, dass sich Altera möglicherweise für fdSOI interessiert. Vielleicht stehen lediglich Verhandlungen mit TSMC dahinter.

MfG

MfG

dekaisi

Grand Admiral Special

- Mitglied seit

- 06.11.2006

- Beiträge

- 3.929

- Renomée

- 25

- Standort

- B

- Mein Laptop

- Lenovo Y50-70,32GB Ram, Samsung 830Pro 256GB, Panel Upgrade,...

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 3950X

- Mainboard

- ROG Strix X570-E

- Kühlung

- Corsair H115i Platinium

- Speicher

- 4x G.Skill F4-3600C15-8GTZ (B-Die)

- Grafikprozessor

- MSI Trio X 3090

- Display

- Predator X27, Asus MQ270Q

- SSD

- sehr viele :D

- HDD

- viele viele und extra Platz :D

- Optisches Laufwerk

- LG Bluray BH10LS30

- Soundkarte

- Soundblaster X7, Steinberg UR-22C

- Gehäuse

- Corsair Vengeance v70 +Dämmung

- Netzteil

- Enermax Platimax D.F. 600W

- Tastatur

- Corsair RGB Platinum K95

- Maus

- Asus ROG Pugio

- Betriebssystem

- Win10 Prof Workstation

Ich lese da nur die Forderung nach mehr Subvention. Das übliche Spiel.

Ich denke aber z.B. aus dem SAB hat erst 2012 wieder gespendet und ihre Gelder sind verbraucht. Da müssten Geld schon aus anderen Topf kommen.

Aber der Buschfunk meldet, dass wohl DD nochmals erweitert werden soll.

Aber wie sieht es eigentlich in Fab8 aus?

Woerns

Grand Admiral Special

- Mitglied seit

- 05.02.2003

- Beiträge

- 2.983

- Renomée

- 232

etwas OT:

heise berichtet, dass TSMC in New York, eventuell Malta, ein Werk errichten will, um Chips für Apple zu produzieren. Zunächst aber würde TSMC A6X Chips für das aktuelle iPAD produzieren.

Interessant daran ist, dass kürzlich der für Malta zuständige Governour in Taipeh war, um TSMC an der Teilnahme der 450mm Entwicklung in New York zu gewinnen. TSMC hatte abgewunken.

MfG

heise berichtet, dass TSMC in New York, eventuell Malta, ein Werk errichten will, um Chips für Apple zu produzieren. Zunächst aber würde TSMC A6X Chips für das aktuelle iPAD produzieren.

Interessant daran ist, dass kürzlich der für Malta zuständige Governour in Taipeh war, um TSMC an der Teilnahme der 450mm Entwicklung in New York zu gewinnen. TSMC hatte abgewunken.

MfG

nVoodoo

Vice Admiral Special

- Mitglied seit

- 16.03.2007

- Beiträge

- 531

- Renomée

- 1

- Standort

- Nördliches Emsland

- Meine Systeme

- R7 1700;2xX5650;i7 4700MQ;2x E5430;Athlon 5350

- BOINC-Statistiken

Das ist ja gerade der Witz an der Sache, in jedem Paper steht, dass es billiger ist, da die Yields anfangs höher wären und man weniger Masken bräuchte ...

Das sollte die Aktionäre ja interessieren, v.a. aht RRead ja erst was von " Zahl der Masken verringern" erzählt. Das würde gut passen. Könnte aber eben auch sein, dass er das einfach so meint, dass AMD in Zukunft nur noch Billigteile mit Jaguar herstellt

http://www.planet3dnow.de/vbulletin/showthread.php?p=4675385#post4675385

Sind aber nicht die SOI-Wafer n gutes Stück teurer als normale "Bulk"-Wafer? Aber die Info schwirrt glaube ich scho seit der SOI Einführung herum...

Außerdem nützt es ja nichts wenn GF trotzdem mehr Geld für FD-SOI nimmt auch wenn es theoretisch günstiger herzustellen wäre...

Zuletzt bearbeitet:

Opteron

Redaktion

☆☆☆☆☆☆

Ja, aber das ist laut den SOI Leuten zu vernachlässigen. Für das bisschen Mehrkosten pro Wafer bekommt man laut deren Aussage nen Strauß Vorteile:Sind aber nicht die SOI-Wafer n gutes Stück teurer als normale "Bulk"-Wafer? Aber die Info schwirrt glaube ich scho seit der SOI Einführung herum...

- höhere Yields (also mehr gute Chips pro Wafer, was die Mehrkosten schon drückt)

- bessere Chipperformance -> die Chips lassen sich auch teurer verkaufen

- schnellere Produktion, d.h. man kann die Chips früher zu Geld machen, die Kapitalbindungsdauer ist geringer.

Wobei letztes Argument eher ein Vorteil für GF ist, die bekommen das Geld von AMD früher, da sie den Wafer früher ausliefern können. AMD hat aber auch den Vorteil der früheren "time to market", mit FD-SOI spart man halt ein paar Wochen ein, da könnte es ausnahmsweise mal passieren, dass Launch-Termine eingehalten werden

Hm, ja das könnte natürlich sein. Aber GF spart ja auch, es gibt weniger Prozessschritte. D.H. der Output einer Fab würde mit FD-SOI steigen. Wenn nicht nichts falsch verstanden habe.Außerdem nützt es ja nichts wenn GF trotzdem mehr Geld für FD-SOI nimmt auch wenn es theoretisch günstiger herzustellen wäre...

In dem Fall sollte an AMD nur die Mehrkosten von der Soitec Wafer weitergegeben werden, mehr nicht.

@Woerns:

Ja das geisterte schon länger durch die Presse, interessant vielleicht, dass sie in den USA suchen. Ist für TSMC das erste Mal außerhalb von Taiwan/China, oder?

Aber gut, mit Apple als Strippenzieher im Hintergrund eher nicht.

nVoodoo

Vice Admiral Special

- Mitglied seit

- 16.03.2007

- Beiträge

- 531

- Renomée

- 1

- Standort

- Nördliches Emsland

- Meine Systeme

- R7 1700;2xX5650;i7 4700MQ;2x E5430;Athlon 5350

- BOINC-Statistiken

Hm, ja das könnte natürlich sein. Aber GF spart ja auch, es gibt weniger Prozessschritte. D.H. der Output einer Fab würde mit FD-SOI steigen. Wenn nicht nichts falsch verstanden habe.

In dem Fall sollte an AMD nur die Mehrkosten von der Soitec Wafer weitergegeben werden, mehr nicht.

Aber GF verdient ja auch noch kein Geld also wird man sowieso versuchen die Margen zu erhöhen und FD-SOI wird doch warscheinlich sowieso nur in Dresden zu fertigen sein? Ein Produkt oder Verfahren was eindeutig Vorteile für den Kunden hat (Takt/Verbrauch z.B.) wird am Anfang niemals günstiger sein als ein standard 0815 Produkt/Verfahren.

Kann man denn die ganzen Anlagen einfach so von SOI auf BULK und umgekehrt switchen weil wenn in Dresden schon viel umgerüstet wurde und das zurückswitchen auf SOI wieder kompliziert ist kostet das ja auch Zeit(wäre der Vorteil schonmal wieder weg) und Geld...

Das wird sich GF auch alles bezahlen lassen... AMD kann ja eh nicht weg von GF wegen den Knebelverträgen und aktuellen Produktlage also interessiert es GF auch warscheinlich herzlich wenig ob AMD jetzt Bulk, SOI oder FD-SOI einsetzt.

Und von den Kapazitäten ist AMD glaube ich sowieso nicht mehr in der Lage Dresden auszulasten...

Ähnliche Themen

- Antworten

- 6

- Aufrufe

- 3K

- Antworten

- 22

- Aufrufe

- 4K

- Antworten

- 0

- Aufrufe

- 142K