App installieren

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: This feature may not be available in some browsers.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

AMD Zen - 14nm, 8 Kerne, 95W TDP & DDR4?

- Ersteller UNRUHEHERD

- Erstellt am

Dresdenboy

Redaktion

☆☆☆☆☆☆

Ohne festen Takt werden diese Vergleiche anhand normal veröffentlichter Benchmarks kompliziert. Dann taktet ein Kern dank 14 nm Prozess länger hoch, während der Prozessor mit 28 nm Herstellung eher wieder den Takt zurücknehmen muss.

gruffi

Grand Admiral Special

- Mitglied seit

- 08.03.2008

- Beiträge

- 5.393

- Renomée

- 65

- Standort

- vorhanden

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 5 1600

- Mainboard

- MSI B350M PRO-VDH

- Kühlung

- Wraith Spire

- Speicher

- 2x 8 GB DDR4-2400 CL16

- Grafikprozessor

- XFX Radeon R7 260X

- Display

- LG W2361

- SSD

- Crucial CT250BX100SSD1

- HDD

- Toshiba DT01ACA200

- Optisches Laufwerk

- LG Blu-Ray-Brenner BH16NS40

- Soundkarte

- Realtek HD Audio

- Gehäuse

- Sharkoon MA-I1000

- Netzteil

- be quiet! Pure Power 9 350W

- Betriebssystem

- Windows 10 Professional 64-bit

- Webbrowser

- Mozilla Firefox

- Verschiedenes

- https://valid.x86.fr/mb4f0j

Eher Haswell+.XV +40% ist ca. SB IPC.

OBrian

Moderation MBDB, ,

- Mitglied seit

- 16.10.2000

- Beiträge

- 17.032

- Renomée

- 267

- Standort

- NRW

- Details zu meinem Desktop

- Prozessor

- Phenom II X4 940 BE, C2-Stepping (undervolted)

- Mainboard

- Gigabyte GA-MA69G-S3H (BIOS F7)

- Kühlung

- Noctua NH-U12F

- Speicher

- 4 GB DDR2-800 ADATA/OCZ

- Grafikprozessor

- Radeon HD 5850

- Display

- NEC MultiSync 24WMGX³

- SSD

- Samsung 840 Evo 256 GB

- HDD

- WD Caviar Green 2 TB (WD20EARX)

- Optisches Laufwerk

- Samsung SH-S183L

- Soundkarte

- Creative X-Fi EM mit YouP-PAX-Treibern, Headset: Sennheiser PC350

- Gehäuse

- Coolermaster Stacker, 120mm-Lüfter ersetzt durch Scythe S-Flex, zusätzliche Staubfilter

- Netzteil

- BeQuiet 500W PCGH-Edition

- Betriebssystem

- Windows 7 x64

- Webbrowser

- Firefox

- Verschiedenes

- Tastatur: Zowie Celeritas Caseking-Mod (weiße Tasten)

Außerdem ist ja nicht nur die IPC entscheidend, sondern auch der Takt. Wenn die IPC sogar besser als die von Skylake (oder Nachfolger) sein sollte, aber Intel dann einige hundert MHz mehr drauflegen könnte, ohne daß aus der TDP-Klasse ausgebrochen wird, dann wäre AMD wieder hinten dran. Aber auch das wäre ja nicht schlimm für den Kunden, so gibt es wenigstens mal wieder mehr CPU-Leistung auf dem Markt, nach jahrelangem Stillstand. Intel darf ja ruhig vorne sein, sie müssen aber den heißen Atem der Konkurrenz im Nacken spüren

hoschi_tux

Grand Admiral Special

- Mitglied seit

- 08.03.2007

- Beiträge

- 4.761

- Renomée

- 286

- Standort

- Ilmenau

- Aktuelle Projekte

- Einstein@Home, Predictor@Home, QMC@Home, Rectilinear Crossing No., Seti@Home, Simap, Spinhenge, POEM

- Lieblingsprojekt

- Seti/Spinhenge

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen R9 5900X

- Mainboard

- ASUS TUF B450m Pro-Gaming

- Kühlung

- Noctua NH-U12P

- Speicher

- 2x 16GB Crucial Ballistix Sport LT DDR4-3200, CL16-18-18

- Grafikprozessor

- AMD Radeon RX 6900XT (Ref)

- Display

- LG W2600HP, 26", 1920x1200

- HDD

- Crucial M550 128GB, Crucial M550 512GB, Crucial MX500 2TB, WD7500BPKT

- Soundkarte

- onboard

- Gehäuse

- Cooler Master Silencio 352M

- Netzteil

- Antec TruePower Classic 550W

- Betriebssystem

- Gentoo 64Bit, Win 7 64Bit

- Webbrowser

- Firefox

Wenn die IPC sogar besser als die von Skylake (oder Nachfolger) sein sollte, aber Intel dann einige hundert MHz mehr drauflegen könnte, ohne daß aus der TDP-Klasse ausgebrochen wird, dann wäre AMD wieder hinten dran.

Schau dir den mal an: http://www.golem.de/news/xeon-e5-2602-v4-intel-plant-spezialprozessor-mit-5-1-ghz-1601-118583.html

4 Kerne (+4 SMT), 5,1GHz und 165W. Intel hat keinen Taktspielraum nach oben.

Onkel_Dithmeyer

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 22.04.2008

- Beiträge

- 12.943

- Renomée

- 4.014

- Standort

- Zlavti

- Aktuelle Projekte

- Universe@home

- Lieblingsprojekt

- Universe@home

- Meine Systeme

- cd0726792825f6f563c8fc4afd8a10b9

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- Ryzen 9 3900X @4000 MHz//1,15V

- Mainboard

- MSI X370 XPOWER GAMING TITANIUM

- Kühlung

- Custom Wasserkühlung vom So. G34

- Speicher

- 4x8 GB @ 3000 MHz

- Grafikprozessor

- Radeon R9 Nano

- Display

- HP ZR30W & HP LP3065

- SSD

- 2 TB ADATA

- Optisches Laufwerk

- LG

- Soundkarte

- Im Headset

- Gehäuse

- Xigmatek

- Netzteil

- BeQuiet Dark Pro 9

- Tastatur

- GSkill KM570

- Maus

- GSkill MX780

- Betriebssystem

- Ubuntu 20.04

- Webbrowser

- Firefox Version 94715469

- Internetanbindung

- ▼100 Mbit ▲5 Mbit

"Our Zen based CPU development is on track to achieve greater than 40% ITC uplift from our previous generation and we're on schedule to sample later this year."

"To sample" ist damit gemeint, dass Engeneering Samples verteilt werden, oder was genau?

Müssten Pressesample gemeint sein, die Eng-Samples sind schon viel früher vor einem Launch im Umlauf. Ich vermute einen Paperlaunch im Dezember.

BoMbY

Grand Admiral Special

- Mitglied seit

- 22.11.2001

- Beiträge

- 7.468

- Renomée

- 293

- Standort

- Aachen

- Details zu meinem Desktop

- Prozessor

- Ryzen 3700X

- Mainboard

- Gigabyte X570 Aorus Elite

- Kühlung

- Noctua NH-U12A

- Speicher

- 2x16 GB, G.Skill F4-3200C14D-32GVK @ 3600 16-16-16-32-48-1T

- Grafikprozessor

- RX 5700 XTX

- Display

- Samsung CHG70, 32", 2560x1440@144Hz, FreeSync2

- SSD

- AORUS NVMe Gen4 SSD 2TB, Samsung 960 EVO 1TB, Samsung 840 EVO 1TB, Samsung 850 EVO 512GB

- Optisches Laufwerk

- Sony BD-5300S-0B (eSATA)

- Gehäuse

- Phanteks Evolv ATX

- Netzteil

- Enermax Platimax D.F. 750W

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox

Lisa Su sagt laut Transkript "late in the year" und nicht "later this year".

http://seekingalpha.com/article/382...-results-earnings-call-transcript?part=single

EDIT

Im Audio ist ganz klar "late" zu hören: http://edge.media-server.com/m/p/wmuffn7g/lan/en

Naja, bis dahin war es jedenfalls immer "later", und nicht "late". Möglicherweise hat sie sich versprochen - jedenfalls passt das "late" nicht zu der ansonsten bisher sehr einstudiert wirkenden Aussage.

Edit: Weiter unten steht es wieder:

and we're on schedule to sample later this year.

Dresdenboy

Redaktion

☆☆☆☆☆☆

Auf dieser herumschwirrenden Folie stand auch "late".Naja, bis dahin war es jedenfalls immer "later", und nicht "late". Möglicherweise hat sie sich versprochen - jedenfalls passt das "late" nicht zu der ansonsten bisher sehr einstudiert wirkenden Aussage.

Edit: Weiter unten steht es wieder:

Crashtest

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 11.11.2008

- Beiträge

- 9.275

- Renomée

- 1.413

- Standort

- Leipzig

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- Collatz, yoyo, radac

- Lieblingsprojekt

- yoyo

- Meine Systeme

- Ryzen: 2x1600, 5x1700, 1x2700,1x3600, 1x5600X; EPYC 7V12 und Kleinzeuch

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Lenovo IdeaPad 5 14ALC05

- Details zu meinem Desktop

- Prozessor

- Ryzen 7950X / Ryzen 4750G

- Mainboard

- ASRock B650M PGRT / X570D4U

- Kühlung

- be quiet! Dark Rock Pro4 / Pure Rock Slim 2

- Speicher

- 64GB DDR5-5600 G Skill F5-5600J3036D16G / 32 GB DDR4-3200 ECC

- Grafikprozessor

- Raphael IGP / ASpeed AST-2500

- Display

- 27" Samsung LF27T450F

- SSD

- KINGSTON SNVS2000G

- HDD

- - / 8x Seagate IronWolf Pro 20TB

- Optisches Laufwerk

- 1x B.Ray - LG BD-RE BH16NS55

- Soundkarte

- onboard HD?

- Gehäuse

- zu kleines für die GPU

- Netzteil

- be quiet! Pure Power 11 400W / dito

- Tastatur

- CHERRY SECURE BOARD 1.0

- Maus

- Logitech RX250

- Betriebssystem

- Windows 10 19045.4355 / Server 20348.2227

- Webbrowser

- Edge 124.0.2478.51

- Verschiedenes

- U320 SCSI-Controller !!!!

- Internetanbindung

- ▼1000 MBit ▲82 MBit

also 4+4 bei rd 5GHz und 165W bekommt AMD auch hin; man kann die 9590er FX durchaus so mit rd 180W auf 5GHz bekommen (wie reden von 32nm SOI vs. 14nm bei Intel) !

In welchen Benchmarks denn? Und auf welchem Takt?

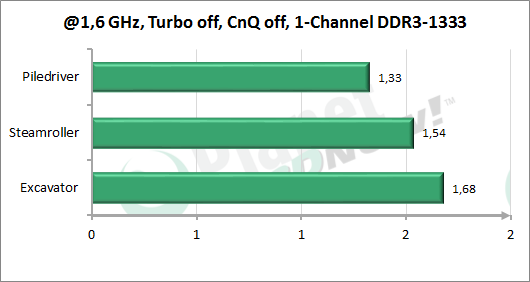

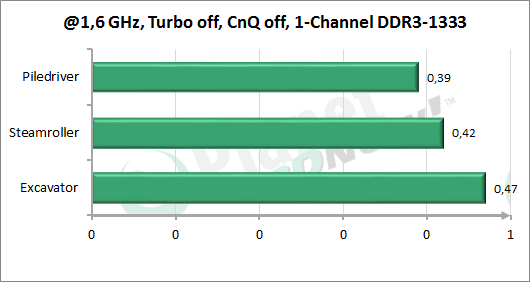

Cinebench R11.5 mit A10-8700P

http://www.notebookcheck.net/Carrizo-in-Review-How-does-AMD-s-A10-8700P-Perform.147654.0.html

Sind aber nur grobe Schätzungen meinerseits, deshalb fragte ich ja ob es taktnormierte Vergleiche irgendwo im Netz gibt?

Zuletzt bearbeitet:

y33H@

Admiral Special

- Mitglied seit

- 16.05.2011

- Beiträge

- 1.768

- Renomée

- 10

Was doch passt: Samples "later this year", Retail "late in the year".Edit: Weiter unten steht es wieder:

Ich bezweifle, dass sich Lisa Su bei einem Earnings Call bei einer Aussage zu Zen verspricht, da hängen zu viele Analysten an ihren Lippen. Seit Monaten ist der interne Stand, dass Zen-basierte CPUs erst im (Spät)herbst 2016 erscheinen. Mich würde ein Vorgehen ähnlich der HD 7970 nicht allzu sehr wundern: Reviews im Dezember, erhältlich in geringen Stückzahlen ab Januar. Lieber wäre mir freilich, dass die neuen FX viel früher kommen - ernsthafte Hinweise darauf gibt's aber keine.

BoMbY

Grand Admiral Special

- Mitglied seit

- 22.11.2001

- Beiträge

- 7.468

- Renomée

- 293

- Standort

- Aachen

- Details zu meinem Desktop

- Prozessor

- Ryzen 3700X

- Mainboard

- Gigabyte X570 Aorus Elite

- Kühlung

- Noctua NH-U12A

- Speicher

- 2x16 GB, G.Skill F4-3200C14D-32GVK @ 3600 16-16-16-32-48-1T

- Grafikprozessor

- RX 5700 XTX

- Display

- Samsung CHG70, 32", 2560x1440@144Hz, FreeSync2

- SSD

- AORUS NVMe Gen4 SSD 2TB, Samsung 960 EVO 1TB, Samsung 840 EVO 1TB, Samsung 850 EVO 512GB

- Optisches Laufwerk

- Sony BD-5300S-0B (eSATA)

- Gehäuse

- Phanteks Evolv ATX

- Netzteil

- Enermax Platimax D.F. 750W

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox

Nein, nur verstehen kann ich die endlosen Verzögerungen auch nicht wirklich. Und auch die AM4-Geschichte erscheint mir seltsam. Zum einen, dass die MB-Hersteller teilweise schon in den Startlöchern zu stehen scheinen, und die Aussage von AMD gegenüber Heise, dass es kein Release von Bristol Ridge AM4 APUs ohne Zen geben wird.

cyrusNGC_224

Grand Admiral Special

- Mitglied seit

- 01.05.2014

- Beiträge

- 5.924

- Renomée

- 117

- Aktuelle Projekte

- POGS, Asteroids, Milkyway, SETI, Einstein, Enigma, Constellation, Cosmology

- Lieblingsprojekt

- POGS, Asteroids, Milkyway

- Meine Systeme

- X6 PII 1090T, A10-7850K, 6x Athlon 5350, i7-3632QM, C2D 6400, AMD X4 PII 810, 6x Odroid U3

- BOINC-Statistiken

Etwas mehr Klarheit wäre wünschenswert. Oder sollte man bewußt klein stapeln, um positiv "überraschen" zu können?

Effe

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 17.02.2011

- Beiträge

- 3.184

- Renomée

- 164

- Standort

- Im Havelland

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- Rosetta & TN-Grid + F&H ->>> FCK CVD19 !

- Lieblingsprojekt

- Einstein@Home

- Meine Systeme

- 3700X+2080+1650; 2400G+290X+560D+Vega11; 2200G+ 5700XT+Vega8; i7860+R7950; i73930K+1660+Vega56+750ti

- BOINC-Statistiken

- Folding@Home-Statistiken

- Details zu meinem Desktop

- Prozessor

- RyZen R7-3700X; RyZen 5 2400G

- Mainboard

- ASUS X370 Prime Pro; MSI B350M Mortar

- Kühlung

- Alpenföhn Brocken 2; Alpenföhn Wasser

- Speicher

- 32GB Crucial Ballistix Sport CL16 3200 MHz ;GSkill F4-3200C14D-16GTZ;

- Grafikprozessor

- MSI Radeon RX 5700 XT Gaming X; Vega 11 + Inno3D GTX1660;

- Display

- HP Pavilion 32 HDR; HP Pavilion 32

- SSD

- Crucial P1 1TB NVMe + BX500 960GB; Sandisk Plus 480GB

- HDD

- WD Blue 1TB; WD Purple 3TB

- Soundkarte

- X-Fi Titanium Fatal1ty; X-Fi Titanium

- Gehäuse

- Chieftec Smart CH-09B-U3; Sharkoon CA-M silber

- Netzteil

- Aerocool P7 650W; SST-SX500-LG

- Betriebssystem

- Win10 64bit

- Webbrowser

- Firefox X,; Chrome 10000

Welche endlosen Verzögerungen? Es steht nichts fest, außer Ende 2016 für ZEN. Der Rest ist stochern im Gerüchtenebel.die endlosen Verzögerungen auch nicht wirklich.

BoMbY

Grand Admiral Special

- Mitglied seit

- 22.11.2001

- Beiträge

- 7.468

- Renomée

- 293

- Standort

- Aachen

- Details zu meinem Desktop

- Prozessor

- Ryzen 3700X

- Mainboard

- Gigabyte X570 Aorus Elite

- Kühlung

- Noctua NH-U12A

- Speicher

- 2x16 GB, G.Skill F4-3200C14D-32GVK @ 3600 16-16-16-32-48-1T

- Grafikprozessor

- RX 5700 XTX

- Display

- Samsung CHG70, 32", 2560x1440@144Hz, FreeSync2

- SSD

- AORUS NVMe Gen4 SSD 2TB, Samsung 960 EVO 1TB, Samsung 840 EVO 1TB, Samsung 850 EVO 512GB

- Optisches Laufwerk

- Sony BD-5300S-0B (eSATA)

- Gehäuse

- Phanteks Evolv ATX

- Netzteil

- Enermax Platimax D.F. 750W

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox

AMD muss liefern, und das schnell. Und im Moment gibt es nur Nebelkerzen von denen.

Ansonsten: AMD Updates Its Roadmap for 2016 and 2017.

Die "Transformational Memory Architecture" für die Zen-Server-APUs dürfte übrigens das hier sein: Die-stacked memory device with reconfigurable logic.

Für die "Disruptive Memory Bandwidth" allgemein vermute ich mal, dass es pro zwei Zen-Kernen einen DDR4-Speicherkanal gibt. Also Quad-Channel bei 8 Kernen, Octa-Channel bei 16 Kernen.

Ansonsten wäre die Idee von 3D-Stacking für CPUs natürlich auch interessant.

Wäre es eventuell denkbar, dass Bristol Ridge ein Excavator-Shrink ist (wie auch immer die das hinbekommen haben sollten)? Das könnte einiges erklären.

Ansonsten: AMD Updates Its Roadmap for 2016 and 2017.

Die "Transformational Memory Architecture" für die Zen-Server-APUs dürfte übrigens das hier sein: Die-stacked memory device with reconfigurable logic.

Für die "Disruptive Memory Bandwidth" allgemein vermute ich mal, dass es pro zwei Zen-Kernen einen DDR4-Speicherkanal gibt. Also Quad-Channel bei 8 Kernen, Octa-Channel bei 16 Kernen.

Ansonsten wäre die Idee von 3D-Stacking für CPUs natürlich auch interessant.

Wäre es eventuell denkbar, dass Bristol Ridge ein Excavator-Shrink ist (wie auch immer die das hinbekommen haben sollten)? Das könnte einiges erklären.

Dresdenboy

Redaktion

☆☆☆☆☆☆

Ja, mit Gabriel Loh's Veröffentlichungen und Patenten bekommt man einen Eindruck, was uns da erwarten könnte. Stichworte: PIM, L4 HBM Caches, NVRAM, 2.5D oder gar 3D Stacking (Logik-Chip darf je nach Kühlung auch >40W haben).AMD muss liefern, und das schnell. Und im Moment gibt es nur Nebelkerzen von denen.

Ansonsten: AMD Updates Its Roadmap for 2016 and 2017.

Die "Transformational Memory Architecture" für die Zen-Server-APUs dürfte übrigens das hier sein: Die-stacked memory device with reconfigurable logic.

Für die "Disruptive Memory Bandwidth" allgemein vermute ich mal, dass es pro zwei Zen-Kernen einen DDR4-Speicherkanal gibt. Also Quad-Channel bei 8 Kernen, Octa-Channel bei 16 Kernen.

Ansonsten wäre die Idee von 3D-Stacking für CPUs natürlich auch interessant.

Wäre es eventuell denkbar, dass Bristol Ridge ein Excavator-Shrink ist (wie auch immer die das hinbekommen haben sollten)? Das könnte einiges erklären.

Können 2 Zen-Kerne + SMT + L3 + GBs an L4 den DDR4-Kanal auslasten? Ansonsten knabbern die vielen Kanäle nur Energie weg. Deshalb gibt es ja u. a. das HBM + NVRAM-Konzept.

BoMbY

Grand Admiral Special

- Mitglied seit

- 22.11.2001

- Beiträge

- 7.468

- Renomée

- 293

- Standort

- Aachen

- Details zu meinem Desktop

- Prozessor

- Ryzen 3700X

- Mainboard

- Gigabyte X570 Aorus Elite

- Kühlung

- Noctua NH-U12A

- Speicher

- 2x16 GB, G.Skill F4-3200C14D-32GVK @ 3600 16-16-16-32-48-1T

- Grafikprozessor

- RX 5700 XTX

- Display

- Samsung CHG70, 32", 2560x1440@144Hz, FreeSync2

- SSD

- AORUS NVMe Gen4 SSD 2TB, Samsung 960 EVO 1TB, Samsung 840 EVO 1TB, Samsung 850 EVO 512GB

- Optisches Laufwerk

- Sony BD-5300S-0B (eSATA)

- Gehäuse

- Phanteks Evolv ATX

- Netzteil

- Enermax Platimax D.F. 750W

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox

Wobei das Patent hier besser auf "Transformational" passt:

Edit: Kurz gesagt: Solange die Software nicht speziell damit umgehen kann, wird HBM und DDR4-RAM zusammengefasst und von der CPU verwaltet, und das System kann beides in Kombination als gemeinsamen Hauptspeicher nutzen.

Multi-level memory hierarchy

Described is a system and method for a multi-level memory hierarchy. Each level is based on different attributes including, for example, power, capacity, bandwidth, reliability, and volatility. In some embodiments, the different levels of the memory hierarchy may use an on-chip stacked dynamic random access memory, (providing fast, high-bandwidth, low-energy access to data) and an off-chip non-volatile random access memory, (providing low-power, high-capacity storage), in order to provide higher-capacity, lower power, and higher-bandwidth performance. The multi-level memory may present a unified interface to a processor so that specific memory hardware and software implementation details are hidden. The multi-level memory enables the illusion of a single-level memory that satisfies multiple conflicting constraints. A comparator receives a memory address from the processor, processes the address and reads from or writes to the appropriate memory level. In some embodiments, the memory architecture is visible to the software stack to optimize memory utilization.

Edit: Kurz gesagt: Solange die Software nicht speziell damit umgehen kann, wird HBM und DDR4-RAM zusammengefasst und von der CPU verwaltet, und das System kann beides in Kombination als gemeinsamen Hauptspeicher nutzen.

Zuletzt bearbeitet:

Dresdenboy

Redaktion

☆☆☆☆☆☆

Die sind schwer zu finden. Diese CB-Scores (11.5) mit festen Taktfrequenzen könnten schonmal helfen:Cinebench R11.5 mit A10-8700P

http://www.notebookcheck.net/Carrizo-in-Review-How-does-AMD-s-A10-8700P-Perform.147654.0.html

Sind aber nur grobe Schätzungen meinerseits, deshalb fragte ich ja ob es taktnormierte Vergleiche irgendwo im Netz gibt?

http://i.imgur.com/YfjdDXf.png

Da es gut skaliert, passt sogar der halbierte 3,2GHz-Interpolationswert (1,65) gut zu dem Ergebnis:

Für den Vergleich:

Cinebench mit Skylake bei fixierten 3,5 GHz:

http://www.pcper.com/reviews/Proces...irst-Enthusiasts/Clock-Clock-Skylake-Broadwel

P3DNow!-Test bei 1,6 GHz:

http://www.planet3dnow.de/cms/18564...er-architekturen/subpage-rendering-cinebench/

Und hier ist noch Geekbench 3.32 x64 mit Carrizo bei versch. festen Taktfrequenzen:

http://i.imgur.com/elw8WNq.png

y33H@

Admiral Special

- Mitglied seit

- 16.05.2011

- Beiträge

- 1.768

- Renomée

- 10

0,47 ptk von 1,65 auf 3,5 GHz wären (Milchmädchen) gerundet 1,0 ptk. Hauen wir da +40 % drauf, laden wir minimal unter Sandy Bridge. Rechnet man dann noch so Zeug wie schnelleren DDR4-RAM im Dual-Channel, eine dritte Cache-Stufe und vll eine flottere Northbridge mit rein, landet man iwo bei Ivy Bridge bis Haswell.

0,47 ptk von 1,65 auf 3,5 GHz wären (Milchmädchen) gerundet 1,0 ptk. Hauen wir da +40 % drauf, laden wir minimal unter Sandy Bridge. Rechnet man dann noch so Zeug wie schnelleren DDR4-RAM im Dual-Channel, eine dritte Cache-Stufe und vll eine flottere Northbridge mit rein, landet man iwo bei Ivy Bridge bis Haswell.

Also bei (0.47/1.6)*3.5 *1,4 lande ich im Ergebnis bei 1.44 d.h zwischen Sandy und Ivy Bridge. Zu Skylake fehlen dann noch 19,5% (alles in Cinebench und bei linearer Skalierung). Wenn AMD es wie bei Carrizo schafft durch die HD-Libs und gute eine gute Kernarchitektur einen sehr sparsamen Kern zu entwickeln, sollte es möglich sein eine schnelle Mobil-CPU auf dem Niveau von Skylake zu produzieren. Bei GPU mit Polaris und mit HBM sollte es dann auch möglich sein eine Mobil-APU zu entwickeln, die im Gesamtpaket deutlich vor Intel liegt.

Ich glaub im Mai werd ich es mal wagen einige Aktien von AMD zu erwerben

gruffi

Grand Admiral Special

- Mitglied seit

- 08.03.2008

- Beiträge

- 5.393

- Renomée

- 65

- Standort

- vorhanden

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 5 1600

- Mainboard

- MSI B350M PRO-VDH

- Kühlung

- Wraith Spire

- Speicher

- 2x 8 GB DDR4-2400 CL16

- Grafikprozessor

- XFX Radeon R7 260X

- Display

- LG W2361

- SSD

- Crucial CT250BX100SSD1

- HDD

- Toshiba DT01ACA200

- Optisches Laufwerk

- LG Blu-Ray-Brenner BH16NS40

- Soundkarte

- Realtek HD Audio

- Gehäuse

- Sharkoon MA-I1000

- Netzteil

- be quiet! Pure Power 9 350W

- Betriebssystem

- Windows 10 Professional 64-bit

- Webbrowser

- Mozilla Firefox

- Verschiedenes

- https://valid.x86.fr/mb4f0j

Cinebench sollte man nicht als IPC Vergleich heranziehen, da es bekanntlich recht stark Intel optimiert ist. Der durchschnittliche IPC Unterschied zwischen AMD und Intel ist geringer als in Cinebench. Ich denke sowas wie Geekbench ist da schon geeigneter für einen groben Vergleich. Allerdings sollte man auch hier diverse Sachen aussen vor lassen. Wie zB AVX Scores, die wenig Aussagekraft für allgemeine Performance haben.

Woerns

Grand Admiral Special

- Mitglied seit

- 05.02.2003

- Beiträge

- 2.983

- Renomée

- 232

Ich glaub im Mai werd ich es mal wagen einige Aktien von AMD zu erwerben

Hättest es besser vorhin tun sollen. Schau mal auf die Kursentwicklung heute.

MfG

Pirx

Admiral Special

- Mitglied seit

- 11.11.2001

- Beiträge

- 1.234

- Renomée

- 11

- Standort

- Mädels auf Bäumen wachsen

- Mein Laptop

- Samsung NC20

- Details zu meinem Desktop

heftigHättest es besser vorhin tun sollen. Schau mal auf die Kursentwicklung heute.

MfG

BoMbY

Grand Admiral Special

- Mitglied seit

- 22.11.2001

- Beiträge

- 7.468

- Renomée

- 293

- Standort

- Aachen

- Details zu meinem Desktop

- Prozessor

- Ryzen 3700X

- Mainboard

- Gigabyte X570 Aorus Elite

- Kühlung

- Noctua NH-U12A

- Speicher

- 2x16 GB, G.Skill F4-3200C14D-32GVK @ 3600 16-16-16-32-48-1T

- Grafikprozessor

- RX 5700 XTX

- Display

- Samsung CHG70, 32", 2560x1440@144Hz, FreeSync2

- SSD

- AORUS NVMe Gen4 SSD 2TB, Samsung 960 EVO 1TB, Samsung 840 EVO 1TB, Samsung 850 EVO 512GB

- Optisches Laufwerk

- Sony BD-5300S-0B (eSATA)

- Gehäuse

- Phanteks Evolv ATX

- Netzteil

- Enermax Platimax D.F. 750W

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox

Aktien kann man eigentlich ehh vergessen, sofern man kein HFT-Bot ist. Ich freue mich schon auf den nächsten Flashcrash.

Hättest es besser vorhin tun sollen. Schau mal auf die Kursentwicklung heute.

MfG

Wahrscheinlich liest Warren Buffet im Forum mit

Dresdenboy

Redaktion

☆☆☆☆☆☆

Ich würde auch gerne andere Werte verwenden.Cinebench sollte man nicht als IPC Vergleich heranziehen, da es bekanntlich recht stark Intel optimiert ist. Der durchschnittliche IPC Unterschied zwischen AMD und Intel ist geringer als in Cinebench. Ich denke sowas wie Geekbench ist da schon geeigneter für einen groben Vergleich. Allerdings sollte man auch hier diverse Sachen aussen vor lassen. Wie zB AVX Scores, die wenig Aussagekraft für allgemeine Performance haben.

Ähnliche Themen

- Antworten

- 96

- Aufrufe

- 9K

- Antworten

- 14

- Aufrufe

- 950

- Antworten

- 102

- Aufrufe

- 11K

- Antworten

- 3

- Aufrufe

- 2K