App installieren

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: This feature may not be available in some browsers.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Spekulationen zu aktuellen und zukünftigen Prozessen bei GlobalFoundries (<= 32nm)

- Ersteller Lynxeye

- Erstellt am

In einem Blogbeitrag erläutert ASML unter anderem, dass ein einzelnes EUV-System satte 180 Tonnen wiegt und in 40 Containern, verteilt auf 20 Lastwagen und drei Flugzeuge, geliefert wird.

Aber ich habe gar keine Rollbahn

In Anlehnung der Kaffee-Werbung - Ich habe gar kein Auto...

In Anlehnung der Kaffee-Werbung - Ich habe gar kein Auto...--- Update ---

Then comes the really hard part. The pre-pulse laser hits the spherical tin droplet and turns it into a pancake-like shape. Then the laser unit fires again, representing the main pulse. The main pulse hits the pancake-like tin droplet and vaporizes it. “We are trying to hit each droplet twice with the pre-pulse and main-pulse at 50,000 times a second,” ASML’s Lercel said.

At that point, the tin vapor becomes plasma. The plasma, in turn, emits EUV light at 13.5nm wavelengths.

Ha ha, und das nur um Licht zu machen

halt welches das nur 13,5 nm Wellenlänge hat...

halt welches das nur 13,5 nm Wellenlänge hat...cyrusNGC_224

Grand Admiral Special

- Mitglied seit

- 01.05.2014

- Beiträge

- 5.924

- Renomée

- 117

- Aktuelle Projekte

- POGS, Asteroids, Milkyway, SETI, Einstein, Enigma, Constellation, Cosmology

- Lieblingsprojekt

- POGS, Asteroids, Milkyway

- Meine Systeme

- X6 PII 1090T, A10-7850K, 6x Athlon 5350, i7-3632QM, C2D 6400, AMD X4 PII 810, 6x Odroid U3

- BOINC-Statistiken

Wenn alleine die Lichterzeugung so extrem aufwendig ist...

Und weiter steht, dass die Effizienz, mit der die Laserleistung in EUV Licht umgewandelt wird, von der Präzision der Treffer abhängt. Und diese Effizienz beträgt momentan sagenhafte 5%.

Eigentlich alles unglaublich.

--- Update ---

So ist auch nicht verwunderlich, dass so eine Anlage einen ganzen Güterzug füllen würde.

Und weiter steht, dass die Effizienz, mit der die Laserleistung in EUV Licht umgewandelt wird, von der Präzision der Treffer abhängt. Und diese Effizienz beträgt momentan sagenhafte 5%.

Eigentlich alles unglaublich.

--- Update ---

So ist auch nicht verwunderlich, dass so eine Anlage einen ganzen Güterzug füllen würde.

BoMbY

Grand Admiral Special

- Mitglied seit

- 22.11.2001

- Beiträge

- 7.468

- Renomée

- 293

- Standort

- Aachen

- Details zu meinem Desktop

- Prozessor

- Ryzen 3700X

- Mainboard

- Gigabyte X570 Aorus Elite

- Kühlung

- Noctua NH-U12A

- Speicher

- 2x16 GB, G.Skill F4-3200C14D-32GVK @ 3600 16-16-16-32-48-1T

- Grafikprozessor

- RX 5700 XTX

- Display

- Samsung CHG70, 32", 2560x1440@144Hz, FreeSync2

- SSD

- AORUS NVMe Gen4 SSD 2TB, Samsung 960 EVO 1TB, Samsung 840 EVO 1TB, Samsung 850 EVO 512GB

- Optisches Laufwerk

- Sony BD-5300S-0B (eSATA)

- Gehäuse

- Phanteks Evolv ATX

- Netzteil

- Enermax Platimax D.F. 750W

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox

Sieht ja nicht schlecht aus:

GLOBALFOUNDRIES Expands to Meet Worldwide Customer Demand

[...]

In the United States, GF plans to expand 14nm FinFET capacity by an additional 20 percent at its Fab 8 facility in New York, with the new production capabilities to come online in the beginning of 2018.

[...]

In Germany, GF plans to build up 22FDX® 22nm FD-SOI capacity at is Fab 1 facility in Dresden to meet demand for the Internet of Things (IoT), smartphone processors, automotive electronics, and other battery-powered wirelessly connected applications, growing the overall fab capacity by 40 percent by 2020.

[...]

In China, GF and the Chengdu municipality have formed a partnership to build a fab in Chengdu. The partners plan to establish a 300mm fab to support the growth of the Chinese semiconductor market and to meet accelerating global customer demand for 22FDX

[...]

MagicEye04

Grand Admiral Special

- Mitglied seit

- 20.03.2006

- Beiträge

- 23.299

- Renomée

- 1.889

- Standort

- oops,wrong.planet..

- Aktuelle Projekte

- Seti,WCG,Einstein + was gerade Hilfe braucht

- Lieblingsprojekt

- Seti

- Meine Systeme

- R7-1700+GTX1070ti,R7-1700+RadeonVII, FX-8350+GTX1050ti, X4-5350+GT1030, X2-240e+RX460

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Dell Latitude E7240

- Details zu meinem Desktop

- Prozessor

- R9-3950X (@65W)

- Mainboard

- Asus Prime B550plus

- Kühlung

- TR Macho

- Speicher

- 2x16GiB Corsair LPX2666C16

- Grafikprozessor

- Radeon VII

- Display

- LG 32UD99-W 81,3cm

- SSD

- Crucial MX500-250GB, Samsung EVO280 256GB

- HDD

- Seagate 7200.14 2TB (per eSATAp)

- Optisches Laufwerk

- LG DVDRAM GH24NS90

- Soundkarte

- onboard

- Gehäuse

- Nanoxia Deep Silence1

- Netzteil

- BeQuiet StraightPower 11 550W

- Tastatur

- Cherry RS6000

- Maus

- Logitech RX600

- Betriebssystem

- Ubuntu

- Webbrowser

- Feuerfuchs

- Verschiedenes

- 4x Nanoxia Lüfter (120/140mm) , Festplatte in Bitumenbox

Man könnte es auch anders interpretieren:

- Die Chinesen wollen in Zukunft keine europäischen oder amerikanischen Chips kaufen, also soll GF gefälligst dort eine Fab bauen, dafür gibts ordentlich Zuschuss.

- Die vorhandenen Anlagen bei GF sind schon wieder veraltet und müssen teilweise ersetzt werden, um weiterhin konkurrenzfähig zu bleiben, obwohl sie noch gar nicht so viel produziert haben. Man verkauft das Ganze aber lieber positiv als "Kapazitätserweiterung", die vermutlich ohnehin nebenbei angefallen wäre.

Das würde in meinen Augen irgendwie besser zu den Jammermeldungen passen, die noch gar nicht so alt sind und in Richtung Jobabbau gingen.

- Die Chinesen wollen in Zukunft keine europäischen oder amerikanischen Chips kaufen, also soll GF gefälligst dort eine Fab bauen, dafür gibts ordentlich Zuschuss.

- Die vorhandenen Anlagen bei GF sind schon wieder veraltet und müssen teilweise ersetzt werden, um weiterhin konkurrenzfähig zu bleiben, obwohl sie noch gar nicht so viel produziert haben. Man verkauft das Ganze aber lieber positiv als "Kapazitätserweiterung", die vermutlich ohnehin nebenbei angefallen wäre.

Das würde in meinen Augen irgendwie besser zu den Jammermeldungen passen, die noch gar nicht so alt sind und in Richtung Jobabbau gingen.

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Hier eine aktuelle Roadmap der Fertigungsnodes:

http://www.eetimes.com/document.asp?doc_id=1331185&page_number=1

http://www.eetimes.com/document.asp?doc_id=1331185&page_number=1

BavarianRealist

Grand Admiral Special

- Mitglied seit

- 06.02.2010

- Beiträge

- 3.358

- Renomée

- 80

Wenn AMD jetzt schon zum 02.03.2017 schon über 1 Mio. Ryzen-CPUs ausliefern will, von denen alles 8-Kerner sind, dann müsste entweder das Yield des 14nm-Prozesses echt gut sein, oder AMD müsste gleichzeitig auf einem Haufen 6- und 4-Kerner sitzen, die man erst mal zurück hält, oder?

hoschi_tux

Grand Admiral Special

- Mitglied seit

- 08.03.2007

- Beiträge

- 4.763

- Renomée

- 287

- Standort

- Ilmenau

- Aktuelle Projekte

- Einstein@Home, Predictor@Home, QMC@Home, Rectilinear Crossing No., Seti@Home, Simap, Spinhenge, POEM

- Lieblingsprojekt

- Seti/Spinhenge

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen R9 5900X

- Mainboard

- ASUS TUF B450m Pro-Gaming

- Kühlung

- Noctua NH-U12P

- Speicher

- 2x 16GB Crucial Ballistix Sport LT DDR4-3200, CL16-18-18

- Grafikprozessor

- AMD Radeon RX 6900XT (Ref)

- Display

- LG W2600HP, 26", 1920x1200

- HDD

- Crucial M550 128GB, Crucial M550 512GB, Crucial MX500 2TB, WD7500BPKT

- Soundkarte

- onboard

- Gehäuse

- Cooler Master Silencio 352M

- Netzteil

- Antec TruePower Classic 550W

- Betriebssystem

- Gentoo 64Bit, Win 7 64Bit

- Webbrowser

- Firefox

Ryzen soll ja seit Oktober fertig sein, da wundert die Stückzahl nicht.

Kleinere/teildefekte dürften zuerst an die OEMs gehen um eine Alibiproduktlinie aufzubauen.

Kleinere/teildefekte dürften zuerst an die OEMs gehen um eine Alibiproduktlinie aufzubauen.

amdfanuwe

Grand Admiral Special

- Mitglied seit

- 24.06.2010

- Beiträge

- 2.372

- Renomée

- 34

- Details zu meinem Desktop

- Prozessor

- 4200+

- Mainboard

- M3A-H/HDMI

- Kühlung

- ein ziemlich dicker

- Speicher

- 2GB

- Grafikprozessor

- onboard

- Display

- Samsung 20"

- HDD

- WD 1,5TB

- Netzteil

- Extern 100W

- Betriebssystem

- XP, AndLinux

- Webbrowser

- Firefox

- Verschiedenes

- Kaum hörbar

AMD müsste gleichzeitig auf einem Haufen 6- und 4-Kerner sitzen, die man erst mal zurück hält, oder?

Die muss AMD ja auch schön sammeln. Denke mal, dass die Nachfrage nach CPUs in der 150 - 300€ Klasse höher ist als in der 300- 550€ Klasse.

Denke auch mal, dass die 4-Kerner sowohl aus Summit Ridge als auch aus Raven Ridge Dies gewonnen werden.

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Ich glaube auch, dass die Raven Ridge 4-Kern CPUs den Hauptteil ausmachen werden bei Veröffentlichung der 4-Core Ryzen. Ich vermute AMD wird diese CPU-Transistoren weniger Dicht packen und dafür die Möglichkeit für höhere Taktraten einbauen. Es werden auf jeden Fall Unterschiede zu merken sein, denke ich, die alleine schon aus dem reiferen Prozess entstehen. Die 8-Core Dies werden für die 6-Cores verwendet und die APUs sind ja auch schon in der Produktion, wo eben defekte iGPUs zu einem 4-Core Ryzen führen.

Pirx

Admiral Special

- Mitglied seit

- 11.11.2001

- Beiträge

- 1.234

- Renomée

- 11

- Standort

- Mädels auf Bäumen wachsen

- Mein Laptop

- Samsung NC20

- Details zu meinem Desktop

Die APUs sind schon in Produktion??

Gibts Infos zu (weiteren) Kapazitäten, denn ich glaube kaum, daß GF das alles (Ryzen, Naples, RR, Polaris, Vega) gleichzeitig schafft.

Gibts Infos zu (weiteren) Kapazitäten, denn ich glaube kaum, daß GF das alles (Ryzen, Naples, RR, Polaris, Vega) gleichzeitig schafft.

MagicEye04

Grand Admiral Special

- Mitglied seit

- 20.03.2006

- Beiträge

- 23.299

- Renomée

- 1.889

- Standort

- oops,wrong.planet..

- Aktuelle Projekte

- Seti,WCG,Einstein + was gerade Hilfe braucht

- Lieblingsprojekt

- Seti

- Meine Systeme

- R7-1700+GTX1070ti,R7-1700+RadeonVII, FX-8350+GTX1050ti, X4-5350+GT1030, X2-240e+RX460

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Dell Latitude E7240

- Details zu meinem Desktop

- Prozessor

- R9-3950X (@65W)

- Mainboard

- Asus Prime B550plus

- Kühlung

- TR Macho

- Speicher

- 2x16GiB Corsair LPX2666C16

- Grafikprozessor

- Radeon VII

- Display

- LG 32UD99-W 81,3cm

- SSD

- Crucial MX500-250GB, Samsung EVO280 256GB

- HDD

- Seagate 7200.14 2TB (per eSATAp)

- Optisches Laufwerk

- LG DVDRAM GH24NS90

- Soundkarte

- onboard

- Gehäuse

- Nanoxia Deep Silence1

- Netzteil

- BeQuiet StraightPower 11 550W

- Tastatur

- Cherry RS6000

- Maus

- Logitech RX600

- Betriebssystem

- Ubuntu

- Webbrowser

- Feuerfuchs

- Verschiedenes

- 4x Nanoxia Lüfter (120/140mm) , Festplatte in Bitumenbox

Ich würds auch so machen: Erstmal die bedienen, die viel Geld auszugeben bereit sind oder die es nicht erwarten können.

Dann die Leute versorgen, die scharf kalkulieren, also eher 4-6 Kerne nehmen.

Und zum Schluss die absoluten Sparfüchse.

In der Vergangenheit wurden ja auch einfach gute CPUs absichtlich runtergestuft (also funktionierende Kerne deaktiviert etc.), weil nicht genügend Leute die kaufen wollten für den höheren Preis, man sich aber auch mit Ramschpreisen diesen Markt nicht kaputt machen wollte.

Aber warum sollte der Fertiger die Transistoren weniger dicht packen? Das kostet doch Geld und gerade für die Brot- und Butter-CPUs wird man sich das nicht leisten können.

Die Nodes weiter oben sind doch inzwischen eh nur noch Marketing, das hat nichts mehr mit der Realität zu tun. Eigentlich müssten die Hersteller dazu übergehen, die Fläche pro Transistor anzugeben.

Dann die Leute versorgen, die scharf kalkulieren, also eher 4-6 Kerne nehmen.

Und zum Schluss die absoluten Sparfüchse.

In der Vergangenheit wurden ja auch einfach gute CPUs absichtlich runtergestuft (also funktionierende Kerne deaktiviert etc.), weil nicht genügend Leute die kaufen wollten für den höheren Preis, man sich aber auch mit Ramschpreisen diesen Markt nicht kaputt machen wollte.

Aber warum sollte der Fertiger die Transistoren weniger dicht packen? Das kostet doch Geld und gerade für die Brot- und Butter-CPUs wird man sich das nicht leisten können.

Die Nodes weiter oben sind doch inzwischen eh nur noch Marketing, das hat nichts mehr mit der Realität zu tun. Eigentlich müssten die Hersteller dazu übergehen, die Fläche pro Transistor anzugeben.

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Na wäre ein 4-Core Ryzen der schneller taktet als der i7-7700K nicht eine Überraschung weil er nicht so dicht gepackt ist  Zudem sowieso andere Transistoren verwendet werden auf APUs als auf reinen CPUs. Sie müssen ja auch für den GPU Teil geeignet sein. Für 10% mehr Diefläche den Konkurrenten beim Takt abzuhängen könnte eine lohnende Investition sein. Es würde kaum auffallen, da ja sowieso der halbe Die (iGPU) deaktiviert werden müsste für die 4-Core Ryzen. Ausser AMD nimmt natürlich einfach die APUs und nennt diese dann R3.

Zudem sowieso andere Transistoren verwendet werden auf APUs als auf reinen CPUs. Sie müssen ja auch für den GPU Teil geeignet sein. Für 10% mehr Diefläche den Konkurrenten beim Takt abzuhängen könnte eine lohnende Investition sein. Es würde kaum auffallen, da ja sowieso der halbe Die (iGPU) deaktiviert werden müsste für die 4-Core Ryzen. Ausser AMD nimmt natürlich einfach die APUs und nennt diese dann R3.

Zudem sowieso andere Transistoren verwendet werden auf APUs als auf reinen CPUs. Sie müssen ja auch für den GPU Teil geeignet sein. Für 10% mehr Diefläche den Konkurrenten beim Takt abzuhängen könnte eine lohnende Investition sein. Es würde kaum auffallen, da ja sowieso der halbe Die (iGPU) deaktiviert werden müsste für die 4-Core Ryzen. Ausser AMD nimmt natürlich einfach die APUs und nennt diese dann R3.

Zudem sowieso andere Transistoren verwendet werden auf APUs als auf reinen CPUs. Sie müssen ja auch für den GPU Teil geeignet sein. Für 10% mehr Diefläche den Konkurrenten beim Takt abzuhängen könnte eine lohnende Investition sein. Es würde kaum auffallen, da ja sowieso der halbe Die (iGPU) deaktiviert werden müsste für die 4-Core Ryzen. Ausser AMD nimmt natürlich einfach die APUs und nennt diese dann R3.

Zuletzt bearbeitet:

MagicEye04

Grand Admiral Special

- Mitglied seit

- 20.03.2006

- Beiträge

- 23.299

- Renomée

- 1.889

- Standort

- oops,wrong.planet..

- Aktuelle Projekte

- Seti,WCG,Einstein + was gerade Hilfe braucht

- Lieblingsprojekt

- Seti

- Meine Systeme

- R7-1700+GTX1070ti,R7-1700+RadeonVII, FX-8350+GTX1050ti, X4-5350+GT1030, X2-240e+RX460

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Dell Latitude E7240

- Details zu meinem Desktop

- Prozessor

- R9-3950X (@65W)

- Mainboard

- Asus Prime B550plus

- Kühlung

- TR Macho

- Speicher

- 2x16GiB Corsair LPX2666C16

- Grafikprozessor

- Radeon VII

- Display

- LG 32UD99-W 81,3cm

- SSD

- Crucial MX500-250GB, Samsung EVO280 256GB

- HDD

- Seagate 7200.14 2TB (per eSATAp)

- Optisches Laufwerk

- LG DVDRAM GH24NS90

- Soundkarte

- onboard

- Gehäuse

- Nanoxia Deep Silence1

- Netzteil

- BeQuiet StraightPower 11 550W

- Tastatur

- Cherry RS6000

- Maus

- Logitech RX600

- Betriebssystem

- Ubuntu

- Webbrowser

- Feuerfuchs

- Verschiedenes

- 4x Nanoxia Lüfter (120/140mm) , Festplatte in Bitumenbox

Das wäre mir neu, dass die Transistoren bereits für eine bestimmte Aufgabe geeignet sein müssen (abgesehen von wirklich diskreten Transistoren oder solche für Höchstfrequenzen um die 100GHz).

Die müssen in der CPU oder GPU einfach nur schnell und verlustarm schalten. Die Funktion wird ein paar Ebenen darüber durch die Verdrahtung festgelegt.

Speicher und Logik haben sicherlich gewisse Unterschiede in der Fertigung, was die Verdrahtung angeht.

Und wenn sie schneller schalten sollen, dann sind eine gewisse räumliche Nähe und kurze Leiterbahnen eigentlich eher positiv zu sehen.

Was mich wieder an einen Professor vor 20 Jahren erinnert: "In wenigen Jahren werden CPUs die 2GHz erreichen, dann ist rechnerisch Schluss, weil man nicht dichter packen kann, in 10 Jahren haben wird dann überall optische Verbindungen im PC". 20 Jahre später ist von Optik immer noch nichts im PC zu sehen und die Probleme der zu langen Wege hat man durch andere Übertragungsprotokolle gelöst.

Die müssen in der CPU oder GPU einfach nur schnell und verlustarm schalten. Die Funktion wird ein paar Ebenen darüber durch die Verdrahtung festgelegt.

Speicher und Logik haben sicherlich gewisse Unterschiede in der Fertigung, was die Verdrahtung angeht.

Und wenn sie schneller schalten sollen, dann sind eine gewisse räumliche Nähe und kurze Leiterbahnen eigentlich eher positiv zu sehen.

Was mich wieder an einen Professor vor 20 Jahren erinnert: "In wenigen Jahren werden CPUs die 2GHz erreichen, dann ist rechnerisch Schluss, weil man nicht dichter packen kann, in 10 Jahren haben wird dann überall optische Verbindungen im PC". 20 Jahre später ist von Optik immer noch nichts im PC zu sehen und die Probleme der zu langen Wege hat man durch andere Übertragungsprotokolle gelöst.

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Mit Kaveri kamen die zum Einsatz erstmalig

http://www.tomshardware.com/reviews/a10-7850k-a8-7600-kaveri,3725.html

http://www.tomshardware.com/reviews/a10-7850k-a8-7600-kaveri,3725.html

Allerdings ist es eher anders herum als ich es erinnerte, es sind kleinere Frequenzen zu erwarten von den APUs...SchadeOne component of this approach involved re-thinking lithography. In partnership with GlobalFoundries, AMD is shifting from 32 nm SOI to a 28 nm bulk silicon process. Now, there are associated advantages and disadvantages. Previously, AMD was building its APUs using technology optimized for CPUs. That allowed chips like the A10-6800K to hit clock rates as high as 4.4 GHz through Turbo Core. But tuning for low density, low resistance, and ultimately higher frequencies negatively affected the number of transistors that AMD could fit on a die, limiting the complexity of its GPU. In a world where x86 cores are considered “fast enough” in workloads that wait for user input, the decision was made to slide the scale toward density. AMD calls this APU-optimized, but the bottom line is that it’s using slower, higher-resistance transistors in order to facilitate better area utilization.

amdfanuwe

Grand Admiral Special

- Mitglied seit

- 24.06.2010

- Beiträge

- 2.372

- Renomée

- 34

- Details zu meinem Desktop

- Prozessor

- 4200+

- Mainboard

- M3A-H/HDMI

- Kühlung

- ein ziemlich dicker

- Speicher

- 2GB

- Grafikprozessor

- onboard

- Display

- Samsung 20"

- HDD

- WD 1,5TB

- Netzteil

- Extern 100W

- Betriebssystem

- XP, AndLinux

- Webbrowser

- Firefox

- Verschiedenes

- Kaum hörbar

es sind kleinere Frequenzen zu erwarten von den APUs...Schade

Damals ging es um die Fläche und den Verbrauch. Deshalb "slower, higher -resistance transistors".

Bei 14nm FF sieht das schon wieder anders aus, die leakage ist nicht so hoch. Da kann man auch wieder "dickere, schnellere" Transistoren einplanen.

Je nach Anwendungsfall gibt es mehr als 10 verschiedene Designs für ein einfaches Gatter, von 2 (npn + pnp) schnellen, saufenden Transistoren für einen einfachen Inverter mit mehr als 6 Transistoren für einen sparsamen Inverter. Flächenoptimiert, Verbrauchsoptimiert, Geschwindigkeitsoptimiert, Temperaturoptimiert mit entsprechenden Kombinationen.

Die Transistoren werden auf das Die in mehreren Prozessschritten geätzt, dotiert etc. Da bestimmen die Masken, wie ein Transistor werden soll. Die müssen nicht alle gleich sein.

Ich denke mal, dass AMD einfach den vorhandenen, getesteten 4 Kern Cluster für die APU nimmt. Spart Kosten und Zeit.

Niedrigere Taktraten sind dann zu erwarten, wenn der GPU-Teil ausgelastet ist und die TDP erreicht wird. Ist ja bei Carrizo und Bristol Ridge auch schon so.

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Wie du siehst reden wir seit 6 Beiträgen über den möglichen Unterschied beim Takt der Salvage Parts von Summit Ridge und Raven Ridge wo die GPU deaktiviert ist und diese als 4-Core-CPU Versionen verarbeitet werden. Daher spielt der GPU-Teil bei dieser Betrachtung keine Rolle.

--- Update ---

http://www.pcgameshardware.de/Polaris-Codename-265453/News/welche-Chips-stellt-Samsung-her-1203182/

--- Update ---

Ja Samsung ist auch schon gebucht.Die APUs sind schon in Produktion??

Gibts Infos zu (weiteren) Kapazitäten, denn ich glaube kaum, daß GF das alles (Ryzen, Naples, RR, Polaris, Vega) gleichzeitig schafft.

http://www.pcgameshardware.de/Polaris-Codename-265453/News/welche-Chips-stellt-Samsung-her-1203182/

GF hat seit 2015 mehr Wafer produziert jährlich als Intel:Am wahrscheinlichsten sei aber immer noch, so die Kollegen, dass AMD Samsungs Fabriken vor allem für kommende Produktlinien wie Zen-Prozessoren, neue Konsolen-APUs und Vega-GPUs nutzt. Auch die wären eigentlich eher bei Globalfoundries zuhause, aufgrund identischer Produktionsprozesse könne man deren Produktionsstätten aber ebenfalls recht mühelos wechseln.

According to IC Insights, GlobalFoundries completed the 2015 with wafer manufacturing capacity of 762,000 wspm (wafer starts per month) i.e. 4.7% of worldwide capacity, pushing Intel into the fourth position. As Intel transitions to 14nm, the company reduced capacity by 1%, to 714,000 wspm. GlobalFoundries is not expected to reduce capacity anytime soon, as the company continues the path of increasing market share.

Furthermore, GlobalFoundries recently completed the purchase of more land around Fab 8 site in New York State, as they plan to add in more manufacturing capacity. The Fab 8 site was originally called for a single clean room with 60,000 wspm capacity, which radically increased as the world demand for semiconductors increased almost exponentialy, mostly due to explosion in mobile market, with smartphones and tablets requiring billions of additional semiconductor products – processors and memory chips – to be manufactured in order to satisfy the demand. Today’s plans call for three large clean rooms, which would take GlobalFoundries ever so closer to TSMC. Still, not even three clean rooms at Malta, NY would not suffice to overtake TSMC. Thus, we managed to learn that key goal of GlobalFoundries is to increase the revenue into a $10 billion range. While the numbers are not made public, GlobalFoundries achieved estimated $4.4-4.6 billion in 2014, but the numbers for 2015 should be significantly different due to acquisition of IBM’s foundry business.

Zuletzt bearbeitet:

Keine Ahnung welche Vorstellung Du hast wenn Du was von dicht schreibst. Aber AMD wird kaum einen weiteren Kern entwickeln mit anderer Cell-Bibliothek usw.Ich glaube auch, dass die Raven Ridge 4-Kern CPUs den Hauptteil ausmachen werden bei Veröffentlichung der 4-Core Ryzen. Ich vermute AMD wird diese CPU-Transistoren weniger Dicht packen und dafür die Möglichkeit für höhere Taktraten einbauen.

--- Update ---

Was soll ein dickerer Transistor sein?Damals ging es um die Fläche und den Verbrauch. Deshalb "slower, higher -resistance transistors".

Bei 14nm FF sieht das schon wieder anders aus, die leakage ist nicht so hoch. Da kann man auch wieder "dickere, schnellere" Transistoren einplanen.

Vergrößerst Du die Transistorweite geht mehr Strom durch. Macht Du ihn länger geht weniger Strom durch.

Ansonsten gibt kalte und heiße (mit hoher Einsatzsspannung und geringer).

Länge und Einsatzsspannung schieben den Leckstrom logarithmisch im Verhältnis zum Drivestrom (wichtig für hohe Frequenzen, der Drivestrom arbeitet gegen die Kapazität der Leitung und des Gates). Bei der Weite ist der Zusammenhang einfach linear.

In einem normalen Logik hast Du normalerweise Transistoren mit 3-4 verschiedene Einsatzspannungen und 2-3 und mehr verschiedene Gatelängen zu Auswahl.

Außerdem kann z.B. Dein Inverter (kein npn, sondern da CMOS nur ein gate über n und p, das je nach Spannung die p oder n Seite öffnet) nicht nur aus einem Finger, sondern mehreren parallel bestehen und damit mehr Strom liefern. In einer Standardbibliothek gibt es dann für einen Inverter mal locker 20 verschiedene Ausführungen.

Diese Auswahl an Möglichkeiten ist notwendig. Ein chip funktioniert so, das ein flip flop mit dem ClockSignal sein Eingangsignal auf den Ausgang legt, daraufhin werden die Signale losgeschickt wild in den Gattern verkombiniert und landen beim nächsten flip flop, der sie beim nächsten Clock Signal wieder losschickt.

Dabei muss das Timing so weit stimmen, das am Eingangssignal nicht schon ein Signal zu zeitig ankommt und den noch zu übermittelten Zustand überschreibt. Es darf aber auch nicht zu spät kommen, so das quasi noch das alte Signal am Eingang anliegt. Das Clocksignal selber hat auch noch eine seine Laufzeit über den Chip.

Man wählt möglichst langsame, sparsame Transistoren und verbaut nur an den kritischen Stellen schnelle Gatter nimmt. Wenn man da mal sein Core entwickelt hat, haut man das sicherlich nicht schnell mal über den Haufen.

Mit Hilfe der Fertigung kann man da etwas hier und her schieben z.B. durch global längerer oder kürzer Transistoren, ein nm macht da schon ganz schöne Unterschiede.

Das ist aber nix neues. Der einzige Unterschied ist mit jeder neuen Technologie, das die Transistoren weniger Leckstrom bei gleichen Drivestrom haben bezogen auf die eine normierte Weite.

Zuletzt bearbeitet:

Das wäre mir neu, dass die Transistoren bereits für eine bestimmte Aufgabe geeignet sein müssen (abgesehen von wirklich diskreten Transistoren oder solche für Höchstfrequenzen um die 100GHz).

Die müssen in der CPU oder GPU einfach nur schnell und verlustarm schalten. Die Funktion wird ein paar Ebenen darüber durch die Verdrahtung festgelegt.

Speicher und Logik haben sicherlich gewisse Unterschiede in der Fertigung, was die Verdrahtung angeht.

Und wenn sie schneller schalten sollen, dann sind eine gewisse räumliche Nähe und kurze Leiterbahnen eigentlich eher positiv zu sehen.

Ein Transistor der weniger Leistung treiben muß könnte z.B. anders aussehen als der mehr Leistung treiben muß. Das gleiche Spiel geht auch bei der Frequenz.

Ob allerdings tatsächlich auf so einem Level optimiert wird kann ich nicht sagen.

Was mich wieder an einen Professor vor 20 Jahren erinnert: "In wenigen Jahren werden CPUs die 2GHz erreichen, dann ist rechnerisch Schluss, weil man nicht dichter packen kann, in 10 Jahren haben wird dann überall optische Verbindungen im PC". 20 Jahre später ist von Optik immer noch nichts im PC zu sehen und die Probleme der zu langen Wege hat man durch andere Übertragungsprotokolle gelöst.

Damals hatten CPUs noch keinen Uncore. Ein Core läuft komplett in der gleichen Taktdomäne bzw. Vielfachen oder Teiler, also mit der gleichen Phase.

amdfanuwe

Grand Admiral Special

- Mitglied seit

- 24.06.2010

- Beiträge

- 2.372

- Renomée

- 34

- Details zu meinem Desktop

- Prozessor

- 4200+

- Mainboard

- M3A-H/HDMI

- Kühlung

- ein ziemlich dicker

- Speicher

- 2GB

- Grafikprozessor

- onboard

- Display

- Samsung 20"

- HDD

- WD 1,5TB

- Netzteil

- Extern 100W

- Betriebssystem

- XP, AndLinux

- Webbrowser

- Firefox

- Verschiedenes

- Kaum hörbar

@sciing

Mit dicken Transistoren meinte ich halt welche, die mehr Platz brauchen.

Ich kenns so: npn + pnp

Ist bei mir auch schon 25 Jahre her.

Mit dicken Transistoren meinte ich halt welche, die mehr Platz brauchen.

Haste ne Zeichnung dazu?kein npn, sondern da CMOS nur ein gate über n und p, das je nach Spannung die p oder n Seite öffnet

Ich kenns so: npn + pnp

Ist bei mir auch schon 25 Jahre her.

@sciing

Mit dicken Transistoren meinte ich halt welche, die mehr Platz brauchen.

Haste ne Zeichnung dazu?

Ich kenns so: npn + pnp

Ist bei mir auch schon 25 Jahre her.

Oder hier: https://de.wikipedia.org/wiki/Gegentaktendstufe

IMHO braucht es dafür ein Komplementärpärchen. Aber welchen Anteil haben Transistoren in einer modernen [CG]PU die Gegentaktendstufen bilden?

Zuletzt bearbeitet:

cyrusNGC_224

Grand Admiral Special

- Mitglied seit

- 01.05.2014

- Beiträge

- 5.924

- Renomée

- 117

- Aktuelle Projekte

- POGS, Asteroids, Milkyway, SETI, Einstein, Enigma, Constellation, Cosmology

- Lieblingsprojekt

- POGS, Asteroids, Milkyway

- Meine Systeme

- X6 PII 1090T, A10-7850K, 6x Athlon 5350, i7-3632QM, C2D 6400, AMD X4 PII 810, 6x Odroid U3

- BOINC-Statistiken

Alles wo es um's Treiben größerer Kapazitäten geht, also langer Leitungen. Ich vermute also, in den PHYs jeglicher Schnittstellen.

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Auf der APU ist auch GPU vorhanden, welche in anderer Transistordichte gepackt wird. Wenn du meinst die gesamte Core-IP wird eben völlig unverändert auf die APU übertragen kannst du das ja gerne meinen. Ich denke es besteht die Möglichkeit hier Optimierungen durchzuführen, was ja hirnrissig wäre, wenn man dies nicht tun würde um auf einen höheren Takt zu kommen wenn die iGPU nicht belastet wird. Dazu muss AMD ganz sicher keinen anderen Kern entwickeln, sondern den vorhandenen weiter optimieren, was sie mit großer Wahrscheinlichkeit ebenso tun, wie sie es auch bei den ganzen Bulldozer-APUs auch gemacht haben - was gibt es da anzuzweifeln?Keine Ahnung welche Vorstellung Du hast wenn Du was von dicht schreibst. Aber AMD wird kaum einen weiteren Kern entwickeln mit anderer Cell-Bibliothek usw.

amdfanuwe

Grand Admiral Special

- Mitglied seit

- 24.06.2010

- Beiträge

- 2.372

- Renomée

- 34

- Details zu meinem Desktop

- Prozessor

- 4200+

- Mainboard

- M3A-H/HDMI

- Kühlung

- ein ziemlich dicker

- Speicher

- 2GB

- Grafikprozessor

- onboard

- Display

- Samsung 20"

- HDD

- WD 1,5TB

- Netzteil

- Extern 100W

- Betriebssystem

- XP, AndLinux

- Webbrowser

- Firefox

- Verschiedenes

- Kaum hörbar

Oder hier: https://de.wikipedia.org/wiki/Gegentaktendstufe

IMHO braucht es dafür ein Komplementärpärchen. Aber welchen Anteil haben Transistoren in einer modernen [CG]PU die Gegentaktendstufen bilden?

Ein paar Inverter bzw. NICHT Gatter werden noch vorhanden sein.

Nehmen wir halt ein anderes Grundelement

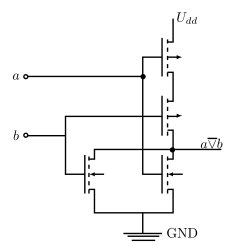

In der nächste Stunden schauen wir uns dann an, wie wir aus ein paar Millionen solcher Elemente theoretisch eine ALU, FPU, MPU, GPU etc. zusammenbauen.

Die Unterschiede ergeben sich, weil es verschiedene Zellbibliotheken sind. Wie gesagt, das tauscht man nicht einfach aus. Du kannst nicht einen Transistor breiter oder schmaller machen, weil es das Timing versaut. Da stecken jahrelange Entwicklung drin. Mag sein das man ein paar critical paths anpasst oder zusätzliche Funktionen aktiviert.Auf der APU ist auch GPU vorhanden, welche in anderer Transistordichte gepackt wird. Wenn du meinst die gesamte Core-IP wird eben völlig unverändert auf die APU übertragen kannst du das ja gerne meinen.

Das meine ich nicht, das weiss ich

--- Update ---

So sieht immer noch aus. Nur wird das einfach als pFET und nFET bezeichnen. Source und Drain sind beim pFET p- und beim nFET n-dotiert. Die Wannen und Kanäle normalerweise komplimentär (es braucht den p-n Übergang der sperrt). Bei FDSOI kann die Wanne (im Bulk unterm BOx) auch mal das gleiche sein und der Kanal (im SOI) ist am besten undotiert.@sciing

Mit dicken Transistoren meinte ich halt welche, die mehr Platz brauchen.

Haste ne Zeichnung dazu?

Ich kenns so: npn + pnp

Ist bei mir auch schon 25 Jahre her.

Zuletzt bearbeitet:

Ähnliche Themen

- Antworten

- 6

- Aufrufe

- 3K

- Antworten

- 22

- Aufrufe

- 4K

- Antworten

- 0

- Aufrufe

- 142K