App installieren

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: This feature may not be available in some browsers.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Bulldozer 2.0 / BDver2: Sepang, Terramar, Komodo, Trinity, Vishera

Opteron

Redaktion

☆☆☆☆☆☆

Nachdem mittlerweile erste Infos der Bulldozer Nachfolgegeneration samt Zeitplan bekannt wurden, macht ein Sammelthread Sinn.

Jeder der einen neuenn sinnvollen Link hat bitte unter Links samt kurzer Beschreibung hinzufügen.

[H4]Steamroller[/H4]

Eventueller APU Codename: http://citavia.blog.de/2010/12/10/brazos-opencl-steamroller-and-other-stuff-10160610/

Von der Logik her könnte es aber auch der Codename der BDver3 Architektur sein, würde Sinn von den Namen her machen:

BDVer1: Bulldozer (32nm)

BDVer2: Piledriver (32nm)

BDVer3: Steamroller (wäre dann laut der letzten, inoffiziellen Roadmap wohl die Basis für die 28nm Serverchips)

"BDver3" wurde aber bisher aber noch nirgends erwähnt, pure Spekulation meinerseits (Opteron)

[H4]Viperfish[/H4]

Eventueller Codename fürs Server DIE, da zusammen mit Trinity genannt: http://www.planet3dnow.de/vbulletin/showpost.php?p=4372056&postcount=25

[H4]Vishera[/H4]

Laut xbitlabs Bericht Ersatz für den gestrichenen Komodo Prozessor (siehe oben unter 1.3).

Unterschiede:

Keine PCIe Integration und kein Sockel FMx, stattdessen soll doch noch der altbewährte Sockel AM3+ Anwendung finden.

Frühere Spekulationen gab es dazu schon bei 4Gamer, allerdings lieferten die Leute dort auch noch eine mit Fehlern übersäte Pseudoroadmap mit, so dass es wenig glaubwürdig erschien.

Zusammenfassung dazu hier im Thread in Posting #147.

http://blogs.amd.com/fusion/2010/11/09/simply-put-it’s-all-about-velocity/dt-roadmap_with-footnote/

Quelle: http://pcper.com/news/Graphics-Cards/AFDS11-Upcoming-Trinity-APU-will-use-VLIW4-Cayman-Architecture

Quelle: http://mb.zol.com.cn/240/2405453.html

Quelle: http://www.donanimhaber.com/islemci...MDnin-2012-model-mobil-Fusion-islemcileri.htm

Quelle: http://www.computerbase.de/news/har.../2011/august/server-roadmap-von-amd-bis-2013/

Hardwareluxx: Trinity reiht sich in HD7000-Familie ein

BMI: Bit Manipulation Instructions

TBM: Trailing Bit Manipulation

FMA3: three operand FMA instructions

Gesammelt hier zu finden: http://citavia.blog.de/2010/10/21/signs-of-bulldozer-2-and-llano-9726240/

------

Ich bitte um rege Anteilnahme

Jeder der einen neuenn sinnvollen Link hat bitte unter Links samt kurzer Beschreibung hinzufügen.

BDver2 CPU Typen

Bisher sind 3 Typen für unterschiedliche Sockel und Segmente bekannt. Die unten genauer aufgeschlüsselt werden. Allgemein kann man für Bulldozer 2.0 folgende Verbesserungen gegenüber der ersten Generation aufführen:- Neue Befehlssätze: BDver2 wird Intels FMA3 Befehle sowie TBM und BMI unterstützen (siehe Datenblätter)

- Höhere Integration: Ähnlich wie schon bei den APUs wird nun auch bei den CPUs ein PCIe Interface integriert.

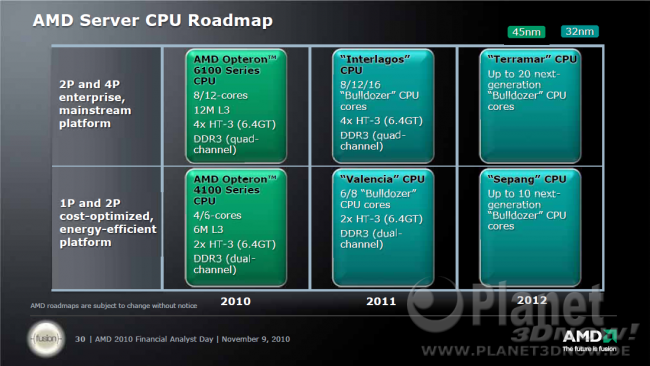

Sepang

- 2P Server CPU

- bis zu 10 next Generation Bulldozer-Cores

- 2-Sockel-Systeme

- Sockel C2012 (Zahl=Pincount oder Platzhalter?)

- 3-Kanal Speicherinterface

- integriertes PCIe Gen3

- Geplant für 2012

Terramar

- 2P-4P Server CPU

- bis zu 20 next Generation Bulldozer-Cores

- 2-4 Sockel-Systeme

- Sockel G2012 (Zahl=Pincount oder Platzhalter?)

- 4-Kanal Speicherinterface

- integriertes PCIe Gen3

- Geplant für 2012

- vermutlich MCM aus zwei Sepang DIEs

Komodo

- 1P Server und High Performance Desktop CPU

- bis zu 10 next Generation Bulldozer-Cores, Codename Piledriver (siehe auch: http://www.planet3dnow.de/vbulletin/showthread.php?p=4354768#post4354768)

- Desktopversion

- Sockel FMx/FM2 Plattform -> Nicht mehr AM3 kompatibel

- Geplant für 2012

- - laut Gerüchten eventuell ersetzt durch Vishera, siehe Punkt 3.2.1 -

Dublin

- 28nm

- bis zu 20 next Generation Bulldozer-Cores

- geplant für 2013

- Sockel G2012 / Porto Plattform

Macau

- bis zu 10 next Generation Bulldozer-Cores

- 28nm

- geplant für 2013

- Sockel C2012 / Luxembourg Platform

BDver2 APU Typen

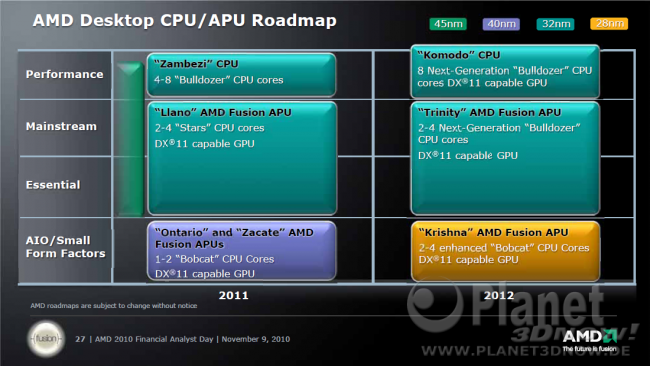

Trinity

- Notebook- und Desktop-APU

- 32nm SOI

- jeweils Mainstream und High Performance-Level

- 2 bis 4 next Generation Bulldozer-Cores, Codename Piledriver

- Sockel FMx/FM2

- DirectX® 11 GPU im VLIW4-Design

- Theoretische (GP)GPU-Leistung (GFLOPs) "bis zu" 50% höher als bei Llano

- Geplant für 2012

Noch unzugeordnete Codenamen

Codenamen aus sicherer Quelle

Hier ist Platz für alle sicheren, aber inoffiziellen Codenamen, z.B. aus Compilerkommentaren. Die Compilerbauer haben immer Zugriff auf NDA Material, sodass deren Kommentare 100% stimmen sollten.[H4]Steamroller[/H4]

Eventueller APU Codename: http://citavia.blog.de/2010/12/10/brazos-opencl-steamroller-and-other-stuff-10160610/

Von der Logik her könnte es aber auch der Codename der BDver3 Architektur sein, würde Sinn von den Namen her machen:

BDVer1: Bulldozer (32nm)

BDVer2: Piledriver (32nm)

BDVer3: Steamroller (wäre dann laut der letzten, inoffiziellen Roadmap wohl die Basis für die 28nm Serverchips)

"BDver3" wurde aber bisher aber noch nirgends erwähnt, pure Spekulation meinerseits (Opteron)

[H4]Viperfish[/H4]

Eventueller Codename fürs Server DIE, da zusammen mit Trinity genannt: http://www.planet3dnow.de/vbulletin/showpost.php?p=4372056&postcount=25

Inoffizielle Codenamen aus der Gerüchteküche

Hier ist Platz für eventuelle Codenamen aus dubiosen Quellen.[H4]Vishera[/H4]

Laut xbitlabs Bericht Ersatz für den gestrichenen Komodo Prozessor (siehe oben unter 1.3).

Unterschiede:

Keine PCIe Integration und kein Sockel FMx, stattdessen soll doch noch der altbewährte Sockel AM3+ Anwendung finden.

Frühere Spekulationen gab es dazu schon bei 4Gamer, allerdings lieferten die Leute dort auch noch eine mit Fehlern übersäte Pseudoroadmap mit, so dass es wenig glaubwürdig erschien.

Zusammenfassung dazu hier im Thread in Posting #147.

Roadmaps

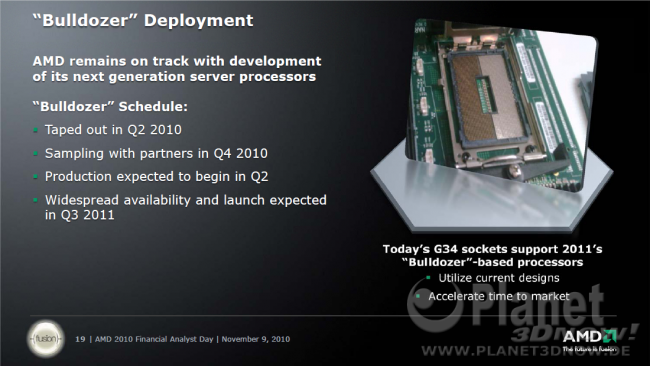

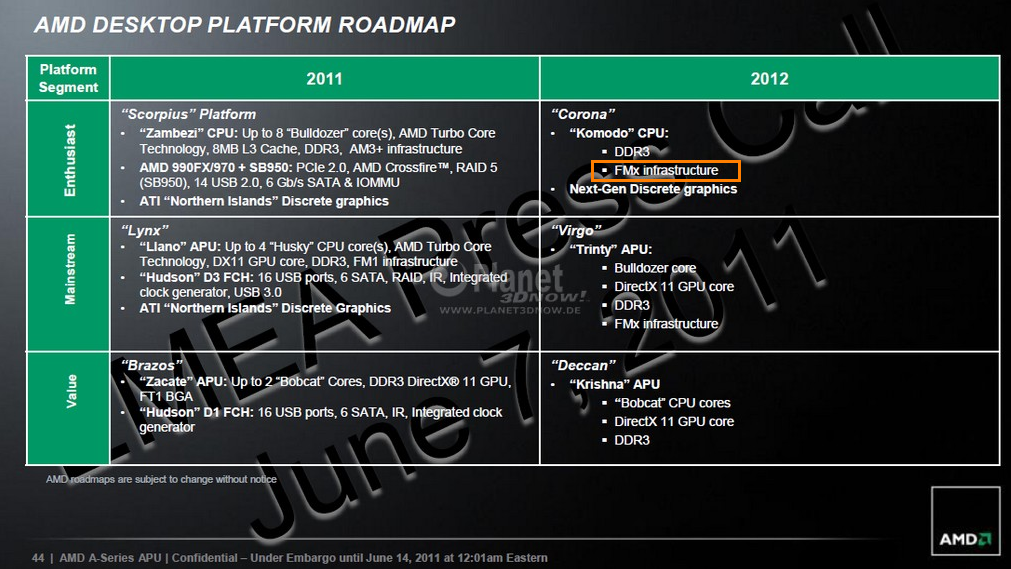

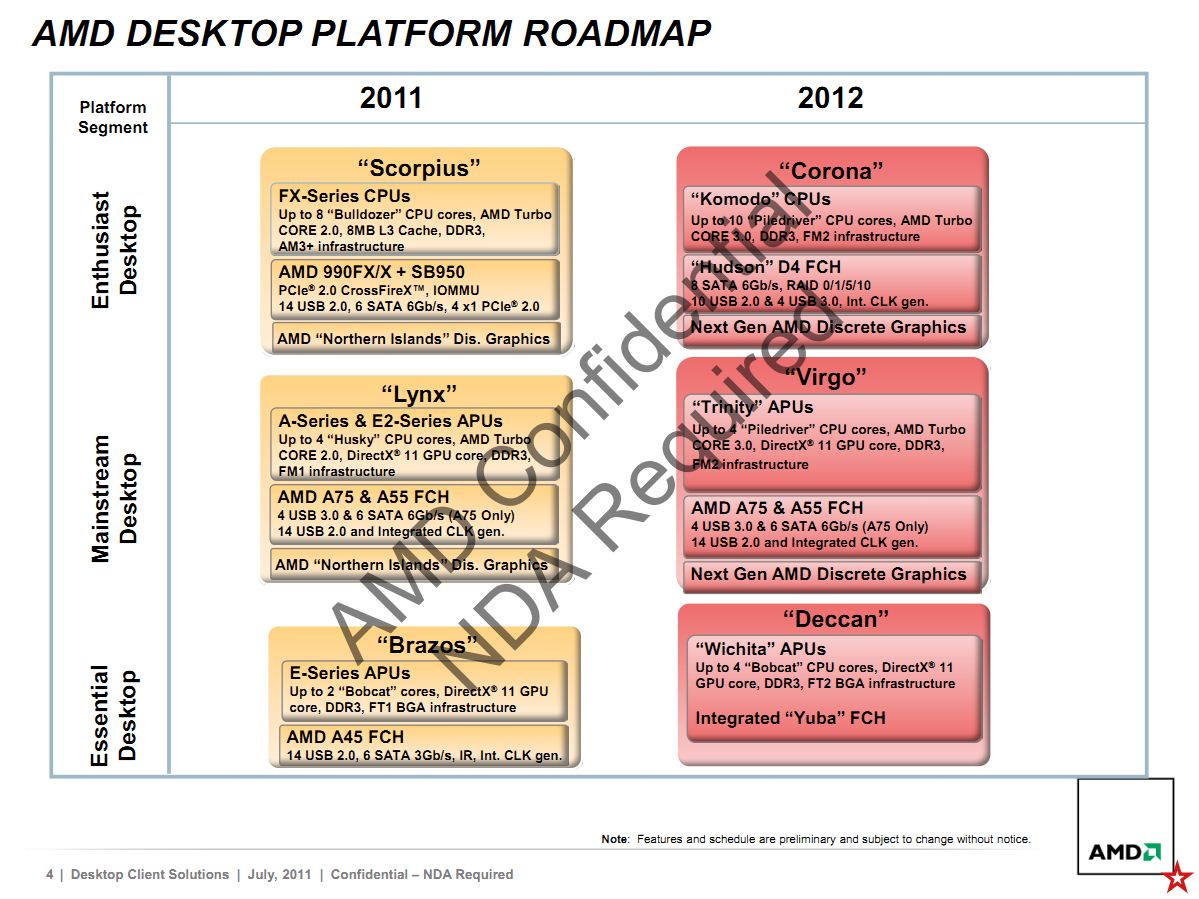

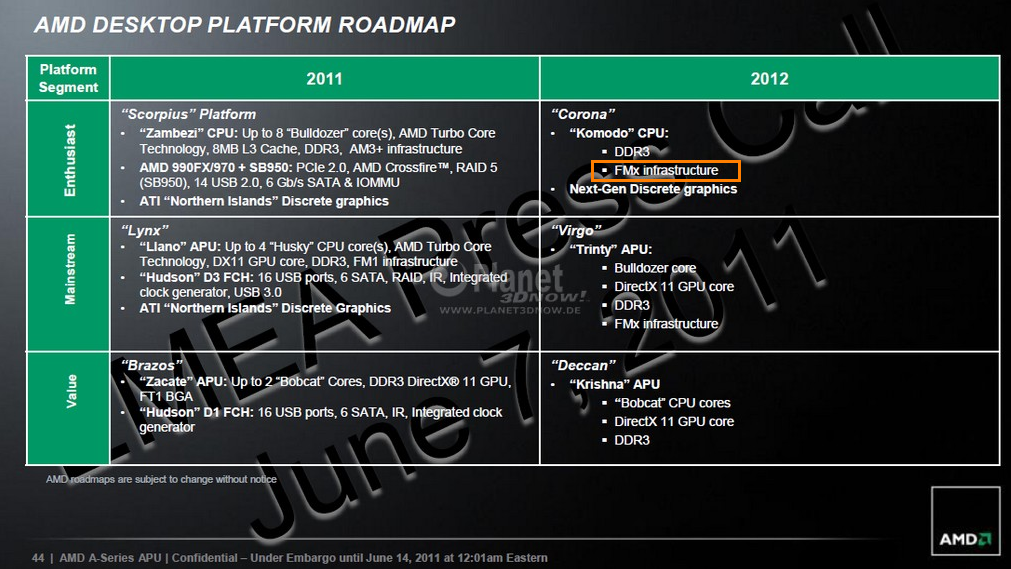

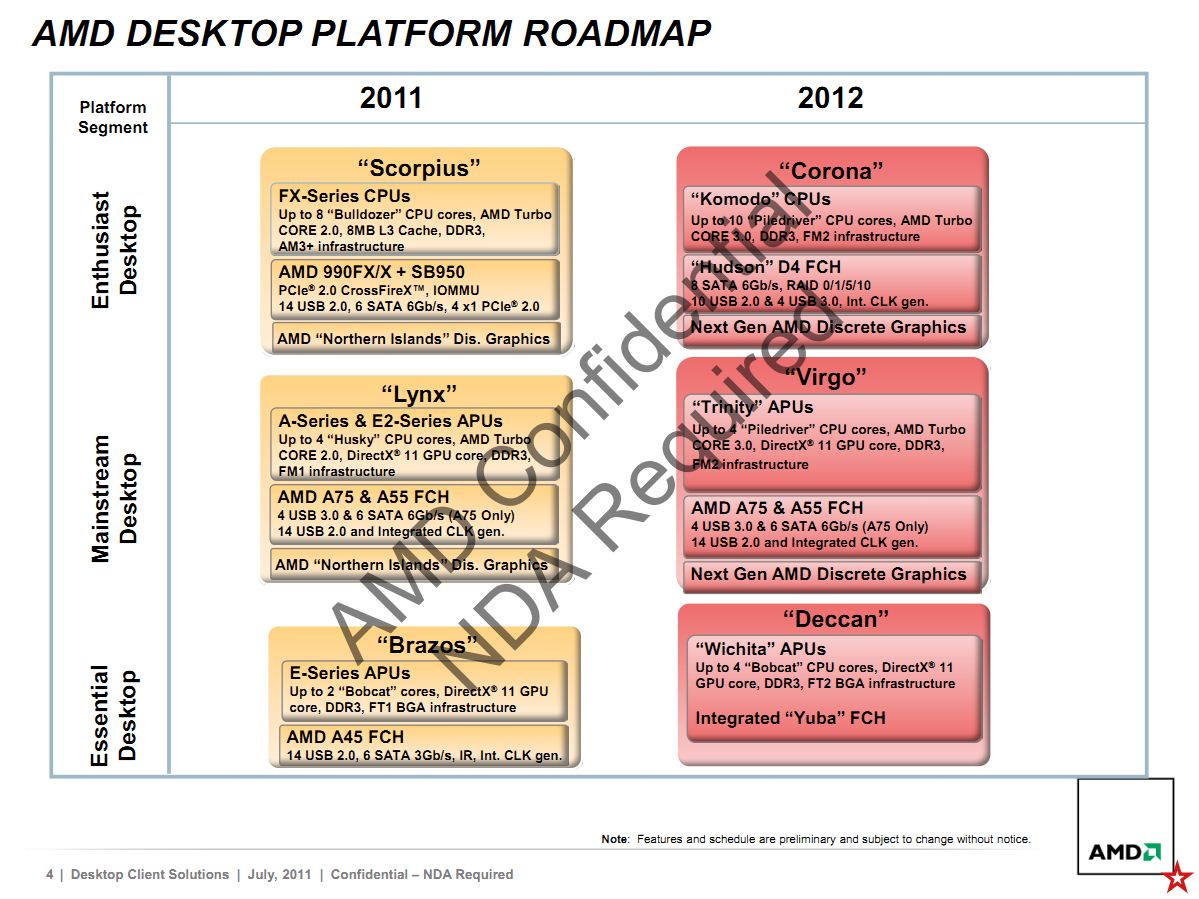

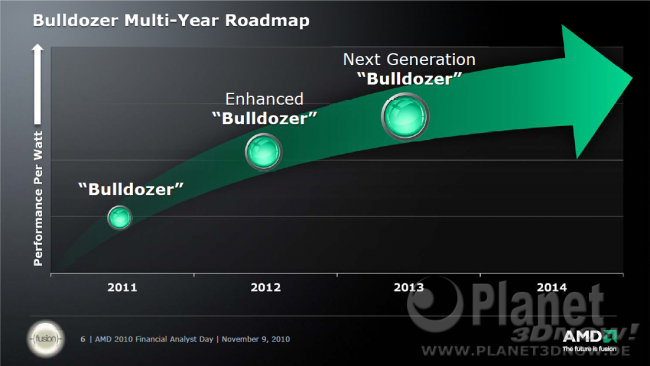

9. November 2010 (Analyst Day)

März 2011 (Blog)

http://blogs.amd.com/fusion/2010/11/09/simply-put-it’s-all-about-velocity/dt-roadmap_with-footnote/

Juni 2011 - AFDS

Quelle: http://pcper.com/news/Graphics-Cards/AFDS11-Upcoming-Trinity-APU-will-use-VLIW4-Cayman-Architecture

Juli 2011 (Inoffiziell, unbestätigt )

Quelle: http://mb.zol.com.cn/240/2405453.html

Aug 2011 (Inoffiziell, unbestätigt )

Quelle: http://www.donanimhaber.com/islemci...MDnin-2012-model-mobil-Fusion-islemcileri.htm

Serverroadmap April 2011

Quelle: http://www.computerbase.de/news/har.../2011/august/server-roadmap-von-amd-bis-2013/

Links

Allgemeines und Langfristiges

Dresdenboys BlogSpezielle Spekulationsartikel und Meldungen

Hardwareluxx: Trinity reiht sich in HD7000-Familie ein

Testberichte

Datenblätter z.B: Befehlssatzerweiterungen, Compilerpatches etc. pp.

BMI: Bit Manipulation Instructions

TBM: Trailing Bit Manipulation

FMA3: three operand FMA instructions

Gesammelt hier zu finden: http://citavia.blog.de/2010/10/21/signs-of-bulldozer-2-and-llano-9726240/

Sonstiges

------

Ich bitte um rege Anteilnahme

Zuletzt bearbeitet:

Opteron

Redaktion

☆☆☆☆☆☆

Jein, nur der "G" Sockel ist für MCMs, C ist wie jetzt schon C32 der single DIE Sockel, sieht man ja an den Kernen, 10 Sepang <> 20 Terramar -> Terrarmar = 2xSepangIch denke mit den Sockeln C/G2012 hats folgendes auf sich:

denn beim Komodo steht nirgends ein Sockel dazu.

- Es sind Server-Sockel

- Für MCMs

- vgl. Sockel G34

- die 2012 gibt nicht den Pincount wieder sondern ist nur als Platzhalter gedacht denn 2012 schon wieder einen neuen Sockel in dem Markt?

Und da er keine APU ist denke ich er soll auf "AM3+" landen auf welchen ja auch die aktuellen AM3-CPUs lauffähig sein sollen. Entsprechend bezweifle ich auch einen 3 oder 4-Kanal IMC beim Komodo

2012 ist sicherlich ein Platzhalter im Form der Jahreszahl

ciao

Alex

Zuletzt bearbeitet:

Onkel_Dithmeyer

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 22.04.2008

- Beiträge

- 12.949

- Renomée

- 4.038

- Standort

- Zlavti

- Aktuelle Projekte

- Universe@home

- Lieblingsprojekt

- Universe@home

- Meine Systeme

- cd0726792825f6f563c8fc4afd8a10b9

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- Ryzen 9 3900X @4000 MHz//1,15V

- Mainboard

- MSI X370 XPOWER GAMING TITANIUM

- Kühlung

- Custom Wasserkühlung vom So. G34

- Speicher

- 4x8 GB @ 3000 MHz

- Grafikprozessor

- Radeon R9 Nano

- Display

- HP ZR30W & HP LP3065

- SSD

- 2 TB ADATA

- Optisches Laufwerk

- LG

- Soundkarte

- Im Headset

- Gehäuse

- Xigmatek

- Netzteil

- BeQuiet Dark Pro 9

- Tastatur

- GSkill KM570

- Maus

- GSkill MX780

- Betriebssystem

- Ubuntu 20.04

- Webbrowser

- Firefox Version 94715469

- Internetanbindung

- ▼100 Mbit ▲5 Mbit

Die Folien wiedersprechen sich teilweise. In den oben eingebundenen Folien steht Next Generation BD für 2012. Auf dieser Folie aber:

Steht für 2012 Enhanced BD und erst 2013 Next Generation BD ...

edit:

Ich könnte mir vorstellen, dass mit Enhanced BD im Serverbereich BD-CPUs mit 2 Dies bedeutet.

Steht für 2012 Enhanced BD und erst 2013 Next Generation BD ...

edit:

Ich könnte mir vorstellen, dass mit Enhanced BD im Serverbereich BD-CPUs mit 2 Dies bedeutet.

Zuletzt bearbeitet:

Opteron

Redaktion

☆☆☆☆☆☆

Die Folien wiedersprechen sich teilweise. In den oben eingebundenen Folien steht Next Generation BD für 2012. Auf dieser Folie aber:

Steht für 2012 Enhanced BD und erst 2013 Next Generation BD ...

Jo das ist ein bisschen komisch, JF hatte das Thema auf Nachfrage schon angeschnitten:

http://www.semiaccurate.com/forums/showpost.php?p=81781&postcount=12Enhanced BD and next gen BD are only labels, not product names. Think of that as shorthand for "whatever comes next."

Sollte also so sein, dass das eine n+1 und das andre n+2 ist, nichts weiter. Natürlich trotzdem sehr unglücklichlich, wenns nicht passt, macht nen schlechten Eindruck -> schlechtes Marketing

Ich frag mal gleich hinterher, was das nun soll ^^

Nö, da kommt ja schon Interlagos.edit:

Ich könnte mir vorstellen, dass mit Enhanced BD im Serverbereich BD-CPUs mit 2 Dies bedeutet.

ciao

Alex

Onkel_Dithmeyer

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 22.04.2008

- Beiträge

- 12.949

- Renomée

- 4.038

- Standort

- Zlavti

- Aktuelle Projekte

- Universe@home

- Lieblingsprojekt

- Universe@home

- Meine Systeme

- cd0726792825f6f563c8fc4afd8a10b9

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- Ryzen 9 3900X @4000 MHz//1,15V

- Mainboard

- MSI X370 XPOWER GAMING TITANIUM

- Kühlung

- Custom Wasserkühlung vom So. G34

- Speicher

- 4x8 GB @ 3000 MHz

- Grafikprozessor

- Radeon R9 Nano

- Display

- HP ZR30W & HP LP3065

- SSD

- 2 TB ADATA

- Optisches Laufwerk

- LG

- Soundkarte

- Im Headset

- Gehäuse

- Xigmatek

- Netzteil

- BeQuiet Dark Pro 9

- Tastatur

- GSkill KM570

- Maus

- GSkill MX780

- Betriebssystem

- Ubuntu 20.04

- Webbrowser

- Firefox Version 94715469

- Internetanbindung

- ▼100 Mbit ▲5 Mbit

Nö, da kommt ja schon Interlagos.

Kommt der schon 2012 oder 2013?

Opteron

Redaktion

☆☆☆☆☆☆

Der kommt 2011Kommt der schon 2012 oder 2013?

.

EDIT :

.

JF hat geantwortet, und zwar damit, dass er nichts sagen darf und es nicht seine Slides wären.

Supi ... mal wieder tolle Organisation bei AMD ...

Zuletzt bearbeitet:

Opteron

Redaktion

☆☆☆☆☆☆

Der Platz für den 6ten Core geht vermutlich für PCIe. Je nachdem, wieviel Lanes man anbieten will, braucht das schon DIE Fläche. Dann noch der Triple MC und noch plus X .. wird schon irgendwie passen ^^Komisch.

10 Integer-Units, das würde heissen 5 Bulldozer-Module.

Ich tu mir gerade ganz schwer die auf einem Die zu platzieren.

Ich hätte fest mit 6 gerechnet, dann wäre man wieder beim Sprung Shanghai -> Istanbul.

Vielleicht ja endlich auch T-RAM ^^

Dresdenboy

Redaktion

☆☆☆☆☆☆

Ich habe schonmal die gesicherten Befehlssatzerweiterungen eingearbeitet. Man könnte hier noch ASF anbringen.

Onkel_Dithmeyer

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 22.04.2008

- Beiträge

- 12.949

- Renomée

- 4.038

- Standort

- Zlavti

- Aktuelle Projekte

- Universe@home

- Lieblingsprojekt

- Universe@home

- Meine Systeme

- cd0726792825f6f563c8fc4afd8a10b9

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- Ryzen 9 3900X @4000 MHz//1,15V

- Mainboard

- MSI X370 XPOWER GAMING TITANIUM

- Kühlung

- Custom Wasserkühlung vom So. G34

- Speicher

- 4x8 GB @ 3000 MHz

- Grafikprozessor

- Radeon R9 Nano

- Display

- HP ZR30W & HP LP3065

- SSD

- 2 TB ADATA

- Optisches Laufwerk

- LG

- Soundkarte

- Im Headset

- Gehäuse

- Xigmatek

- Netzteil

- BeQuiet Dark Pro 9

- Tastatur

- GSkill KM570

- Maus

- GSkill MX780

- Betriebssystem

- Ubuntu 20.04

- Webbrowser

- Firefox Version 94715469

- Internetanbindung

- ▼100 Mbit ▲5 Mbit

Der kommt 2011

Irgendwie war ich der Meinung wir hätten schon 2011

Vermutlich Wunschdenken

Vermutlich Wunschdenken ![Augen rollen (sarkastisch) :] :]](https://www.planet3dnow.de/vbulletin/images/smilies/rolleyes.gif)

Dresdenboy

Redaktion

☆☆☆☆☆☆

Und zu Weihnachten ein Zambezi-System?Irgendwie war ich der Meinung wir hätten schon 2011Vermutlich Wunschdenken

![Augen rollen (sarkastisch) :] :]](https://www.planet3dnow.de/vbulletin/images/smilies/rolleyes.gif)

Onkel_Dithmeyer

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 22.04.2008

- Beiträge

- 12.949

- Renomée

- 4.038

- Standort

- Zlavti

- Aktuelle Projekte

- Universe@home

- Lieblingsprojekt

- Universe@home

- Meine Systeme

- cd0726792825f6f563c8fc4afd8a10b9

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- Ryzen 9 3900X @4000 MHz//1,15V

- Mainboard

- MSI X370 XPOWER GAMING TITANIUM

- Kühlung

- Custom Wasserkühlung vom So. G34

- Speicher

- 4x8 GB @ 3000 MHz

- Grafikprozessor

- Radeon R9 Nano

- Display

- HP ZR30W & HP LP3065

- SSD

- 2 TB ADATA

- Optisches Laufwerk

- LG

- Soundkarte

- Im Headset

- Gehäuse

- Xigmatek

- Netzteil

- BeQuiet Dark Pro 9

- Tastatur

- GSkill KM570

- Maus

- GSkill MX780

- Betriebssystem

- Ubuntu 20.04

- Webbrowser

- Firefox Version 94715469

- Internetanbindung

- ▼100 Mbit ▲5 Mbit

Und zu Weihnachten ein Zambezi-System?

Habe ich grad mir Tränen in den Augen von der Wunschliste gestrichen

@T

Im Spekulationsthread 2011 wurde ein Link gepostet auf der ich eine schöne Übersicht über die aktuellen Prozessoren, BD1 und auch BD2.

http://pc.watch.impress.co.jp/img/pcw/docs/405/860/html/15.jpg.html

Die deckt soweit ganz gut mit unseren Daten.

Lynxeye

Admiral Special

- Mitglied seit

- 26.10.2007

- Beiträge

- 1.107

- Renomée

- 60

- Standort

- Sachsen

- Mein Laptop

- Lifebook T1010

- Details zu meinem Desktop

- Prozessor

- AMD FX 8150

- Mainboard

- Gigabyte GA-970A-UD3

- Kühlung

- Zalman Reserator 1 Plus

- Speicher

- 4x8GB DDR3-1600 G.Skill Ripjaws

- Grafikprozessor

- ASUS ENGTX 260

- Display

- 19" AOC LM928 (1280x1024), V7 21" (1680x1050)

- HDD

- Crucial M4 128GB, 500GB WD Caviar 24/7 Edition

- Optisches Laufwerk

- DVD Multibrenner LG GSA-4167B

- Soundkarte

- Creative Audigy 2 ZS

- Gehäuse

- Amacrox Spidertower

- Netzteil

- Enermax Liberty 500W

- Betriebssystem

- Fedora 17

- Webbrowser

- Firefox

- Verschiedenes

- komplett Silent durch passive Wasserkühlug

Ist zwar hoch spekulativ von mir, würde aber evtl. zum 2013er "next Generation Bulldozer" passen:

Das AMD Operating System Research Center in Dresden hat in den letzten Monaten einiges zum Thema Transactional Memory publiziert, inklusive Verweisen auf Simulationen mit Erkenntnissen, wie das ganze in Hardware umgesetzt werden kann. Das könnte ganz gut zur Bulldozer Architektur passen und wäre auch vom Zeitplan her realistisch.

Das AMD Operating System Research Center in Dresden hat in den letzten Monaten einiges zum Thema Transactional Memory publiziert, inklusive Verweisen auf Simulationen mit Erkenntnissen, wie das ganze in Hardware umgesetzt werden kann. Das könnte ganz gut zur Bulldozer Architektur passen und wäre auch vom Zeitplan her realistisch.

Ge0rgy

Grand Admiral Special

- Mitglied seit

- 14.07.2006

- Beiträge

- 4.322

- Renomée

- 82

- Mein Laptop

- Lenovo Thinkpad X60s

- Details zu meinem Desktop

- Prozessor

- Phenom II 955 BE

- Mainboard

- DFI LanParty DK 790FXB-M3H5

- Kühlung

- Noctua NH-U12P

- Speicher

- 4GB OCZ Platinum DDR1600 7-7-7 @ 1333 6-6-6

- Grafikprozessor

- Radeon 4850 1GB

- HDD

- Western Digital Caviar Black 1TB

- Netzteil

- Enermax Modu 525W

- Betriebssystem

- Linux, Vista x64

- Webbrowser

- Firefox 3.5

Ist das eigentlich ein vertipper dass Sepang Triple-Channel speicher kriegen soll und Terramar als Sepang x 2 dann nur Quadchannel aufweisen kann? - Damit hätte Terramar pro core weniger Speicherbandbreite zur Verfügung als sein kleiner Bruder...

Aktuell ist das doch eine simple verdopplung, also dass Istanbul Dualchannel hat und als MCM dann halt 2 mal Dualchannel = Quad...

Aktuell ist das doch eine simple verdopplung, also dass Istanbul Dualchannel hat und als MCM dann halt 2 mal Dualchannel = Quad...

Opteron

Redaktion

☆☆☆☆☆☆

Ne das kann schon stimmen. Da gibts wohl ein paar Fälle, die hochgetaktete Kerne und viel RAM-Bandbreite benötigen. So ein 3ter RAMKontroller kostet vermutlich eh nicht viel und kann außerdem noch als Redundanz zweckentfremdet werden ^^Ist das eigentlich ein vertipper dass Sepang Triple-Channel speicher kriegen soll und Terramar als Sepang x 2 dann nur Quadchannel aufweisen kann? - Damit hätte Terramar pro core weniger Speicherbandbreite zur Verfügung als sein kleiner Bruder...

Aktuell ist das doch eine simple verdopplung, also dass Istanbul Dualchannel hat und als MCM dann halt 2 mal Dualchannel = Quad...

Dresdenboy

Redaktion

☆☆☆☆☆☆

Das könnte auch wieder ein Tradeoff sein. Die doppelte Zahl Kerne im Terramar läuft vermutlich eher mit ~70% des Taktes. Die für die gesteigerte Rechenleistung (ungeachtet der ebenfalls verdoppelten Caches) im gleichen Maße benötigte Speicherbandbreite läge bei +40%. Der 4. Kanal brächte +33% bei insgesamt 2/3 der Energie von 6 Speicherkanälen...Ist das eigentlich ein vertipper dass Sepang Triple-Channel speicher kriegen soll und Terramar als Sepang x 2 dann nur Quadchannel aufweisen kann? - Damit hätte Terramar pro core weniger Speicherbandbreite zur Verfügung als sein kleiner Bruder...

Aktuell ist das doch eine simple verdopplung, also dass Istanbul Dualchannel hat und als MCM dann halt 2 mal Dualchannel = Quad...

Ge0rgy

Grand Admiral Special

- Mitglied seit

- 14.07.2006

- Beiträge

- 4.322

- Renomée

- 82

- Mein Laptop

- Lenovo Thinkpad X60s

- Details zu meinem Desktop

- Prozessor

- Phenom II 955 BE

- Mainboard

- DFI LanParty DK 790FXB-M3H5

- Kühlung

- Noctua NH-U12P

- Speicher

- 4GB OCZ Platinum DDR1600 7-7-7 @ 1333 6-6-6

- Grafikprozessor

- Radeon 4850 1GB

- HDD

- Western Digital Caviar Black 1TB

- Netzteil

- Enermax Modu 525W

- Betriebssystem

- Linux, Vista x64

- Webbrowser

- Firefox 3.5

Wisst ihr was mir bei "Komodo" zuerst einfällt?

Limited Waranty

Limited Waranty

Opteron

Redaktion

☆☆☆☆☆☆

Was mir beim Thema Speicherbandbreite auch wieder einfällt ist eDRAM. IBM hats ja erst im Power7 @45nm verbaut, für 32nm hat man bereits 2009 nen "Durchbruch" vermeldet:Das könnte auch wieder ein Tradeoff sein. Die doppelte Zahl Kerne im Terramar läuft vermutlich eher mit ~70% des Taktes. Die für die gesteigerte Rechenleistung (ungeachtet der ebenfalls verdoppelten Caches) im gleichen Maße benötigte Speicherbandbreite läge bei +40%. Der 4. Kanal brächte +33% bei insgesamt 2/3 der Energie von 6 Speicherkanälen...

http://www.theinquirer.net/inquirer/news/1534135/ibm-develops-32nm-dynamic-memorySo far IBM has made a test chip with this embedded dynamic random access memory (eDRAM) technology that it says contains the industry's smallest memory cells.

The company claims it offers higher density, speed and capacity better than conventional on-chip static random access memory (SRAM) that has been announced in 32nm and 22nm technology. It thinks its eDRAM is comparable to what would be expected of SRAM produced on a 15nm process, three technology generations ahead of chips in volume production today.

IBM's eDRAM cell is twice as dense as any announced 22nm embedded SRAM cell and up to four times as dense as any comparable 32nm embedded SRAM in the industry.

http://www.eetimes.com/electronics-news/4196326/IBM-makes-claims-for-32-nm-eDRAM-on-SOI

Entweder das, oder das übliche T-RAM Gespenst ... irgendwas Neues müssen sie bei nem überarbeiteten 32nm Prozess eigentlich einbauen. Durch die kleinen eDRAM Zellgrößen wäre man mit 22nm konkurrenzfähig. Frage ist, obs sogar für den L2 taugen würde.

eDRAM Präsentation:

http://www.bloobble.com/broadband-presentations/presentations?itemid=3255

ciao

Alex

Zuletzt bearbeitet:

Opteron

Redaktion

☆☆☆☆☆☆

Gerade gefunden:

Die wissen wohl bei AMD selbst noch nicht, wieviel Kerne das werden

</pre>

http://ir.amd.com/phoenix.zhtml?c=74093&p=irol-newsArticle&ID=1494197&highlight=-- "Komodo": a 32nm CPU featuring up to 10 AMD "Bulldozer" CPU cores

designed for high-performance and enthusiast desktops;

Die wissen wohl bei AMD selbst noch nicht, wieviel Kerne das werden

</pre>

WindHund

Grand Admiral Special

- Mitglied seit

- 30.01.2008

- Beiträge

- 12.236

- Renomée

- 538

- Standort

- Im wilden Süden (0711)

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- NumberFields@home

- Lieblingsprojekt

- none, try all

- Meine Systeme

- RYZEN R9 3900XT @ ASRock Taichi X570 & ASUS RX Vega64

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5950X

- Mainboard

- ASRock 570X Taichi P5.05 Certified

- Kühlung

- AlphaCool Eisblock XPX, 366x40mm Radiator 6l Brutto m³

- Speicher

- 2x 16 GiB DDR4-3600 CL26 Kingston (Dual Rank, unbuffered ECC)

- Grafikprozessor

- 1x ASRock Radeon RX 6950XT Formula OC 16GByte GDDR6 VRAM

- Display

- SAMSUNG Neo QLED QN92BA 43" up to 4K@144Hz FreeSync PP HDR10+

- SSD

- WD_Black SN850 PCI-Express 4.0 NVME

- HDD

- 3 Stück

- Optisches Laufwerk

- 1x HL-DT-ST BD-RE BH10LS30 SATA2

- Soundkarte

- HD Audio (onboard)

- Gehäuse

- SF-2000 Big Tower

- Netzteil

- Corsair RM1000X (80+ Gold)

- Tastatur

- Habe ich

- Maus

- Han I

- Betriebssystem

- Windows 10 x64 Professional (up to date!)

- Webbrowser

- @Chrome.Google & Edge Chrome

Hallo zusammen,

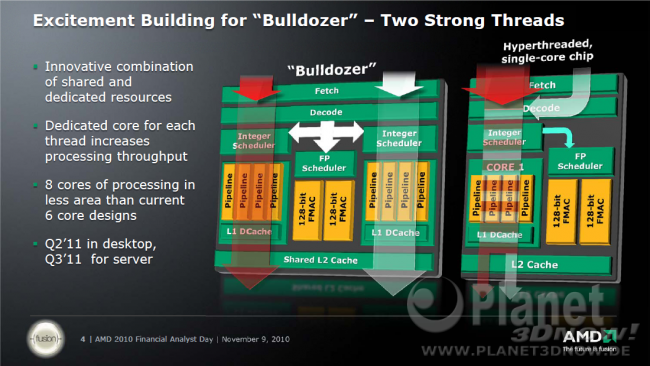

kleine Frage am Rande, wie ist das erste Bild zu deuten "two strong Threads"?

Und warum kann ein Kern (von 2 in einem Modul) 2 Threads abarbeiten, hat der BD dann auch Hyperthreading?

Oder ist das evt der Turbo?

MfG

kleine Frage am Rande, wie ist das erste Bild zu deuten "two strong Threads"?

Und warum kann ein Kern (von 2 in einem Modul) 2 Threads abarbeiten, hat der BD dann auch Hyperthreading?

Oder ist das evt der Turbo?

MfG

Onkel_Dithmeyer

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 22.04.2008

- Beiträge

- 12.949

- Renomée

- 4.038

- Standort

- Zlavti

- Aktuelle Projekte

- Universe@home

- Lieblingsprojekt

- Universe@home

- Meine Systeme

- cd0726792825f6f563c8fc4afd8a10b9

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- Ryzen 9 3900X @4000 MHz//1,15V

- Mainboard

- MSI X370 XPOWER GAMING TITANIUM

- Kühlung

- Custom Wasserkühlung vom So. G34

- Speicher

- 4x8 GB @ 3000 MHz

- Grafikprozessor

- Radeon R9 Nano

- Display

- HP ZR30W & HP LP3065

- SSD

- 2 TB ADATA

- Optisches Laufwerk

- LG

- Soundkarte

- Im Headset

- Gehäuse

- Xigmatek

- Netzteil

- BeQuiet Dark Pro 9

- Tastatur

- GSkill KM570

- Maus

- GSkill MX780

- Betriebssystem

- Ubuntu 20.04

- Webbrowser

- Firefox Version 94715469

- Internetanbindung

- ▼100 Mbit ▲5 Mbit

Ich denke mal, dass du das Bild falsch interpretierst. Das oll ein vergleich der Architekturen sein. Ein mal bulldowzer, der 2 Threats bearbeitet in einem !Modul! und ein mal ein Kern mit HT, der 2 threats zerstückelt nacheinander bearbeitet.

WindHund

Grand Admiral Special

- Mitglied seit

- 30.01.2008

- Beiträge

- 12.236

- Renomée

- 538

- Standort

- Im wilden Süden (0711)

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- NumberFields@home

- Lieblingsprojekt

- none, try all

- Meine Systeme

- RYZEN R9 3900XT @ ASRock Taichi X570 & ASUS RX Vega64

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5950X

- Mainboard

- ASRock 570X Taichi P5.05 Certified

- Kühlung

- AlphaCool Eisblock XPX, 366x40mm Radiator 6l Brutto m³

- Speicher

- 2x 16 GiB DDR4-3600 CL26 Kingston (Dual Rank, unbuffered ECC)

- Grafikprozessor

- 1x ASRock Radeon RX 6950XT Formula OC 16GByte GDDR6 VRAM

- Display

- SAMSUNG Neo QLED QN92BA 43" up to 4K@144Hz FreeSync PP HDR10+

- SSD

- WD_Black SN850 PCI-Express 4.0 NVME

- HDD

- 3 Stück

- Optisches Laufwerk

- 1x HL-DT-ST BD-RE BH10LS30 SATA2

- Soundkarte

- HD Audio (onboard)

- Gehäuse

- SF-2000 Big Tower

- Netzteil

- Corsair RM1000X (80+ Gold)

- Tastatur

- Habe ich

- Maus

- Han I

- Betriebssystem

- Windows 10 x64 Professional (up to date!)

- Webbrowser

- @Chrome.Google & Edge Chrome

Gut möglich, daher frage ich ja!Ich denke mal, dass du das Bild falsch interpretierst. Das oll ein vergleich der Architekturen sein. Ein mal bulldowzer, der 2 Threats bearbeitet in einem !Modul! und ein mal ein Kern mit HT, der 2 threats zerstückelt nacheinander bearbeitet.

Laut dem Bild werden die Threads im Decoder zerstückelt, aber nach dem L2 Cache kommen die Threads wieder Syncron raus!

Hat sonst noch jemand eine Erklärung?

MfG

Opteron

Redaktion

☆☆☆☆☆☆

Da wird nichts zerstückelt, die Decoder arbeiten halt wechselweise an Thread 1 oder 2, und/oder gleichzeitig an beiden Threads, je nachdem wie die Instruktionen fallen.Gut möglich, daher frage ich ja!

Laut dem Bild werden die Threads im Decoder zerstückelt, aber nach dem L2 Cache kommen die Threads wieder Syncron raus!

Hat sonst noch jemand eine Erklärung?

Ansonsten hat noch jeder Kern seine eigenen AGUs und Load/Store Abteilung, deswegen laufen die Speicherzugriffe auch mehr oder minder unabhängig voneinander, auch wenn der L2 gemeinsam benützt wird.

Mit "strong threads" meinen sie, dass sie 2x volle Power für die Threads bei CMT haben, während sich bei SMT die Kernleistung pro Thread quasi halbiert, da sich die 2 Threads viel mehr Resourcen teilen müssen. Zusammen genommen bringen 2 SMT Threads dann natürlich mehr Durchsatz, aber max. kommt man halt auf 130%, während es mit CMT 180% Leistung sind. 100% ist dabei die Leistung eines Kerns mit einem Thread.

ciao

Alex

WindHund

Grand Admiral Special

- Mitglied seit

- 30.01.2008

- Beiträge

- 12.236

- Renomée

- 538

- Standort

- Im wilden Süden (0711)

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- NumberFields@home

- Lieblingsprojekt

- none, try all

- Meine Systeme

- RYZEN R9 3900XT @ ASRock Taichi X570 & ASUS RX Vega64

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5950X

- Mainboard

- ASRock 570X Taichi P5.05 Certified

- Kühlung

- AlphaCool Eisblock XPX, 366x40mm Radiator 6l Brutto m³

- Speicher

- 2x 16 GiB DDR4-3600 CL26 Kingston (Dual Rank, unbuffered ECC)

- Grafikprozessor

- 1x ASRock Radeon RX 6950XT Formula OC 16GByte GDDR6 VRAM

- Display

- SAMSUNG Neo QLED QN92BA 43" up to 4K@144Hz FreeSync PP HDR10+

- SSD

- WD_Black SN850 PCI-Express 4.0 NVME

- HDD

- 3 Stück

- Optisches Laufwerk

- 1x HL-DT-ST BD-RE BH10LS30 SATA2

- Soundkarte

- HD Audio (onboard)

- Gehäuse

- SF-2000 Big Tower

- Netzteil

- Corsair RM1000X (80+ Gold)

- Tastatur

- Habe ich

- Maus

- Han I

- Betriebssystem

- Windows 10 x64 Professional (up to date!)

- Webbrowser

- @Chrome.Google & Edge Chrome

Mercy Opteron!

Dann wäre ein Turbo garnicht so abwägig, es wird nur ein Kern genutzt womit weniger TDP entsteht für mehr Takt.

Dann evt. sogar für 2 Threads.

MfG

Dann wäre ein Turbo garnicht so abwägig, es wird nur ein Kern genutzt womit weniger TDP entsteht für mehr Takt.

Dann evt. sogar für 2 Threads.

MfG

Opteron

Redaktion

☆☆☆☆☆☆

Hmm, hatten wir das schon ?

Vielleicht der DIE Codename, also quasi Orochi 2.0 ?

Zum Namen:

Na mal schauen, was das wird.

ciao

Alex

http://old.nabble.com/-PATCH--AMD-bdver2-processors-2-2---TBM-td30502191.html+@code{@value{AS}} supports AMD's Trailing Bit Manipulation (TBM)

+instruction set, available on AMD's BDVER2 processors (Trinity and

+Viperfish).

Vielleicht der DIE Codename, also quasi Orochi 2.0 ?

Zum Namen:

Klingt gut ^^Die Viperfische (Chauliodus) sind eine Gattung der Bartel-Drachenfische (Stomiidae) und gehören zur Unterfamilie Stomiinae. Manche Ichthyologen stellen sie in eine eigene Familie, Chauliodontidae, z.B. weil sie keine Bartel haben. Viperfische sind Beutegreifer der Tiefsee. Sie sind hochspezialisiert für eine Existenz in diesem uns so lebensfeindlich scheinenden Lebensraum. Mit etwa 30 Zentimetern Körpergröße (maximal 35 cm) gehören sie zu den größeren, aber auch recht häufigen Fischen der oberen Tiefsee.

Klingt weniger gutDie Viperfische wurden oft als bizarre, leuchtende Raubtiere der Tiefsee beschrieben

Na mal schauen, was das wird.

ciao

Alex

Ähnliche Themen

- Antworten

- 368

- Aufrufe

- 40K

- Antworten

- 28

- Aufrufe

- 20K

- Antworten

- 0

- Aufrufe

- 2K

G

- Antworten

- 0

- Aufrufe

- 2K

G

- Antworten

- 8

- Aufrufe

- 4K