App installieren

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: This feature may not be available in some browsers.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

AMD Halo - HighEnd-APUs (FP11, Strix Halo)

- Ersteller E555user

- Erstellt am

E555user

Grand Admiral Special

★ Themenstarter ★

- Mitglied seit

- 05.10.2015

- Beiträge

- 2.173

- Renomée

- 938

Halo APUs

In diversen Nutzerforen gab es in der Vergangenheit schon oft Überlegungen und Hoffnungen auf APUs für PCs mit besonders grosser GPU-Leistung. Während AMD bei Gaming-Konsolen mehrfach bewiesen hatte, dass man entpsrechend potente SoCs entwickeln kann waren APUs für Laptop und Desktop in der Grafikleistung sehr eingeschränkt. Mit den sich verdichtenden Infos und Gerüchten wird es Zeit für einen separaten Thread zu den kommenden HighEnd-APUs von AMD.Sofern man wie in der Vergangenheit über mehrere Generationen an einem einheitlichem Package für OEMs festhalten ergibt sich eine neue Produktkategorie, die Notebook-Designes über mehrere Jahre nutzen lassen, womöglich sogar Ähnlichkeiten mit Intels Designvorgaben aufweisen.

Das Besondere an Strix Halo ist heuer, dass die APU nicht als Monolith konzipiert ist sondern vielmehr ein flexibleres Chiplet-Design aufweist. Aufgrund der Grösse wird von einem BGA-Package ausgegangen, über eine Eignung für Sockel AM5 wird noch spekuliert.

Für die mögliche neue SoC Klasse als Package zeigen sich folgende Parameter:

- FP11: 37.5mm x 45.0mm; 1687mm² (wie Intel LGA-1700)

- LPDDR 256bit Speicherschnittstelle

- I/O 4x USB, 16 Lanes PCIe, 4x Display, tbc

- Powerbudget >175W

Strix Halo

Auf Videocardz.com wurden zuletzt am 08. Juli 2024 Informationen aus dem Chiphellforum zusammengetragen, zuvor auch am 11. Mai.

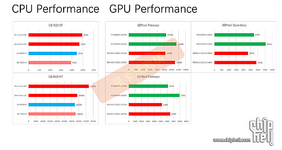

In der Gaming-Performance wird Strix Halo in etwa der Leistungsklasse einer RTX4060 bis RTX4070 zugeordnet. Für CPU erwartet man swohl in SingleThread als auch MultiThreading an Intels Core i9-14900K vorbeizuziehen, die NPU-Leistung ist dabei unberücksichtigt.

Aus der erwarteten ersten SKU Serie umfasst der Strix Halo SoC im Vollausbau:

Aus der erwarteten ersten SKU Serie umfasst der Strix Halo SoC im Vollausbau:(Korrekturen nach CES2025 Präsentation)

- 2 CCDs Zen5 mit

5.8GHz5.1GHz boost, ab 3.0GHz base Clock(jew.)- 8C/16T

- 8MB L2, 32MB L3

- TSMC N4x FinFET

- cIOD Client I/O Die mit GPU und NPU

- 20 WGP RDNA3.5 mit

3.02.9GHz (tot.)- 40 CU, 2,560 stream processors

- 80 AI accelerator

- 40 Ray accelerator

- NPU XDNA2 mit 50

-70TOPs - LPDDR5

x-85338000 bis 128GB @256GB/s (?GDDR6 128bit, 320GB/s)- Memory Attached Last Level iF Cache 32MB (500GB/s Bandbreite Äquivalent)

- Nur für GPU, kann durch AMD per Flag geändert werden

- Kohärent zum gesamtne Speicher

4 Lanes PCIe54x NVMe/GPP

816Lanes PCIe4- 4x NVMe/GPP

- 1x WLAN

- 1x LAN

210x etc

- 8x USB nativ

- 2 USB 4 (40Gbps)

23 USB 3.2 Gen2 (10Gbps)43 USB 2.0 (480Mbps)

- DisplayPorts

- eDP (DP2.1 HBR3)

- extern DP (DP2.1 UHBR10)

- USBC Alt-DP (DP2.1 UHBR10)

- USB4 Alt-DP (DP2.1 UHBR20)

- TSMC N4P

(oder N3E)

- 20 WGP RDNA3.5 mit

Von TechPowerUp kommt die Spekulation um ein zusätzliches GDDR6 Speicherinterface. Im Gegenzug könnte das LPDDR Interface wohl halb so breit ausfallen und man müsste mit unterschiedlichen Speicherdomänen zurechtkommen.

Bei TomsHardware glaubt man an 70 TOPs NPU, auch im April fasste man die frühen Leaks bereits zusammen.

Die Leaks via Twitter/X im April 2024 wie von HKEPC Hardware berichtet haben sich bei Strix Point gänzlich korrekt erwiesen. Das spricht wiederum für 16 Lanes PCIe4 ohne PCIe5.

Medusa Halo

Zuletzt hatte auch Youtuber MLID mit dem "Medusa Leak" eine weitere Halo-Generation in Aussicht gestellt, bereits der Strix Halo cIOD soll in TSMC N3E gefertigt sein. Demnach würde eine solche SoC eine gleiche cIOD mit moderneren Zen6 Chiplets aufbieten.Mit Leak-Video vom 28. März 2025 ergeben sich erste Eckdaten. Der Launch ist für 2H/2027 geplant.

In Erweiterung zum Vorgänger umfasst der Medusa Halo SoC im Vollausbau:

- 2x CCDs Zen6 mit ?GHz, jeweils

- 12C/24T

- 12MB L2, 48MB L3

- TSMC N2P

- cIOD Client I/O Die mit GPU und NPU (potentiell SI/iGPU auch halbiert für "little Halo")

- 2 Zen6 LP Cores

- 24 WGP RDNA unbekant (3.5+ bis 5)

- 48 CU, 3,072 stream processors

- 96 AI accelerator

- 48 Ray accelerator

- NPU XDNA? TOPs

- LPDDR6 384bit oder LPDDR5x 256bit (Grösse ?GB , Bandbreite ?GB/s)

- Nur für GPU, kann durch AMD per Flag geändert werden

- Kohärent zum gesamten Speicher

- 4x NVMe/GPP

- 1x WLAN

- 1x LAN

- 10x etc

- 8x USB nativ

- 2 USB 4 (40Gbps)

- 3 USB 3.2 Gen2 (10Gbps)

- 3 USB 2.0 (480Mbps)

- DisplayPorts

- eDP (DP2.1 HBR3)

- extern DP (DP2.1 UHBR10)

- USBC Alt-DP (DP2.1 UHBR10)

- USB4 Alt-DP (DP2.1 UHBR20)

- TSMC N3P

Zuletzt bearbeitet:

E555user

Grand Admiral Special

★ Themenstarter ★

- Mitglied seit

- 05.10.2015

- Beiträge

- 2.173

- Renomée

- 938

Via WCCFtech kommt ein vermuteter erster Benchmarkwert für ein 8C Engineering Sample.

HP - Geekbench

Benchmark results for a HP with an AMD Eng Sample: 100-000001422-31_N processor.

browser.geekbench.com

NEO83

Grand Admiral Special

- Mitglied seit

- 19.01.2016

- Beiträge

- 5.592

- Renomée

- 996

- Standort

- Wilhelmshaven

- Meine Systeme

- R9 7950X & RTX5080 | R5 9600X & RX9070XT | 7940HS & RTX4070

- BOINC-Statistiken

- Mein Desktopsystem

- Kraftzwerg | MiniMe

- Mein Laptop

- ASUS TUF A17 @R9 7940HS @RTX4070

- Details zu meinem Desktop

- Prozessor

- R9 7950X | R5 9600X

- Mainboard

- MSI MAG X870 Tomahawk WIFI | ASUS B850M-Plus WiFi

- Kühlung

- Corsair iCUE LINK H115i RGB | Noctua NH-D12L

- Speicher

- Corsair Vengeance 64GB, DDR5-6000 | TeamGroup 32GB, DDR5 7200

- Grafikprozessor

- PNY GeForce RTX 5080 OC | RX9070XT RedDevil

- Display

- MSI MAG 274UPFDE @UHD @144Hz | MSI MPG ARTYMIS 273CQRDE @WQHD

- SSD

- WD_BLACK SN850X 1TB, WD_BLACK SN850X 2TB | WD Blue 1TB, FIKWOT 2TB

- Optisches Laufwerk

- USB BD-Brenner

- Soundkarte

- Onboard

- Gehäuse

- Corsair Frame 4000D | Jonsbo D31 MESH

- Netzteil

- be quiet! Power Zone 2 1000W | ASUS ROG Loki 1000W Platinum SFX-L

- Tastatur

- Logitech G815

- Maus

- Logitech G502 SE Lightspeed

- Betriebssystem

- Windows 11 | Dualboot Windows 11 & CachyOS

- Webbrowser

- FireFox | FireFox

- Internetanbindung

-

▼600MBit

▲300MBit

Ich bin mal gespannt ob Anbieter wie MinisForum die APU auf einem mITX Board anbieten werden so wie sie es mit dem BD790i gemacht haben ...

Dann würde das einen wirklich geilen mITX PC geben der aber eben nicht so ein Heulquirl ist wie diese normalen MiniPCs ...

Am besten noch mit LP-CAMM2 Modulen damit der Speicher angepasst werden kann, ja die Module sind och nicht so weit verbreitet aber irgenwann muss man halt mal anfangen

Dann würde das einen wirklich geilen mITX PC geben der aber eben nicht so ein Heulquirl ist wie diese normalen MiniPCs ...

Am besten noch mit LP-CAMM2 Modulen damit der Speicher angepasst werden kann, ja die Module sind och nicht so weit verbreitet aber irgenwann muss man halt mal anfangen

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 15.751

- Renomée

- 2.499

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 7800X3D

- Mainboard

- MSI MPG X670E CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 32GB DDR5-6000 CL36

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Crucial T705 4TB

- HDD

- Western Digital WD Red 2TB, 3TB, 8TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

Die vorhandenen Plattformen halte ich dafür für wenig sinnvoll.

Dem normalem AM5 Sockel fehlen die zusätzlichen Speicherkanäle und für die Threadripper Plattform dürften der APU die PCIe Lanes fehlen.

Dem normalem AM5 Sockel fehlen die zusätzlichen Speicherkanäle und für die Threadripper Plattform dürften der APU die PCIe Lanes fehlen.

Dass hier ein neuer Sockel mit ziemlicher Sicherheit her muesste, sollte klar sein IMHO (256bit Memory Bus etc.).

Selbst wenn es mechanisch (fast) passen sollte (Kann die APU plain DDR5?).

Oder gibt es da schon andere Meldungen? Einen Super AM5 Sockel oder AI AM5 Sockel ?

?

Ich denke jedoch, dass wir leider nie eine gesockelte Variante vorerst sehen werden.

Aber wer weiss, was die mittelbare Zukunft bringt?

Ich bin auch gespannt wie viel davon in ein neues IO Die einfliessen wird; denn wir wissen ohne AI und mehr Speichertakt geht da nix also muss alsbald ein neues her fuer Zen6 und Co.

Gruss,

TNT

Selbst wenn es mechanisch (fast) passen sollte (Kann die APU plain DDR5?).

Oder gibt es da schon andere Meldungen? Einen Super AM5 Sockel oder AI AM5 Sockel

Ich denke jedoch, dass wir leider nie eine gesockelte Variante vorerst sehen werden.

Aber wer weiss, was die mittelbare Zukunft bringt?

Ich bin auch gespannt wie viel davon in ein neues IO Die einfliessen wird; denn wir wissen ohne AI und mehr Speichertakt geht da nix also muss alsbald ein neues her fuer Zen6 und Co.

Gruss,

TNT

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 15.751

- Renomée

- 2.499

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 7800X3D

- Mainboard

- MSI MPG X670E CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 32GB DDR5-6000 CL36

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Crucial T705 4TB

- HDD

- Western Digital WD Red 2TB, 3TB, 8TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

Ich bezweifel das es sich auch nur ansatzweise rechnen würde dafür einen Sondersockel auf den Weg zu bringen.

Das kommt darauf an, was AMD damit vorhat oder wo sie es sehen. Es muss ja nicht gleich die volle Halokost sein.Ich bezweifel das es sich auch nur ansatzweise rechnen würde dafür einen Sondersockel auf den Weg zu bringen.

Dennoch wuerde ich auch nicht gleich einen neuen Sockel erwarten aber vielleicht im long run kommt da was in einem Desktop verbaut werden kann.

Motherboards muessen offensichtlich nicht mehr nur $100 kosten usw.

Aber das wird eher Wunsch als Realitaet sein.

Aber vielleicht wird man das eine oder andere Board mit soldered APU finden in den naechsten 18-24+ Monaten.

Wird es dafuer einen Markt geben? Heute nicht, morgen auch nicht aber dann?

Dennoch erwarte ich, dass gewisse Dinge/Erfahrungen sich an anderer Stelle in neuen Produkten wiederfinden werden.

Auch ist diese Halo APU vermutlich nicht einfach vom Himmel gefallen bei AMD.

Gruss,

TNT

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 15.751

- Renomée

- 2.499

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 7800X3D

- Mainboard

- MSI MPG X670E CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 32GB DDR5-6000 CL36

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Crucial T705 4TB

- HDD

- Western Digital WD Red 2TB, 3TB, 8TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

Ein Sockel dürfte aus Sicht des Herstellers sinnvoll sein wenn viele unterschiedliche Modelle auf der gleichen Plattform laufen soll, beispielsweise um viele Systemvarianten auf dem gleichen Mainboard aufzubauen (OEMs) und das wäre bei den Halo APUs wohl kaum der Fall. Auch sieht es eher danach aus dass die APU nicht für normalen DDR5 Speicher konzipiert ist sondern für den deutlich schnelleren LPDDR5X Speicher. Es gäbe zwar auch DDR5 OC Module die in ähnliche Taktregionen vordringen können aber die wären erheblich teurer und es sind eben nur OC Module die seitens der Signalqualität erheblich problematischer sind als die fest verlöteten LPDDR5X Chips.

Das wären aus meiner Sicht auch schon die Hauptgründe warum ich eine gesockelte Variante als sehr unwarscheinlich halte.

Sie wären teurer, problematischerund/oder langsamer (je nach verbauten Speichermodulen) und der verbleibende Vorteil der Wechselbarkeit dürfte die Hauptabnehmer solcher Proessoren herzlich wenig interessieren, die OEMs.

Das wären aus meiner Sicht auch schon die Hauptgründe warum ich eine gesockelte Variante als sehr unwarscheinlich halte.

Sie wären teurer, problematischerund/oder langsamer (je nach verbauten Speichermodulen) und der verbleibende Vorteil der Wechselbarkeit dürfte die Hauptabnehmer solcher Proessoren herzlich wenig interessieren, die OEMs.

NEO83

Grand Admiral Special

- Mitglied seit

- 19.01.2016

- Beiträge

- 5.592

- Renomée

- 996

- Standort

- Wilhelmshaven

- Meine Systeme

- R9 7950X & RTX5080 | R5 9600X & RX9070XT | 7940HS & RTX4070

- BOINC-Statistiken

- Mein Desktopsystem

- Kraftzwerg | MiniMe

- Mein Laptop

- ASUS TUF A17 @R9 7940HS @RTX4070

- Details zu meinem Desktop

- Prozessor

- R9 7950X | R5 9600X

- Mainboard

- MSI MAG X870 Tomahawk WIFI | ASUS B850M-Plus WiFi

- Kühlung

- Corsair iCUE LINK H115i RGB | Noctua NH-D12L

- Speicher

- Corsair Vengeance 64GB, DDR5-6000 | TeamGroup 32GB, DDR5 7200

- Grafikprozessor

- PNY GeForce RTX 5080 OC | RX9070XT RedDevil

- Display

- MSI MAG 274UPFDE @UHD @144Hz | MSI MPG ARTYMIS 273CQRDE @WQHD

- SSD

- WD_BLACK SN850X 1TB, WD_BLACK SN850X 2TB | WD Blue 1TB, FIKWOT 2TB

- Optisches Laufwerk

- USB BD-Brenner

- Soundkarte

- Onboard

- Gehäuse

- Corsair Frame 4000D | Jonsbo D31 MESH

- Netzteil

- be quiet! Power Zone 2 1000W | ASUS ROG Loki 1000W Platinum SFX-L

- Tastatur

- Logitech G815

- Maus

- Logitech G502 SE Lightspeed

- Betriebssystem

- Windows 11 | Dualboot Windows 11 & CachyOS

- Webbrowser

- FireFox | FireFox

- Internetanbindung

-

▼600MBit

▲300MBit

Ich würde mich über Boards mit verlöteter APU freuen, das RAM Problem kannst du einfach mit LP-CAMM2 umgehen und ich denke dass das zumindest Mittelfristig ein gangbarer Weg sein wird.

Vermutlich werden Firmen wie MinisForum etc die ersten sein die solche Boards anbieten werden aber anfangs eben auch mit verlötetem RAM aber dennoch würde ICH mich vermutlich dazu hinreißen lassen so ein Board zu kaufen.

Denn wenn ich für mich realistisch bin, dann brauche ich garnicht mehr Leistung als das was AMD da anbieten wird, sollte die APU wirklich in Regionen wie der 4070/7800XT oder so vorstoßen können könnte das viele viele PCs wesentlich kleiner machen und Gaming auf kleinem Raum bleibt kein Wunschtraum mehr ... denn seien wir mal ehrlich, ein DeskMeet X600 ist durchaus nett aber auch schon wieder ziemlich "groß" ... aber ein DeskMini mit so einer APU, das wäre schon wirklich was nettes und das wenn möglich OHNE die Nachteile die solche MiniPCs mit 2 NB Lüftern mitsich bringt ...

Ich würde wie gesagt sofort drauf anspringen

Vermutlich werden Firmen wie MinisForum etc die ersten sein die solche Boards anbieten werden aber anfangs eben auch mit verlötetem RAM aber dennoch würde ICH mich vermutlich dazu hinreißen lassen so ein Board zu kaufen.

Denn wenn ich für mich realistisch bin, dann brauche ich garnicht mehr Leistung als das was AMD da anbieten wird, sollte die APU wirklich in Regionen wie der 4070/7800XT oder so vorstoßen können könnte das viele viele PCs wesentlich kleiner machen und Gaming auf kleinem Raum bleibt kein Wunschtraum mehr ... denn seien wir mal ehrlich, ein DeskMeet X600 ist durchaus nett aber auch schon wieder ziemlich "groß" ... aber ein DeskMini mit so einer APU, das wäre schon wirklich was nettes und das wenn möglich OHNE die Nachteile die solche MiniPCs mit 2 NB Lüftern mitsich bringt ...

Ich würde wie gesagt sofort drauf anspringen

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 15.751

- Renomée

- 2.499

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 7800X3D

- Mainboard

- MSI MPG X670E CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 32GB DDR5-6000 CL36

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Crucial T705 4TB

- HDD

- Western Digital WD Red 2TB, 3TB, 8TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

Die Frage wäre aber dennoch ob der Speicher damit auch die anvisierten Taktraten erreicht denn gehe ich nach dem Artikel wäre das nicht der Fall.

www-anandtech-com.translate.goog

www-anandtech-com.translate.goog

Es ist jedoch anzumerken, dass sich Systemanbieter zumindest bei der ersten Generation von LPCAMM2-Modulen zwischen Modularität und Leistung entscheiden müssen. Während fest verlöteter LPDDR5X-Speicher mit Geschwindigkeiten von bis zu 8533 MT/s erhältlich ist – und 9600 MT/s in Aussicht stehen – werden die schnellsten LPCAMM2-Module, die für dieses Jahr von Micron und dem Konkurrenten Samsung geplant sind, mit 7500 MT/s laufen.

Micron Ships Crucial-Branded LPCAMM2 Memory Modules: 64GB of LPDDR5X For $330

NEO83

Grand Admiral Special

- Mitglied seit

- 19.01.2016

- Beiträge

- 5.592

- Renomée

- 996

- Standort

- Wilhelmshaven

- Meine Systeme

- R9 7950X & RTX5080 | R5 9600X & RX9070XT | 7940HS & RTX4070

- BOINC-Statistiken

- Mein Desktopsystem

- Kraftzwerg | MiniMe

- Mein Laptop

- ASUS TUF A17 @R9 7940HS @RTX4070

- Details zu meinem Desktop

- Prozessor

- R9 7950X | R5 9600X

- Mainboard

- MSI MAG X870 Tomahawk WIFI | ASUS B850M-Plus WiFi

- Kühlung

- Corsair iCUE LINK H115i RGB | Noctua NH-D12L

- Speicher

- Corsair Vengeance 64GB, DDR5-6000 | TeamGroup 32GB, DDR5 7200

- Grafikprozessor

- PNY GeForce RTX 5080 OC | RX9070XT RedDevil

- Display

- MSI MAG 274UPFDE @UHD @144Hz | MSI MPG ARTYMIS 273CQRDE @WQHD

- SSD

- WD_BLACK SN850X 1TB, WD_BLACK SN850X 2TB | WD Blue 1TB, FIKWOT 2TB

- Optisches Laufwerk

- USB BD-Brenner

- Soundkarte

- Onboard

- Gehäuse

- Corsair Frame 4000D | Jonsbo D31 MESH

- Netzteil

- be quiet! Power Zone 2 1000W | ASUS ROG Loki 1000W Platinum SFX-L

- Tastatur

- Logitech G815

- Maus

- Logitech G502 SE Lightspeed

- Betriebssystem

- Windows 11 | Dualboot Windows 11 & CachyOS

- Webbrowser

- FireFox | FireFox

- Internetanbindung

-

▼600MBit

▲300MBit

Na das bezieht sich auf dieses Jahr ... vor Mitte bis Ende nächsten Jahres sehe ich garnicht das ein mITX Board mit Strix Halo verfügbar sein wird und wie ich auch sagte kann ich mir auch vorstellen das die ersten Boards tatsächlich mit verlötetem RAM erscheinen

Dennoch sind die 7500MT/s ja schonmal einiges mehr als das was standartmäßig mit DDR5 möglich ist und am Ende wird die Verfügbarkeit solche Boards und Laptops mit LP-CAMM2 darüber entscheiden wie schnell sich die Module in größe und Geschwindigkeit weiterentwickeln.

Dennoch sind die 7500MT/s ja schonmal einiges mehr als das was standartmäßig mit DDR5 möglich ist und am Ende wird die Verfügbarkeit solche Boards und Laptops mit LP-CAMM2 darüber entscheiden wie schnell sich die Module in größe und Geschwindigkeit weiterentwickeln.

vinacis_vivids

Admiral Special

- Mitglied seit

- 12.01.2004

- Beiträge

- 1.435

- Renomée

- 257

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 7950X 16C/32T

- Mainboard

- ASUS ProArt X670E-CREATOR WIFI

- Kühlung

- Arctic Liquid Freezer II 360 RGB

- Speicher

- HyperX Fury 64GB DDR5 6000Mhz CL30

- Grafikprozessor

- Sapphire Nitro+ RX 7900 XTX 24GB

- Display

- LG 5K HDR 10bit 5120x2160@60hz

- SSD

- Samsung SSD 980Pro 2TB

- Soundkarte

- Creative Soundblaster ZXR

- Gehäuse

- Cougar DarkBlader X5

- Netzteil

- InterTech Sama Forza 1200W

- Tastatur

- Cherry MX-10.0 RGB Mechanisch

- Maus

- Razer Mamba

- Betriebssystem

- Windows 11 Education Pro

- Webbrowser

- Google Chrome

- Internetanbindung

- ▼1000 Mbit

So eine high-end APU ist auch für den mobilen Markt interessant. Laptops und mobile Gaming-Handhelds sind Kandidaten für eine feste Verlötung (und niedrigen Verbrauch) und daher geeignet für 8533 MT/s oder auch 9600 MT/s. Glaube kaum, dass die APU für stationäres AM5 interessant ist, wo die große CPU alleine 170W (7950X / 9950X) und die große GPU (7900XTX) 464W sich gönnen.

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 15.751

- Renomée

- 2.499

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 7800X3D

- Mainboard

- MSI MPG X670E CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 32GB DDR5-6000 CL36

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Crucial T705 4TB

- HDD

- Western Digital WD Red 2TB, 3TB, 8TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

@NEO83

Ist aber auch noch ein ganzes Stück vom vorgesehenen LPDDR5X-8533 entfernt.

Eines hat die bisherige Erfahrung mit den APUs aber auch gezeigt, vor allem bei den Top Modellen.

Die vorgesehene Speichergeschwindigkeit ist eher etwas zu langsam weshalb ein langsamerer Speicher mit Sicherheit ziemlich kontraproduktiv wäre und solange es solche Module nicht auch als Endkundenprodukt zu kaufen gibt ist die Aufrüstbarkeit auch eher theoretischer Natur.

Ist aber auch noch ein ganzes Stück vom vorgesehenen LPDDR5X-8533 entfernt.

Eines hat die bisherige Erfahrung mit den APUs aber auch gezeigt, vor allem bei den Top Modellen.

Die vorgesehene Speichergeschwindigkeit ist eher etwas zu langsam weshalb ein langsamerer Speicher mit Sicherheit ziemlich kontraproduktiv wäre und solange es solche Module nicht auch als Endkundenprodukt zu kaufen gibt ist die Aufrüstbarkeit auch eher theoretischer Natur.

NEO83

Grand Admiral Special

- Mitglied seit

- 19.01.2016

- Beiträge

- 5.592

- Renomée

- 996

- Standort

- Wilhelmshaven

- Meine Systeme

- R9 7950X & RTX5080 | R5 9600X & RX9070XT | 7940HS & RTX4070

- BOINC-Statistiken

- Mein Desktopsystem

- Kraftzwerg | MiniMe

- Mein Laptop

- ASUS TUF A17 @R9 7940HS @RTX4070

- Details zu meinem Desktop

- Prozessor

- R9 7950X | R5 9600X

- Mainboard

- MSI MAG X870 Tomahawk WIFI | ASUS B850M-Plus WiFi

- Kühlung

- Corsair iCUE LINK H115i RGB | Noctua NH-D12L

- Speicher

- Corsair Vengeance 64GB, DDR5-6000 | TeamGroup 32GB, DDR5 7200

- Grafikprozessor

- PNY GeForce RTX 5080 OC | RX9070XT RedDevil

- Display

- MSI MAG 274UPFDE @UHD @144Hz | MSI MPG ARTYMIS 273CQRDE @WQHD

- SSD

- WD_BLACK SN850X 1TB, WD_BLACK SN850X 2TB | WD Blue 1TB, FIKWOT 2TB

- Optisches Laufwerk

- USB BD-Brenner

- Soundkarte

- Onboard

- Gehäuse

- Corsair Frame 4000D | Jonsbo D31 MESH

- Netzteil

- be quiet! Power Zone 2 1000W | ASUS ROG Loki 1000W Platinum SFX-L

- Tastatur

- Logitech G815

- Maus

- Logitech G502 SE Lightspeed

- Betriebssystem

- Windows 11 | Dualboot Windows 11 & CachyOS

- Webbrowser

- FireFox | FireFox

- Internetanbindung

-

▼600MBit

▲300MBit

Bis Ende kommenden jahres werden wir bestimmt schon in den Regionen um 8533MT/s wenn nicht auch schon bei 9600MT/s sein denke ich ... wenn man sich anschaut wie schnell DDR5 geworden ist

Warum sollte AMD die APU nicht weiter differenzieren/auspraegen koennen und mehrere Varianten davon in Markt bringen?viele unterschiedliche Modelle auf der gleichen Plattform laufen soll, beispielsweise um viele Systemvarianten auf dem gleichen Mainboard aufzubauen (OEMs) und das wäre bei den Halo APUs wohl kaum der Fall.

Schnell koennen einige Modelle aus dem einen Die abgeleitet (etwas weniger Halo...

Nichts anders passiert heute schon mit den CCD von Zen im Desktop etc.

Ich denke auch nicht, dass AMD es bei einer oder zwei Varianten auf Dauer dieser APU belassen wird.

Es bleibt die Frage, ob das Sinn macht in den Augen von AMD und was sie damit strategisch vorhaben (und was technisch/wirtschaftlich sinnvoll scheint).

Eine grosse Unbekannte ist im Moment noch der Preis & die Kosten einer dieser APUs und des notwendigen Unterbaus.

Wie wichtig wird AI noch fuer den Desktop etc. oder eben auch nicht, kann auch eine Rolle spielen IMHO.

AI-NPU technisch sieht es auf dem Desktop bei AMD aktuell eher sparsam aus.

Soll das ein grosse Reihe werden, mit dezidierten Nachfolgern parallel zu dem Standardprogramm oder bleibt auf die Ecke der HighEnd Notebooks/monbile Workstations beschraenkt?

Was wird die Idee AMDs sein?

Gruss,

TNT

[automerge]1728482054[/automerge]

Genau - vielleicht vermag AMD damit auf dem Desktop eine neue Klasse begruenden?Denn wenn ich für mich realistisch bin, dann brauche ich garnicht mehr Leistung als das was AMD da anbieten wird, sollte die APU wirklich in Regionen wie der 4070/7800XT oder so vorstoßen können könnte das viele viele PCs wesentlich kleiner machen und Gaming auf kleinem Raum bleibt kein Wunschtraum mehr ...

APUs die ein wenig serious Gaming & AI ermoeglichen und alle anderen APUs erst mal im kalten Regen stehen lassen.

Aber das sind alles noch Spukschloesser IMHO solange man von AMD da nichts weiter hoert.

Gruss,

TNT

NEO83

Grand Admiral Special

- Mitglied seit

- 19.01.2016

- Beiträge

- 5.592

- Renomée

- 996

- Standort

- Wilhelmshaven

- Meine Systeme

- R9 7950X & RTX5080 | R5 9600X & RX9070XT | 7940HS & RTX4070

- BOINC-Statistiken

- Mein Desktopsystem

- Kraftzwerg | MiniMe

- Mein Laptop

- ASUS TUF A17 @R9 7940HS @RTX4070

- Details zu meinem Desktop

- Prozessor

- R9 7950X | R5 9600X

- Mainboard

- MSI MAG X870 Tomahawk WIFI | ASUS B850M-Plus WiFi

- Kühlung

- Corsair iCUE LINK H115i RGB | Noctua NH-D12L

- Speicher

- Corsair Vengeance 64GB, DDR5-6000 | TeamGroup 32GB, DDR5 7200

- Grafikprozessor

- PNY GeForce RTX 5080 OC | RX9070XT RedDevil

- Display

- MSI MAG 274UPFDE @UHD @144Hz | MSI MPG ARTYMIS 273CQRDE @WQHD

- SSD

- WD_BLACK SN850X 1TB, WD_BLACK SN850X 2TB | WD Blue 1TB, FIKWOT 2TB

- Optisches Laufwerk

- USB BD-Brenner

- Soundkarte

- Onboard

- Gehäuse

- Corsair Frame 4000D | Jonsbo D31 MESH

- Netzteil

- be quiet! Power Zone 2 1000W | ASUS ROG Loki 1000W Platinum SFX-L

- Tastatur

- Logitech G815

- Maus

- Logitech G502 SE Lightspeed

- Betriebssystem

- Windows 11 | Dualboot Windows 11 & CachyOS

- Webbrowser

- FireFox | FireFox

- Internetanbindung

-

▼600MBit

▲300MBit

Ja so ist es wohl, anfang kommenden Jahres wissen wir vermutlich schon mehr

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 15.751

- Renomée

- 2.499

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 7800X3D

- Mainboard

- MSI MPG X670E CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 32GB DDR5-6000 CL36

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Crucial T705 4TB

- HDD

- Western Digital WD Red 2TB, 3TB, 8TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

Ich sehe keinen Sinn darin für eine solchen Marktbereich eine Plattform mit wechselbaren RAM und ev. einen Sockel für die APU zu schaffen und diesen dann wegen der begrenzten Speichergeschwindigkeit nur mit kastrierten Modellen abzuspeisen.Warum sollte AMD die APU nicht weiter differenzieren/auspraegen koennen und mehrere Varianten davon in Markt bringen?

Klar dürfte es den einen oder anderen geben der sowas kaufen würde aber ich habe starke Zweifel das AMD die dabei anfallenden Investitionskosten für Entwicklung, Validierung usw. wieder raus bekommen würde.

Doch genauso koennte man es machenIch sehe keinen Sinn darin für eine solchen Marktbereich eine Plattform mit wechselbaren RAM und ev. einen Sockel für die APU zu schaffen und diesen dann wegen der begrenzten Speichergeschwindigkeit nur mit kastrierten Modellen abzuspeisen.

Salvage chips.

Aber AMD waeren nicht die ersten, die etwas mit soldered RAM zusammen mit Brett und CPU/APU an den Mann bringen moechten.

Die juengste Vergangenheit zeigt da ganz prominente Beispiele.

Aber das sind hier nur alles recht wilde Ideen hier im Forum. Bislang gibt es dazu kaum Anzeichen, wenn es auch nicht unmoeglich erscheint.

Wichtig ist, wie AMD selbst darueber denkt.

Wie wichtig ist der Memory Speed (-> Mall Cache) oder zerbricht die Performance, wenn da nur 6000er Klasse Speicher anbringen kann usw.

Wie sieht AMD da Marktchancen oder eben auch nicht? Bleibt es ein OnOff?

Gruss,

TNT

Zuletzt bearbeitet:

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 15.751

- Renomée

- 2.499

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 7800X3D

- Mainboard

- MSI MPG X670E CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 32GB DDR5-6000 CL36

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Crucial T705 4TB

- HDD

- Western Digital WD Red 2TB, 3TB, 8TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

Nicht alles was möglich ist ist eben auch wirtschaftlich sinnvoll, so geht die Sockelung wegen des komplizierteren Aufbaus eben auch ins Geld. Dann steht man schnell vor der Situation dass das langsamere, gesockelte Produkt ganz einfach teurer ist als die direkt verlötete Variante. Zudem scheinen die LP-CAMM2 Module noch nicht einmal auf dem freien Markt verfügbar zu sein wodurch die Vorteile mangels Austauschmodule gegen 0 gehen.

Hinzu kommt noch das Grundproblem dass der Löwenanteil der verkauften Systeme normalerweise eher selten aufgerüstet sondern bis zum Austausch genutzt wird wodurch das ein ein finanzielles Debakel mit Ansage werden würde und spätestens da ist das Thema bei den Herstellern normalerweise erledigt.

Hinzu kommt noch das Grundproblem dass der Löwenanteil der verkauften Systeme normalerweise eher selten aufgerüstet sondern bis zum Austausch genutzt wird wodurch das ein ein finanzielles Debakel mit Ansage werden würde und spätestens da ist das Thema bei den Herstellern normalerweise erledigt.

NEO83

Grand Admiral Special

- Mitglied seit

- 19.01.2016

- Beiträge

- 5.592

- Renomée

- 996

- Standort

- Wilhelmshaven

- Meine Systeme

- R9 7950X & RTX5080 | R5 9600X & RX9070XT | 7940HS & RTX4070

- BOINC-Statistiken

- Mein Desktopsystem

- Kraftzwerg | MiniMe

- Mein Laptop

- ASUS TUF A17 @R9 7940HS @RTX4070

- Details zu meinem Desktop

- Prozessor

- R9 7950X | R5 9600X

- Mainboard

- MSI MAG X870 Tomahawk WIFI | ASUS B850M-Plus WiFi

- Kühlung

- Corsair iCUE LINK H115i RGB | Noctua NH-D12L

- Speicher

- Corsair Vengeance 64GB, DDR5-6000 | TeamGroup 32GB, DDR5 7200

- Grafikprozessor

- PNY GeForce RTX 5080 OC | RX9070XT RedDevil

- Display

- MSI MAG 274UPFDE @UHD @144Hz | MSI MPG ARTYMIS 273CQRDE @WQHD

- SSD

- WD_BLACK SN850X 1TB, WD_BLACK SN850X 2TB | WD Blue 1TB, FIKWOT 2TB

- Optisches Laufwerk

- USB BD-Brenner

- Soundkarte

- Onboard

- Gehäuse

- Corsair Frame 4000D | Jonsbo D31 MESH

- Netzteil

- be quiet! Power Zone 2 1000W | ASUS ROG Loki 1000W Platinum SFX-L

- Tastatur

- Logitech G815

- Maus

- Logitech G502 SE Lightspeed

- Betriebssystem

- Windows 11 | Dualboot Windows 11 & CachyOS

- Webbrowser

- FireFox | FireFox

- Internetanbindung

-

▼600MBit

▲300MBit

Crucial 32GB LPCAMM2 LPDDR5X- 7500 memory | CT32G75C2LP5XG | Crucial DE

Kaufen Sie Crucial 32GB LPCAMM2 LPDDR5X- 7500 memory CT32G75C2LP5XG. online. Kostenlose Lieferung & 100% Kompatibilitätsgarantie bei Bestellungen mit Nutzung unserer Onlinetools..

Kann ich direkt bei Crucial kaufen ... an sich also erstmal "kein" Problem wenn man nur einen einzigen Anbieter als Problemlos ansieht.

Die Module werden sich allerdings vermutlich über Notebooks irgendwann durchsetzen ...

Vermutlich erstmal in den teuren Modellen wie hier aber vieles hat in teuren Geräten begonnnen

Ich für meinen Fall fände es gut und zwar unabhängig davon ob es Boards dafür gibt später aber der Standart gefällt mir einfach und er bringt Mobil eben vorteile, ob er auch für den normalen Desktop was bringt ... ich glaube nicht aber wer weiß

LPCAMM2 statt SO-DIMM: So teuer sind die RAM-Upgrades künftiger Laptops

Arbeitsspeicher, der nach dem Kauf eines Laptops aufgerüstet werden kann, soll künftig wieder zum Standard werden, nachdem RAM über die vergangenen Jahre zunehmend am Mainboard verlötet wurde. Crucial bietet nun die ersten Upgrade-Module für LPCAMM2-Notebooks an.

www.notebookcheck.com

www.notebookcheck.com

Gibt es schon, steckt aber noch in den Kinderschuhen.

Mal sehen wie die Verbreitung in einem Jahr ist.

Gruss und Danke,

TNT

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 15.751

- Renomée

- 2.499

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 7800X3D

- Mainboard

- MSI MPG X670E CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 32GB DDR5-6000 CL36

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Crucial T705 4TB

- HDD

- Western Digital WD Red 2TB, 3TB, 8TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

Dann schaut mal in den Preisvergleich denn da gibtes nichts und selbst bei Google habe ich nur Crucial als Anbieter gefunden. Mit dem freien Markt hat das doch eher wenig zu tuen.

Im übrigen würde man davon 2 Module benötigen und hätte dann einen Mindestausbau von 64 GB (habe bisher nur 32 und 64 GB pro Modul gefunden) für den mal eben gute 400 € fällig wären.

Die Wenigsten dürften bei fest verlöteten 64 GB RAM einen allso großen Aufrüstbedarf haben.

Das wäre dann preisbedingt eher etwas für die Top Modelle die aber wegen der Bandbreitenlimitierung unterversorgt wären. Wie gesagt, ich halte es für nahezu ausgeschlossen das solche Varianten kommen werden weil Kosten und Aufwand ziemlich hoch, der Nutzen ziemlich gering wäre, die Nachfrage entsprechend gering und das Minusgeschäft absehbar wäre. Vielleicht als Sondermodelle für einen Großabnehmer aber sonst?

Im übrigen würde man davon 2 Module benötigen und hätte dann einen Mindestausbau von 64 GB (habe bisher nur 32 und 64 GB pro Modul gefunden) für den mal eben gute 400 € fällig wären.

Die Wenigsten dürften bei fest verlöteten 64 GB RAM einen allso großen Aufrüstbedarf haben.

Das wäre dann preisbedingt eher etwas für die Top Modelle die aber wegen der Bandbreitenlimitierung unterversorgt wären. Wie gesagt, ich halte es für nahezu ausgeschlossen das solche Varianten kommen werden weil Kosten und Aufwand ziemlich hoch, der Nutzen ziemlich gering wäre, die Nachfrage entsprechend gering und das Minusgeschäft absehbar wäre. Vielleicht als Sondermodelle für einen Großabnehmer aber sonst?

Zuletzt bearbeitet:

Ähnliche Themen

- Antworten

- 0

- Aufrufe

- 17

- Antworten

- 0

- Aufrufe

- 34

- Antworten

- 18

- Aufrufe

- 1K

- Antworten

- 660

- Aufrufe

- 59K

- Antworten

- 22

- Aufrufe

- 9K