App installieren

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: This feature may not be available in some browsers.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

AMD - Zen 5 /5c - 4 nm/3 nm - Turin, Granite Ridge, Strix Point

- Ersteller pipin

- Erstellt am

derDruide

Grand Admiral Special

- Mitglied seit

- 09.08.2004

- Beiträge

- 2.773

- Renomée

- 450

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 3900X

- Mainboard

- Asus Strix B450-F Gaming

- Kühlung

- Noctua NH-C14

- Speicher

- 32 GB DDR4-3200 CL14 FlareX

- Grafikprozessor

- Radeon RX 590

- Display

- 31.5" Eizo FlexScan EV3285

- SSD

- Corsair MP510 2 TB, Samsung 970 Evo 512 GB

- HDD

- Seagate Ironwulf 6 TB

- Optisches Laufwerk

- Plextor PX-880SA

- Soundkarte

- Creative SoundblasterX AE-7

- Gehäuse

- Antec P280

- Netzteil

- be quiet! Straight Power E9 400W

- Maus

- Logitech Trackman Marble (Trackball)

- Betriebssystem

- openSUSE 15.2

- Webbrowser

- Firefox

- Internetanbindung

- ▼50 MBit ▲10 MBit

AMD will neben TSMCs 3 nm-Prozess wohl auch Samsungs 4 nm benutzen.

wccftech.com

wccftech.com

AMD To Utilize Samsung 4nm & TSMC 3nm Nodes For Next-Gen Chips, Zen 5C Possibly Codenamed Prometheus

AMD is expected to utilize Samsung's 4nm and TSMC's 3nm process node for its next-generation chips as hinted in a new leak.

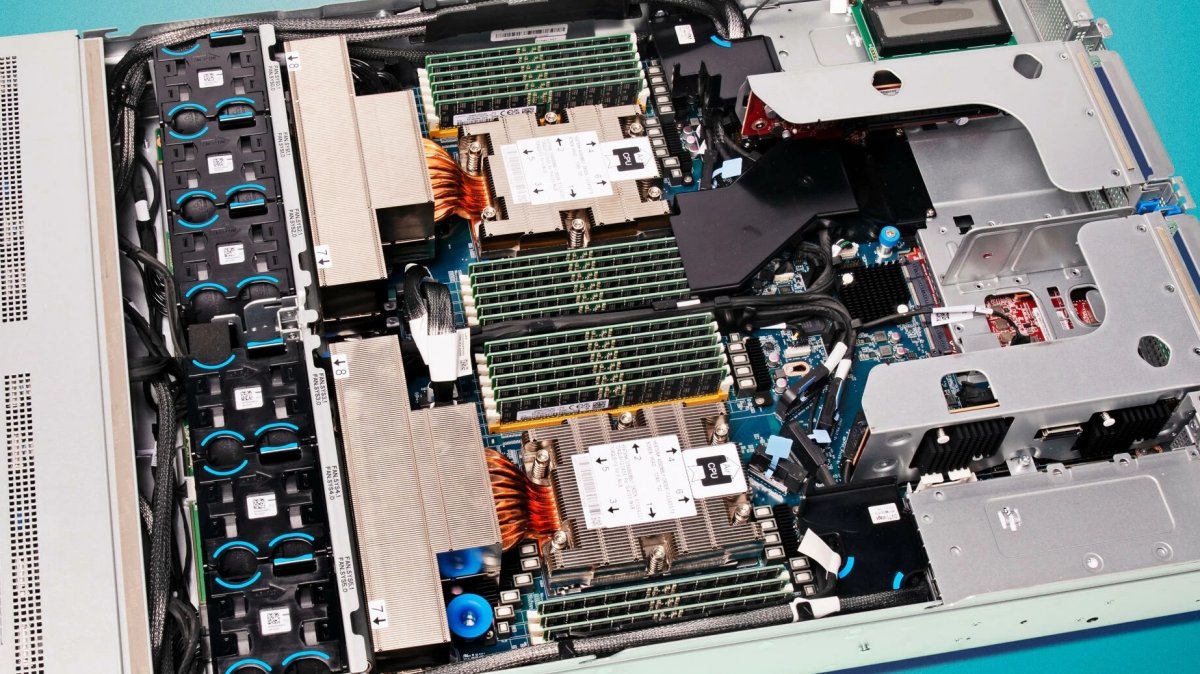

AMDs erster Zen-5-Prozessor "Turin" zeigt sich

Es gibt ein Lebenszeichen von AMDs nächster CPU-Generation. Erste Bilder zeigen den nächsten Epyc "Turin".

derDruide

Grand Admiral Special

- Mitglied seit

- 09.08.2004

- Beiträge

- 2.773

- Renomée

- 450

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 3900X

- Mainboard

- Asus Strix B450-F Gaming

- Kühlung

- Noctua NH-C14

- Speicher

- 32 GB DDR4-3200 CL14 FlareX

- Grafikprozessor

- Radeon RX 590

- Display

- 31.5" Eizo FlexScan EV3285

- SSD

- Corsair MP510 2 TB, Samsung 970 Evo 512 GB

- HDD

- Seagate Ironwulf 6 TB

- Optisches Laufwerk

- Plextor PX-880SA

- Soundkarte

- Creative SoundblasterX AE-7

- Gehäuse

- Antec P280

- Netzteil

- be quiet! Straight Power E9 400W

- Maus

- Logitech Trackman Marble (Trackball)

- Betriebssystem

- openSUSE 15.2

- Webbrowser

- Firefox

- Internetanbindung

- ▼50 MBit ▲10 MBit

Offiziell (per Quellcode) bestätigt: Family 26 (Family 1A) ist ZEN 5.

Zuletzt bearbeitet:

26 = 1Ah... Family 26 (hexadezimal: 1h) ...

derDruide

Grand Admiral Special

- Mitglied seit

- 09.08.2004

- Beiträge

- 2.773

- Renomée

- 450

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 3900X

- Mainboard

- Asus Strix B450-F Gaming

- Kühlung

- Noctua NH-C14

- Speicher

- 32 GB DDR4-3200 CL14 FlareX

- Grafikprozessor

- Radeon RX 590

- Display

- 31.5" Eizo FlexScan EV3285

- SSD

- Corsair MP510 2 TB, Samsung 970 Evo 512 GB

- HDD

- Seagate Ironwulf 6 TB

- Optisches Laufwerk

- Plextor PX-880SA

- Soundkarte

- Creative SoundblasterX AE-7

- Gehäuse

- Antec P280

- Netzteil

- be quiet! Straight Power E9 400W

- Maus

- Logitech Trackman Marble (Trackball)

- Betriebssystem

- openSUSE 15.2

- Webbrowser

- Firefox

- Internetanbindung

- ▼50 MBit ▲10 MBit

Oh, ist korrigiert.

eratte

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 11.11.2001

- Beiträge

- 22.497

- Renomée

- 3.059

- Standort

- Rheinberg / NRW

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- YoYo, Collatz

- Lieblingsprojekt

- YoYo

- Meine Systeme

- Wegen der aktuellen Lage alles aus.

- BOINC-Statistiken

- Mein Laptop

- Lenovo ThinkPad E15 Gen4 Intel / HP PAVILION 14-dk0002ng

- Details zu meinem Desktop

- Prozessor

- Ryzen R9 7950X

- Mainboard

- ASUS ROG Crosshair X670E Hero

- Kühlung

- Noctua NH-D15

- Speicher

- 2 x 32 GB G.Skill Trident Z DDR5 6000 CL30-40-40-96

- Grafikprozessor

- Sapphire Radeon RX7900XTX Gaming OC Nitro+

- Display

- 2 x ASUS XG27AQ (2560x1440@144 Hz)

- SSD

- Samsung 980 Pro 1 TB & Lexar NM790 4 TB

- Optisches Laufwerk

- USB Blu-Ray Brenner

- Soundkarte

- Onboard

- Gehäuse

- NEXT H7 Flow Schwarz

- Netzteil

- Corsair HX1000 (80+ Platinum)

- Tastatur

- ASUS ROG Strix Scope RX TKL Wireless / 2. Rechner&Server Cherry G80-3000N RGB TKL

- Maus

- ROG Gladius III Wireless / 2. Rechner&Server Sharkoon Light2 180

- Betriebssystem

- Windows 11 Pro 64

- Webbrowser

- Firefox

- Verschiedenes

- 4 x BQ Light Wings 14. 1 x NF-A14 Noctua Lüfter. Corsair HS80 Headset .

- Internetanbindung

- ▼VDSL 100 ▲VDSL 100

eratte

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 11.11.2001

- Beiträge

- 22.497

- Renomée

- 3.059

- Standort

- Rheinberg / NRW

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- YoYo, Collatz

- Lieblingsprojekt

- YoYo

- Meine Systeme

- Wegen der aktuellen Lage alles aus.

- BOINC-Statistiken

- Mein Laptop

- Lenovo ThinkPad E15 Gen4 Intel / HP PAVILION 14-dk0002ng

- Details zu meinem Desktop

- Prozessor

- Ryzen R9 7950X

- Mainboard

- ASUS ROG Crosshair X670E Hero

- Kühlung

- Noctua NH-D15

- Speicher

- 2 x 32 GB G.Skill Trident Z DDR5 6000 CL30-40-40-96

- Grafikprozessor

- Sapphire Radeon RX7900XTX Gaming OC Nitro+

- Display

- 2 x ASUS XG27AQ (2560x1440@144 Hz)

- SSD

- Samsung 980 Pro 1 TB & Lexar NM790 4 TB

- Optisches Laufwerk

- USB Blu-Ray Brenner

- Soundkarte

- Onboard

- Gehäuse

- NEXT H7 Flow Schwarz

- Netzteil

- Corsair HX1000 (80+ Platinum)

- Tastatur

- ASUS ROG Strix Scope RX TKL Wireless / 2. Rechner&Server Cherry G80-3000N RGB TKL

- Maus

- ROG Gladius III Wireless / 2. Rechner&Server Sharkoon Light2 180

- Betriebssystem

- Windows 11 Pro 64

- Webbrowser

- Firefox

- Verschiedenes

- 4 x BQ Light Wings 14. 1 x NF-A14 Noctua Lüfter. Corsair HS80 Headset .

- Internetanbindung

- ▼VDSL 100 ▲VDSL 100

AMD to Fix Ryzen 8000G Desktop APU STAPM "Feature" via Motherboard BIOS Updates (TechPowerUp)

Sehe ich das richtig das die Abstände bei den ZEN Generationen immer größer werden?

Doppelposting wurde automatisch zusammengeführt:

Sehe ich das richtig das die Abstände bei den ZEN Generationen immer größer werden?

Zuletzt bearbeitet:

AMD bringt 2024 Ryzen-CPUs mit Zen-5-Architektur

Neue Ryzen- und Epyc-Prozessoren mit Zen-5-Architektur erscheinen 2024. Das hat die AMD-Chefin Lisa Su bestätigt.

derDruide

Grand Admiral Special

- Mitglied seit

- 09.08.2004

- Beiträge

- 2.773

- Renomée

- 450

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 3900X

- Mainboard

- Asus Strix B450-F Gaming

- Kühlung

- Noctua NH-C14

- Speicher

- 32 GB DDR4-3200 CL14 FlareX

- Grafikprozessor

- Radeon RX 590

- Display

- 31.5" Eizo FlexScan EV3285

- SSD

- Corsair MP510 2 TB, Samsung 970 Evo 512 GB

- HDD

- Seagate Ironwulf 6 TB

- Optisches Laufwerk

- Plextor PX-880SA

- Soundkarte

- Creative SoundblasterX AE-7

- Gehäuse

- Antec P280

- Netzteil

- be quiet! Straight Power E9 400W

- Maus

- Logitech Trackman Marble (Trackball)

- Betriebssystem

- openSUSE 15.2

- Webbrowser

- Firefox

- Internetanbindung

- ▼50 MBit ▲10 MBit

Ryzen 9000 vs. Core Ultra 200: Intel soll das CPU-Duell des Jahres bereits verloren haben. Quelle ist MLID.

www.pcgameshardware.de

www.pcgameshardware.de

Ryzen 9000 vs. Core Ultra 200: Intel soll das CPU-Duell des Jahres bereits verloren haben [Gerücht]

Wie Gerüchte besagen, soll Intel das CPU-Duell des Jahres zwischen Ryzen 9000 und Core Ultra 200 aufgrund von Verspätungen bereits gegen AMD verloren haben.

derDruide

Grand Admiral Special

- Mitglied seit

- 09.08.2004

- Beiträge

- 2.773

- Renomée

- 450

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 3900X

- Mainboard

- Asus Strix B450-F Gaming

- Kühlung

- Noctua NH-C14

- Speicher

- 32 GB DDR4-3200 CL14 FlareX

- Grafikprozessor

- Radeon RX 590

- Display

- 31.5" Eizo FlexScan EV3285

- SSD

- Corsair MP510 2 TB, Samsung 970 Evo 512 GB

- HDD

- Seagate Ironwulf 6 TB

- Optisches Laufwerk

- Plextor PX-880SA

- Soundkarte

- Creative SoundblasterX AE-7

- Gehäuse

- Antec P280

- Netzteil

- be quiet! Straight Power E9 400W

- Maus

- Logitech Trackman Marble (Trackball)

- Betriebssystem

- openSUSE 15.2

- Webbrowser

- Firefox

- Internetanbindung

- ▼50 MBit ▲10 MBit

Heise bringt eine "Wasserstandsmeldung" zu den ZEN 5-CPUs. Sie sollen zur Ryzen 9000-Serie gehören, entsprechende BIOS-Versionen stehen als BETA-Versionen zum Download bereit. Das AGESA steht aktuell bei Version 1.1.7.0 Patch A und firmiert jetzt als FireRangePi (vorher ComboAM5PI).

Am 3. Juni um 09:30 hält Lisa Su die Eröffnungs-Keynote auf der Computex. Wobei 09:30 h auch irgendwie relativ ist. Für die Taiwanesen ist das ein guter Zeitpunkt, ein Knoppers raus zu holen. Bei uns sollte man um 03:30 h lieber von Knoppers träumen .

.

www.heise.de

www.heise.de

Am 3. Juni um 09:30 hält Lisa Su die Eröffnungs-Keynote auf der Computex. Wobei 09:30 h auch irgendwie relativ ist. Für die Taiwanesen ist das ein guter Zeitpunkt, ein Knoppers raus zu holen. Bei uns sollte man um 03:30 h lieber von Knoppers träumen

AMD bereitet sich auf Ryzen-9000-Vorstellung vor

Der aktuelle Chipsatztreiber kann bereits mit den Ryzen-9000-Prozessoren umgehen. Mainboard-Hersteller testen derzeit BIOS-Updates.

Zuletzt bearbeitet:

derDruide

Grand Admiral Special

- Mitglied seit

- 09.08.2004

- Beiträge

- 2.773

- Renomée

- 450

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 3900X

- Mainboard

- Asus Strix B450-F Gaming

- Kühlung

- Noctua NH-C14

- Speicher

- 32 GB DDR4-3200 CL14 FlareX

- Grafikprozessor

- Radeon RX 590

- Display

- 31.5" Eizo FlexScan EV3285

- SSD

- Corsair MP510 2 TB, Samsung 970 Evo 512 GB

- HDD

- Seagate Ironwulf 6 TB

- Optisches Laufwerk

- Plextor PX-880SA

- Soundkarte

- Creative SoundblasterX AE-7

- Gehäuse

- Antec P280

- Netzteil

- be quiet! Straight Power E9 400W

- Maus

- Logitech Trackman Marble (Trackball)

- Betriebssystem

- openSUSE 15.2

- Webbrowser

- Firefox

- Internetanbindung

- ▼50 MBit ▲10 MBit

Das bisher inoffiziell gehandelte "Ryzen 9000" wurde durch Gigabyte bestätigt:

Wichtiger und wirklich überraschend: AMDs Serverchip soll als EPYC 4004 auch in den AM5-Sockel kommen, auch mit X3D-Cache:

Wichtiger und wirklich überraschend: AMDs Serverchip soll als EPYC 4004 auch in den AM5-Sockel kommen, auch mit X3D-Cache:

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 14.717

- Renomée

- 2.125

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 3950X

- Mainboard

- MSI MPG X570 GAMING PRO CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 4x 16 GB G.Skill Trident Z RGB, DDR4-3200, CL14

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Intel 600p 1TB

- HDD

- Western Digital WD Red 2 & 3TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

Wer fühlt sich bei dem Namensschema noch an die wenig ruhmreiche erste Phenom Generation erinnert?

www.computerbase.de

www.computerbase.de

AMD Ryzen 9000: Spezifikationen zu 9950X, 9900X, 9700X, 9600X und Chipsätzen

Eine Präsentation nennt AMD Ryzen 9 9950X, Ryzen 9 9900X, Ryzen 7 9700X und Ryzen 5 9600. Erneut soll es bis zu 16 Kerne geben.

NEO83

Grand Admiral Special

- Mitglied seit

- 19.01.2016

- Beiträge

- 4.527

- Renomée

- 629

- Standort

- Wilhelmshaven

- BOINC-Statistiken

- Mein Desktopsystem

- Kraftprotz

- Mein Laptop

- ASUS TUF A17 @R9 7940HS @RTX4070 @EndeavourOS

- Details zu meinem Desktop

- Prozessor

- AMD R7 7800X3D

- Mainboard

- GIGABYTE B650E AORUS Master

- Kühlung

- Endorfy Navis F360 ARGB All-in-One

- Speicher

- Corsair Vengeance RGB Kit 32GB, DDR5-6000, CL30-36-36-76

- Grafikprozessor

- PNY GeForce RTX 4080 XLR8 Gaming Verto Epic-X

- Display

- MSI MAG 274UPFDE @UHD @144Hz

- SSD

- WD_BLACK SN850X 1TB, WD_BLACK SN850X 2TB

- Optisches Laufwerk

- USB BD-Brenner

- Soundkarte

- Onboard

- Gehäuse

- Fractal Design Meshify 2 XL

- Netzteil

- ASUS ROG Loki 1000W Platinum SFX-L

- Tastatur

- Logitech G815

- Maus

- Logitech G502 SE Lightspeed

- Betriebssystem

- Garuda Dr460nized Gaming Edition / Windows 11 64Bit

- Webbrowser

- FireFox

- Internetanbindung

- ▼1,15GBit ▲56MBit

Bei CB sind ganz viele total enttäuscht, ich kann das irgendwie garnicht verstehen ...

Ist das hier auch so?

Ich bin eigentlich positive überrascht, +16% IPC ... klar es gibt nicht mehr Takt aber warum auch? Der führte bei Intel schon einfach nur zu extrem hohen Verbräuchen ...

Ich würde es begrüßen wenn die neuen Ryzen 9000 tasächlich hauptsächlich effizienter zu werke gehen würden auch wenn ich mit meiner Entscheidung was ich kaufe auf jeden Fall noch bis zu den X3D Varianten warten werde ... ich hoffe hier tatsächlich diesesmal auf einen 9950X3D mit doppeltem 3D Chiplet, erst wenn das auf jeden Fall vom Tisch ist werde ich sehen was ich mache ...

Will jemand von euch zeitnah einen 9000er kaufen?

Ist das hier auch so?

Ich bin eigentlich positive überrascht, +16% IPC ... klar es gibt nicht mehr Takt aber warum auch? Der führte bei Intel schon einfach nur zu extrem hohen Verbräuchen ...

Ich würde es begrüßen wenn die neuen Ryzen 9000 tasächlich hauptsächlich effizienter zu werke gehen würden auch wenn ich mit meiner Entscheidung was ich kaufe auf jeden Fall noch bis zu den X3D Varianten warten werde ... ich hoffe hier tatsächlich diesesmal auf einen 9950X3D mit doppeltem 3D Chiplet, erst wenn das auf jeden Fall vom Tisch ist werde ich sehen was ich mache ...

Will jemand von euch zeitnah einen 9000er kaufen?

enigmation

Admiral Special

Ich finde, das passt schon, ist doch ungefähr der gleiche Performanceschritt wie zuvor bei den Ryzen 7000: Die X3D-Performance der Vorgängergeneration wird erreicht ohne X3D. Die Steigerung der Effizienz finde ich auch spannend, denn das macht auch den Unterschied zu Intel aus.

Aber erst mal auf unabhängige Tests im Juli warten, das sind ja jetzt erst mal nur Werte von AMD.

Aber erst mal auf unabhängige Tests im Juli warten, das sind ja jetzt erst mal nur Werte von AMD.

Gozu

Vice Admiral Special

- Mitglied seit

- 19.02.2017

- Beiträge

- 602

- Renomée

- 102

- Mein Laptop

- Asus ROG Zephyrus G14 2022 (GA402RJ-L8116W) / HP 15s-eq1158ng

- Details zu meinem Desktop

- Prozessor

- Ryzen R9 5900

- Mainboard

- AsRock B550 Phantom Gaming Velocita

- Kühlung

- Coolermaster MASTERLIQUID 120

- Speicher

- 2x 16GB HyperX KHX3733C19D4/16GX 3733-19

- Grafikprozessor

- AsRock RX 6800 Phantom Gaming D 16G

- Display

- 27 " iiyama G-Master GB2760QSU WQHD

- HDD

- 2x WDC WD10EADS-11P8B1

- Optisches Laufwerk

- TSSTcorp CDDVDW SH-2

- Gehäuse

- CoolerMaster HAF XB

- Netzteil

- Enermax EDT1250EWT

- Maus

- Rocat Kova

- Betriebssystem

- Windows 10 Professional x64, Manjaro

- Webbrowser

- Iron

- Internetanbindung

- ▼1000 MBit ▲50 MBit

Etwas schade ist daß bei Strix Point der RAM immer verlötet ist. Geht aber wohl nicht anders da die APU Grafik schnellen RAM benötigt.

eratte

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 11.11.2001

- Beiträge

- 22.497

- Renomée

- 3.059

- Standort

- Rheinberg / NRW

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- YoYo, Collatz

- Lieblingsprojekt

- YoYo

- Meine Systeme

- Wegen der aktuellen Lage alles aus.

- BOINC-Statistiken

- Mein Laptop

- Lenovo ThinkPad E15 Gen4 Intel / HP PAVILION 14-dk0002ng

- Details zu meinem Desktop

- Prozessor

- Ryzen R9 7950X

- Mainboard

- ASUS ROG Crosshair X670E Hero

- Kühlung

- Noctua NH-D15

- Speicher

- 2 x 32 GB G.Skill Trident Z DDR5 6000 CL30-40-40-96

- Grafikprozessor

- Sapphire Radeon RX7900XTX Gaming OC Nitro+

- Display

- 2 x ASUS XG27AQ (2560x1440@144 Hz)

- SSD

- Samsung 980 Pro 1 TB & Lexar NM790 4 TB

- Optisches Laufwerk

- USB Blu-Ray Brenner

- Soundkarte

- Onboard

- Gehäuse

- NEXT H7 Flow Schwarz

- Netzteil

- Corsair HX1000 (80+ Platinum)

- Tastatur

- ASUS ROG Strix Scope RX TKL Wireless / 2. Rechner&Server Cherry G80-3000N RGB TKL

- Maus

- ROG Gladius III Wireless / 2. Rechner&Server Sharkoon Light2 180

- Betriebssystem

- Windows 11 Pro 64

- Webbrowser

- Firefox

- Verschiedenes

- 4 x BQ Light Wings 14. 1 x NF-A14 Noctua Lüfter. Corsair HS80 Headset .

- Internetanbindung

- ▼VDSL 100 ▲VDSL 100

Das kann sich mit LPCAMM2 ändern wenn sich das weiter durch setzt und es die Hersteller auch bei AMD Notebooks anbieten.

Erste RAM Hersteller bieten schon entsprechende Module.

Erste RAM Hersteller bieten schon entsprechende Module.

NEO83

Grand Admiral Special

- Mitglied seit

- 19.01.2016

- Beiträge

- 4.527

- Renomée

- 629

- Standort

- Wilhelmshaven

- BOINC-Statistiken

- Mein Desktopsystem

- Kraftprotz

- Mein Laptop

- ASUS TUF A17 @R9 7940HS @RTX4070 @EndeavourOS

- Details zu meinem Desktop

- Prozessor

- AMD R7 7800X3D

- Mainboard

- GIGABYTE B650E AORUS Master

- Kühlung

- Endorfy Navis F360 ARGB All-in-One

- Speicher

- Corsair Vengeance RGB Kit 32GB, DDR5-6000, CL30-36-36-76

- Grafikprozessor

- PNY GeForce RTX 4080 XLR8 Gaming Verto Epic-X

- Display

- MSI MAG 274UPFDE @UHD @144Hz

- SSD

- WD_BLACK SN850X 1TB, WD_BLACK SN850X 2TB

- Optisches Laufwerk

- USB BD-Brenner

- Soundkarte

- Onboard

- Gehäuse

- Fractal Design Meshify 2 XL

- Netzteil

- ASUS ROG Loki 1000W Platinum SFX-L

- Tastatur

- Logitech G815

- Maus

- Logitech G502 SE Lightspeed

- Betriebssystem

- Garuda Dr460nized Gaming Edition / Windows 11 64Bit

- Webbrowser

- FireFox

- Internetanbindung

- ▼1,15GBit ▲56MBit

eiernacken1983

Admiral Special

- Mitglied seit

- 18.06.2020

- Beiträge

- 1.725

- Renomée

- 1.140

- Aktuelle Projekte

- Rosetta@Home, Milkyway@Home; Einstein@Home

- Lieblingsprojekt

- MW@H

- Meine Systeme

- 3990X+2 x Radeon VII; 3950X + Radeon VII; 5950X + 5700XT; 3950X + Vega 64

- BOINC-Statistiken

- Folding@Home-Statistiken

- Details zu meinem Desktop

- Prozessor

- Ryzen 9 5950X

- Mainboard

- Gigabyte X570 Aorus Pro

- Kühlung

- Noctua NH-D15

- Speicher

- 4 x 8 GB G.Skill @ 3600 Cl16

- Grafikprozessor

- RX 5700XT Anniversary Edition

- Betriebssystem

- Windows 10

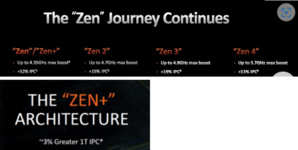

Wenn man sich mal anschaut, was wir bei den letzten Wechseln an IPC-Uplift hatten, dann sind 16 % doch ein guter Wert (der zweithöchste seit Zen+)

Zen+: +3 %

Zen2: +15 %

Zen3: +19 %

Zen 4 +13 %

Zen 5 +16 %

Für mich am wichtigsten ist dann immer, was bei BOINC im ECO-Mode davon übrig bleibt. Hier hat mich z.B. Zen 3 beim Anwendungsfall BOINC eher negativ überrascht, wo mein 5950X ggü. den 3950X 300-500 MHz weniger schafft.

Für die BOINC-Liebhaber unter uns würde ich aber spekulieren, dass Zen 5 gut werden könnte: breitere Pipelines und Absenkung der TDP bei 3 von 4 Modellen. Das nährt zumindest bei mir die Hoffnung, dass im ECO-Mode was geht.

Auch ich schiele eher auf die Modelle mit 3d-Cache und würde mir hier einen 9950Doppel-3D wünschen. Ich befürchte aber, dass man den Cache weiterhin nur auf ein CCD stapelt, um weiterhin das Beste beider Welten abbilden zu können.

Zen+: +3 %

Zen2: +15 %

Zen3: +19 %

Zen 4 +13 %

Zen 5 +16 %

Für mich am wichtigsten ist dann immer, was bei BOINC im ECO-Mode davon übrig bleibt. Hier hat mich z.B. Zen 3 beim Anwendungsfall BOINC eher negativ überrascht, wo mein 5950X ggü. den 3950X 300-500 MHz weniger schafft.

Für die BOINC-Liebhaber unter uns würde ich aber spekulieren, dass Zen 5 gut werden könnte: breitere Pipelines und Absenkung der TDP bei 3 von 4 Modellen. Das nährt zumindest bei mir die Hoffnung, dass im ECO-Mode was geht.

Auch ich schiele eher auf die Modelle mit 3d-Cache und würde mir hier einen 9950Doppel-3D wünschen. Ich befürchte aber, dass man den Cache weiterhin nur auf ein CCD stapelt, um weiterhin das Beste beider Welten abbilden zu können.

NEO83

Grand Admiral Special

- Mitglied seit

- 19.01.2016

- Beiträge

- 4.527

- Renomée

- 629

- Standort

- Wilhelmshaven

- BOINC-Statistiken

- Mein Desktopsystem

- Kraftprotz

- Mein Laptop

- ASUS TUF A17 @R9 7940HS @RTX4070 @EndeavourOS

- Details zu meinem Desktop

- Prozessor

- AMD R7 7800X3D

- Mainboard

- GIGABYTE B650E AORUS Master

- Kühlung

- Endorfy Navis F360 ARGB All-in-One

- Speicher

- Corsair Vengeance RGB Kit 32GB, DDR5-6000, CL30-36-36-76

- Grafikprozessor

- PNY GeForce RTX 4080 XLR8 Gaming Verto Epic-X

- Display

- MSI MAG 274UPFDE @UHD @144Hz

- SSD

- WD_BLACK SN850X 1TB, WD_BLACK SN850X 2TB

- Optisches Laufwerk

- USB BD-Brenner

- Soundkarte

- Onboard

- Gehäuse

- Fractal Design Meshify 2 XL

- Netzteil

- ASUS ROG Loki 1000W Platinum SFX-L

- Tastatur

- Logitech G815

- Maus

- Logitech G502 SE Lightspeed

- Betriebssystem

- Garuda Dr460nized Gaming Edition / Windows 11 64Bit

- Webbrowser

- FireFox

- Internetanbindung

- ▼1,15GBit ▲56MBit

Ja der 9950X oder eben 9950X3D sind meine erklärten Wunsch Upgrades gerade wegen BOINC aber mal sehen ... wie wir ja gesehen haben benötigen manche, wenn auch behämmerte Projekte den großen 3D Cache

eratte

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 11.11.2001

- Beiträge

- 22.497

- Renomée

- 3.059

- Standort

- Rheinberg / NRW

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- YoYo, Collatz

- Lieblingsprojekt

- YoYo

- Meine Systeme

- Wegen der aktuellen Lage alles aus.

- BOINC-Statistiken

- Mein Laptop

- Lenovo ThinkPad E15 Gen4 Intel / HP PAVILION 14-dk0002ng

- Details zu meinem Desktop

- Prozessor

- Ryzen R9 7950X

- Mainboard

- ASUS ROG Crosshair X670E Hero

- Kühlung

- Noctua NH-D15

- Speicher

- 2 x 32 GB G.Skill Trident Z DDR5 6000 CL30-40-40-96

- Grafikprozessor

- Sapphire Radeon RX7900XTX Gaming OC Nitro+

- Display

- 2 x ASUS XG27AQ (2560x1440@144 Hz)

- SSD

- Samsung 980 Pro 1 TB & Lexar NM790 4 TB

- Optisches Laufwerk

- USB Blu-Ray Brenner

- Soundkarte

- Onboard

- Gehäuse

- NEXT H7 Flow Schwarz

- Netzteil

- Corsair HX1000 (80+ Platinum)

- Tastatur

- ASUS ROG Strix Scope RX TKL Wireless / 2. Rechner&Server Cherry G80-3000N RGB TKL

- Maus

- ROG Gladius III Wireless / 2. Rechner&Server Sharkoon Light2 180

- Betriebssystem

- Windows 11 Pro 64

- Webbrowser

- Firefox

- Verschiedenes

- 4 x BQ Light Wings 14. 1 x NF-A14 Noctua Lüfter. Corsair HS80 Headset .

- Internetanbindung

- ▼VDSL 100 ▲VDSL 100

IPC ja aber kein höherer Takt noch dazu - daher eher etwas weniger Steigerung.

E555user

Admiral Special

- Mitglied seit

- 05.10.2015

- Beiträge

- 1.693

- Renomée

- 671

Die IPC legt doch lt. AMD zwischen 10% und bis zu 35% zu. Alle Gerüchte sind demnach "richtig" gewesen.

Dass AMD nun Anwendungen gewählt hat um den Mittelwert mit 16% anzugeben ist eine Marketingentscheidung. Mit LoL und FarCry hat man nur zwei Spiele gelistet, die im Mittel bei 15.5 liegen würden

MLID hatte von Anfang an 15%+ in seinen Leaks genannt. Das Plus von 21% in LoL ist aber wirklich stark und lässt auf eine sehr gute Gaming-CPU schliessen, auch schon ohne X3D.

AM5 hat nun minimum 2027+ im Plattformsupport bekommen. Das Statment war doch sehr zentral. Womöglich werden mit der nächsten Zen-Generation nochmals ein bis 2 Jahre hinzugefügt, war bei AM4 ähnlich.

Leider gibt es nur bei den kleineren Modellen minime Taktsteigerung. Die Fertigung hat hier nichts erreicht dafür aber breiteres Design mit (nativem) AVX512 ermöglicht. Eine abwägende Enscheidung, beides ging wohl nicht.

Wichtig war auch die Aussage, mit doppelter AVX512 Performance erreicht man doppelte AI-Leistung. Das bedeutet doch letztlich, dass AMD zunächst nur auf flexible AVX setzt um mit Desktop- und Serverprozessoren KI-Engines in den APIs abzubilden. Falls die AVX512 mit voller Breite nicht wie bei Intel den Takt signifikant drücken muss hat man denen letztlich aufgezeigt wie es "richtig" gehen kann. Gerade wo Intel AVX512 Support eher abzubauen scheint und auf NPUs auch im Desktops setzen will. Einem Prozessor anzudichten (wie ich anderonorts gelesen hatte) er würde kein Copilot+ bekommen, wenn er keine NPU hätte ist auch etwas zu weit vorgegriffen. Schliesslich lässt sich ein NPU auch in der CPU oder GPU in Form eines Treibers abbilden, hier wird nicht gegen eine spezifische NPU ISA kompiliert, es gibt eine "HAL".

Was mir fehlt ist eine Information zum Infinity Fabric zwischen den Core-Dies. Es gab keine Aussage zur Senkung von Latenzen im gegenseitigen Cache-Zugriff. Allerdings ist der Cache in Zen5 auch doppelt breit angebunden und hat weniger Latenz. Das könnte dazu führen, dass es wieder wichtiger wird einzelne Threads auf einem Chiplet-Die zu halten.

Dass AMD nun Anwendungen gewählt hat um den Mittelwert mit 16% anzugeben ist eine Marketingentscheidung. Mit LoL und FarCry hat man nur zwei Spiele gelistet, die im Mittel bei 15.5 liegen würden

MLID hatte von Anfang an 15%+ in seinen Leaks genannt. Das Plus von 21% in LoL ist aber wirklich stark und lässt auf eine sehr gute Gaming-CPU schliessen, auch schon ohne X3D.

AM5 hat nun minimum 2027+ im Plattformsupport bekommen. Das Statment war doch sehr zentral. Womöglich werden mit der nächsten Zen-Generation nochmals ein bis 2 Jahre hinzugefügt, war bei AM4 ähnlich.

Leider gibt es nur bei den kleineren Modellen minime Taktsteigerung. Die Fertigung hat hier nichts erreicht dafür aber breiteres Design mit (nativem) AVX512 ermöglicht. Eine abwägende Enscheidung, beides ging wohl nicht.

Wichtig war auch die Aussage, mit doppelter AVX512 Performance erreicht man doppelte AI-Leistung. Das bedeutet doch letztlich, dass AMD zunächst nur auf flexible AVX setzt um mit Desktop- und Serverprozessoren KI-Engines in den APIs abzubilden. Falls die AVX512 mit voller Breite nicht wie bei Intel den Takt signifikant drücken muss hat man denen letztlich aufgezeigt wie es "richtig" gehen kann. Gerade wo Intel AVX512 Support eher abzubauen scheint und auf NPUs auch im Desktops setzen will. Einem Prozessor anzudichten (wie ich anderonorts gelesen hatte) er würde kein Copilot+ bekommen, wenn er keine NPU hätte ist auch etwas zu weit vorgegriffen. Schliesslich lässt sich ein NPU auch in der CPU oder GPU in Form eines Treibers abbilden, hier wird nicht gegen eine spezifische NPU ISA kompiliert, es gibt eine "HAL".

Was mir fehlt ist eine Information zum Infinity Fabric zwischen den Core-Dies. Es gab keine Aussage zur Senkung von Latenzen im gegenseitigen Cache-Zugriff. Allerdings ist der Cache in Zen5 auch doppelt breit angebunden und hat weniger Latenz. Das könnte dazu führen, dass es wieder wichtiger wird einzelne Threads auf einem Chiplet-Die zu halten.

Zuletzt bearbeitet:

NEO83

Grand Admiral Special

- Mitglied seit

- 19.01.2016

- Beiträge

- 4.527

- Renomée

- 629

- Standort

- Wilhelmshaven

- BOINC-Statistiken

- Mein Desktopsystem

- Kraftprotz

- Mein Laptop

- ASUS TUF A17 @R9 7940HS @RTX4070 @EndeavourOS

- Details zu meinem Desktop

- Prozessor

- AMD R7 7800X3D

- Mainboard

- GIGABYTE B650E AORUS Master

- Kühlung

- Endorfy Navis F360 ARGB All-in-One

- Speicher

- Corsair Vengeance RGB Kit 32GB, DDR5-6000, CL30-36-36-76

- Grafikprozessor

- PNY GeForce RTX 4080 XLR8 Gaming Verto Epic-X

- Display

- MSI MAG 274UPFDE @UHD @144Hz

- SSD

- WD_BLACK SN850X 1TB, WD_BLACK SN850X 2TB

- Optisches Laufwerk

- USB BD-Brenner

- Soundkarte

- Onboard

- Gehäuse

- Fractal Design Meshify 2 XL

- Netzteil

- ASUS ROG Loki 1000W Platinum SFX-L

- Tastatur

- Logitech G815

- Maus

- Logitech G502 SE Lightspeed

- Betriebssystem

- Garuda Dr460nized Gaming Edition / Windows 11 64Bit

- Webbrowser

- FireFox

- Internetanbindung

- ▼1,15GBit ▲56MBit

AM5 hat nun minimum 2027+ im Plattformsupport bekommen. Das Statment war doch sehr zentral. Womöglich werden mit der nächsten Zen-Generation nochmals ein bis 2 Jahre hinzugefügt, war bei AM4 ähnlich.

Aufpassen, laut AMD lebt der Sockel zwar solange allerdings wird AM6 wohl vorher erscheinen und somit wird AM5 vermutlich ein ähnliches dasein wie AM4 fristen ab der Generation nach den 9000er ... ich vermute das AMD danach vllt auch zu den 3er Bezeichnungen im Desktop wechselt wie sie es Mobil schon machen und dann auch eine NPU verbauen werden ...

Ähnliche Themen

- Antworten

- 32

- Aufrufe

- 2K

- Antworten

- 1

- Aufrufe

- 258

- Antworten

- 15

- Aufrufe

- 2K

- Antworten

- 462

- Aufrufe

- 45K

- Antworten

- 31

- Aufrufe

- 3K