App installieren

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: This feature may not be available in some browsers.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

News Analyse der vermuteten Zen-Architektur

Opteron

Redaktion

☆☆☆☆☆☆

Schon im März wussten wir über ein erstes Codefragment zu AMDs kommender Zen-Architektur zu berichten. Erstmals wurde hier der Befehlssatz angegeben, der alle modernen Erweiterungen bis AVX2 und FMA umfasst. Unser Forenmitglied Dresdenboy hat in seinem englischsprachigen Blog nun über weitere Details berichtet und ein Blockschaltbild entworfen, welches Zen nach aktuellem Wissensstand, gewürzt mit einigen Vermutungen, zeigen könnte. Auf dessen Basis haben wir eine detaillierte Darstellung erstellt und ziehen einen Vergleich mit Skylake.

(…)

» Artikel lesen

Zuletzt bearbeitet:

bschicht86

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 14.12.2006

- Beiträge

- 4.241

- Renomée

- 231

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- 2950X

- Mainboard

- X399 Taichi

- Kühlung

- Heatkiller IV Pure Chopper

- Speicher

- 64GB 3466 CL16

- Grafikprozessor

- 2x Vega 64 @Heatkiller

- Display

- Asus VG248QE

- SSD

- PM981, SM951, ein paar MX500 (~5,3TB)

- HDD

- -

- Optisches Laufwerk

- 1x BH16NS55 mit UHD-BD-Mod

- Soundkarte

- Audigy X-Fi Titanium Fatal1ty Pro

- Gehäuse

- Chieftec

- Netzteil

- Antec HCP-850 Platinum

- Betriebssystem

- Win7 x64, Win10 x64

- Webbrowser

- Firefox

- Verschiedenes

- LS120 mit umgebastelten USB -> IDE (Format wie die gängigen SATA -> IDE)

Schöner und wirklich (mit aktuellen Erkenntnissen) tiefgreifender Artikel!

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 14.717

- Renomée

- 2.125

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 3950X

- Mainboard

- MSI MPG X570 GAMING PRO CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 4x 16 GB G.Skill Trident Z RGB, DDR4-3200, CL14

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Intel 600p 1TB

- HDD

- Western Digital WD Red 2 & 3TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

Schön anschaulich aufbereitet und neutral rüber gebracht.

bbott

Grand Admiral Special

- Mitglied seit

- 11.11.2001

- Beiträge

- 4.363

- Renomée

- 60

- Mein Laptop

- HP Compaq 8510p

- Details zu meinem Desktop

- Prozessor

- AMD FX-8370

- Mainboard

- Asus M5A99X

- Kühlung

- Corsair H60

- Speicher

- 16GB DDR3-1866 Crucial

- Grafikprozessor

- Sapphire HD5770

- Display

- 4k 27" DELL

- SSD

- Samsung Evo 850

- HDD

- 2x Seagate 7200.12

- Optisches Laufwerk

- Pioneer, Plextor

- Soundkarte

- Creative X-Fi Xtreme Music

- Gehäuse

- Silverstone TJ-02S

- Netzteil

- Enermax 450W

- Betriebssystem

- Windows 7

@Opteron, der Danke Button für den Artikel fehlt leider. Also ein fettes Danke von mir

Yoshi 2k3

Admiral Special

- Mitglied seit

- 18.01.2003

- Beiträge

- 1.375

- Renomée

- 210

- BOINC-Statistiken

- Mein Laptop

- Apple Mac Book Pro 14" 2023

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7800X3D

- Mainboard

- ASUS PRIME X670E-PRO WIFI

- Kühlung

- Watercool Heatkiller IV

- Speicher

- 64 GB Team Group DDR5-6400 (2x 32 GB)

- Grafikprozessor

- AMD Radeon RX 6950 XT

- Display

- Nixeus NX-EDG27

- Soundkarte

- SMSL SU-9 USB DAC

- Gehäuse

- Caselabs SM8

- Netzteil

- FSP Hydro Ti Pro 1000W

- Betriebssystem

- Windows 11 Pro

- Webbrowser

- Firefox

- Schau Dir das System auf sysprofile.de an

Sehr guter Artikel, das macht eben P3Dnow! aus.

bbott

Grand Admiral Special

- Mitglied seit

- 11.11.2001

- Beiträge

- 4.363

- Renomée

- 60

- Mein Laptop

- HP Compaq 8510p

- Details zu meinem Desktop

- Prozessor

- AMD FX-8370

- Mainboard

- Asus M5A99X

- Kühlung

- Corsair H60

- Speicher

- 16GB DDR3-1866 Crucial

- Grafikprozessor

- Sapphire HD5770

- Display

- 4k 27" DELL

- SSD

- Samsung Evo 850

- HDD

- 2x Seagate 7200.12

- Optisches Laufwerk

- Pioneer, Plextor

- Soundkarte

- Creative X-Fi Xtreme Music

- Gehäuse

- Silverstone TJ-02S

- Netzteil

- Enermax 450W

- Betriebssystem

- Windows 7

Zu Skylake gib es nun die Folien:

http://www.3dcenter.org/news/blockschalt-diagramm-zu-intels-skylake-architektur

Also kann ein Update des Artikel gemacht werden, allerdings sind diese so klein das es langweilig ist.

http://www.3dcenter.org/news/blockschalt-diagramm-zu-intels-skylake-architektur

Also kann ein Update des Artikel gemacht werden, allerdings sind diese so klein das es langweilig ist.

Opteron

Redaktion

☆☆☆☆☆☆

Zu Skylake gib es nun die Folien:

http://www.3dcenter.org/news/blockschalt-diagramm-zu-intels-skylake-architektur

Also kann ein Update des Artikel gemacht werden, allerdings sind diese so klein das es langweilig ist.

Öh was meinst Du genau, welches Update sollte es geben? Das Skylake PDF (meinst Du das mit Folien?) kannte ich schon, davon hab ich doch das Architekturbild kopiert.

--- Update ---

Jupp, das wissen wissen wir aber schon seit dem Compiler-Patch im März zu den Befehlssatzerweiterungen.Aber Transactional Memory wird Zen nicht haben ...

WindHund

Grand Admiral Special

- Mitglied seit

- 30.01.2008

- Beiträge

- 12.238

- Renomée

- 538

- Standort

- Im wilden Süden (0711)

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- NumberFields@home

- Lieblingsprojekt

- none, try all

- Meine Systeme

- RYZEN R9 3900XT @ ASRock Taichi X570 & ASUS RX Vega64

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5950X

- Mainboard

- ASRock 570X Taichi P5.05 Certified

- Kühlung

- AlphaCool Eisblock XPX, 366x40mm Radiator 6l Brutto m³

- Speicher

- 2x 16 GiB DDR4-3600 CL26 Kingston (Dual Rank, unbuffered ECC)

- Grafikprozessor

- 1x ASRock Radeon RX 6950XT Formula OC 16GByte GDDR6 VRAM

- Display

- SAMSUNG Neo QLED QN92BA 43" up to 4K@144Hz FreeSync PP HDR10+

- SSD

- WD_Black SN850 PCI-Express 4.0 NVME

- HDD

- 3 Stück

- Optisches Laufwerk

- 1x HL-DT-ST BD-RE BH10LS30 SATA2

- Soundkarte

- HD Audio (onboard)

- Gehäuse

- SF-2000 Big Tower

- Netzteil

- Corsair RM1000X (80+ Gold)

- Tastatur

- Habe ich

- Maus

- Han I

- Betriebssystem

- Windows 10 x64 Professional (up to date!)

- Webbrowser

- @Chrome.Google & Edge Chrome

@Opteron

Feiner Artikel, aber mir fällt es gerade echt schwer mir ein Reim daraus zu machen.

Mir fehlen da der Speicher und die System-Anbindung, ein nicht zu Unterschätzender Faktor.

Feiner Artikel, aber mir fällt es gerade echt schwer mir ein Reim daraus zu machen.

Mir fehlen da der Speicher und die System-Anbindung, ein nicht zu Unterschätzender Faktor.

pipip

Captain Special

- Mitglied seit

- 17.03.2011

- Beiträge

- 209

- Renomée

- 2

- Mein Laptop

- HP625

- Details zu meinem Laptop

- Prozessor

- N930@2Ghz , 0,9250Volt

- Speicher

- 4gig

- Grafikprozessor

- AMD HD4200

Transaktionaler Speicher kann entweder komplett als Software (STM), als Hardware (HTM) oder mit Hardware-Unterstützung (Hybrid-HTM) implementiert werden.

Aber eine andere Frage. Hat Haswell nicht einen Bug, wenn es um TSX geht und ist hier nicht deaktiviert. Somit ist Skylake der aktuelle Prozessor der davon in Genuss kommt. Außerdem für den Konsumenten wird es egal sein, ob der bei Zen vorhanden ist. Wie es bei Server aussieht, ist eine andere Sache.

Weiteres finde ich es gut dass hier 4 mal 128Bit FPU vorhanden sind. Eventuell kann Zen bei aktueller Software somit aufholen. Zen macht aktuell einen AMD atypischen Eindruck. Anstatt weit in die Zukunft auszuholen, irgendwelche speziellen eigenentwickelte SIMD ect zu integrieren, sehen wir einen Prozessor, der eventuell aktueller und nahe kommende Software gut zugeschnitten ist.

At least ist das mein Eindruck den ich durch diesen Artikel gewinnen kann.

WindHund

Was die Speicheranbindung angeht, vllt kann man hier nach Carrizo schielen, weil der ZEN FX und Carrizo Refresh die selbe Plattform, sprich AM4 unterstützten.

bschicht86

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 14.12.2006

- Beiträge

- 4.241

- Renomée

- 231

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- 2950X

- Mainboard

- X399 Taichi

- Kühlung

- Heatkiller IV Pure Chopper

- Speicher

- 64GB 3466 CL16

- Grafikprozessor

- 2x Vega 64 @Heatkiller

- Display

- Asus VG248QE

- SSD

- PM981, SM951, ein paar MX500 (~5,3TB)

- HDD

- -

- Optisches Laufwerk

- 1x BH16NS55 mit UHD-BD-Mod

- Soundkarte

- Audigy X-Fi Titanium Fatal1ty Pro

- Gehäuse

- Chieftec

- Netzteil

- Antec HCP-850 Platinum

- Betriebssystem

- Win7 x64, Win10 x64

- Webbrowser

- Firefox

- Verschiedenes

- LS120 mit umgebastelten USB -> IDE (Format wie die gängigen SATA -> IDE)

@Opteron

Feiner Artikel, aber mir fällt es gerade echt schwer mir ein Reim daraus zu machen.

Mir fehlen da der Speicher und die System-Anbindung, ein nicht zu Unterschätzender Faktor.

Speicher sollte klar sein (DDR4). Mit welcher Taktfrequenz vs. Latenz vom RAM Zen am Ende am besten skaliert, muss wohl erst noch herausgefunden werden.

Systemanbindung ist da so eine Sache. Entweder alles bereits integriert (USB, SATA, PCI-E) oder wieder ein schnellerer HT-Link oder sogar beides (HT für hochausgestattete Mainboards als Zusatzoption)

Allerdings wäre dann gerade im Hinblick auf CF/SLI wünschenswert, wenn alle PCI-E-Lanes aus einer Quelle kämen.

Es gibt auch parallele Software für den Consumer, die von HLE und RTM Gebrauch machen kann.Außerdem für den Konsumenten wird es egal sein, ob der bei Zen vorhanden ist.

Opteron

Redaktion

☆☆☆☆☆☆

Naja, so wichtig ist der nicht, Intel hat den gleichen Dual-Channel DDR3 wie Bulldozer und wie siehts leistungsmäßig aus?@Opteron

Feiner Artikel, aber mir fällt es gerade echt schwer mir ein Reim daraus zu machen.

Mir fehlen da der Speicher und die System-Anbindung, ein nicht zu Unterschätzender Faktor.

14nm Designs werden noch größere Caches haben - hoff ich zumindest ^^ - von daher muss man sich ums RAM nicht mehr groß kümmern. Außer man hetzt der letzten Nachkommastelle im Bench xy nach

Zu erwarten ist wohl Dual-Channel DDR4.

Gespannt bin ich auf die PCIe-Anbindung, ich hoff da immer noch auf ne Verbesserung nachdem der Sockel AM4 getauft wurde, obwohl die Leaks vorher immer von FM3 sprachen.

bbott

Grand Admiral Special

- Mitglied seit

- 11.11.2001

- Beiträge

- 4.363

- Renomée

- 60

- Mein Laptop

- HP Compaq 8510p

- Details zu meinem Desktop

- Prozessor

- AMD FX-8370

- Mainboard

- Asus M5A99X

- Kühlung

- Corsair H60

- Speicher

- 16GB DDR3-1866 Crucial

- Grafikprozessor

- Sapphire HD5770

- Display

- 4k 27" DELL

- SSD

- Samsung Evo 850

- HDD

- 2x Seagate 7200.12

- Optisches Laufwerk

- Pioneer, Plextor

- Soundkarte

- Creative X-Fi Xtreme Music

- Gehäuse

- Silverstone TJ-02S

- Netzteil

- Enermax 450W

- Betriebssystem

- Windows 7

Öh was meinst Du genau, welches Update sollte es geben? Das Skylake PDF (meinst Du das mit Folien?) kannte ich schon, davon hab ich doch das Architekturbild kopiert..

Stimmt, ich dachte da wäre etwas neues dabei.

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.962

- Renomée

- 446

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Klasse Artikel

Zumal AMD eine eigene Implementierung besitzt: ASF http://developer.amd.com/community/...d-synchronization-facility-asf-specification/

http://www.realworldtech.com/haswell-tm/4/

Ist auch derzeit unnütz. Zumal auch erst ab 16 Threads und grossen Speichermengen relevant.Aber Transactional Memory wird Zen nicht haben ...

Zumal AMD eine eigene Implementierung besitzt: ASF http://developer.amd.com/community/...d-synchronization-facility-asf-specification/

http://www.realworldtech.com/haswell-tm/4/

AMD is continuing to work on ASF, which has several substantive differences from TSX; privileged instructions, forward progress guarantees and an absence of register rollback on abort are just a few examples. AMD and Intel face a choice, fragmenting the x86 ecosystem with incompatible extensions, or harmonizing ASF and TSX. From an industry standpoint, the latter is clearly preferable, and there is a risk that software vendors may be unwilling to tolerate such incompatibilities. However, it could take years for Intel and AMD to align their implementations.

Ist auch derzeit unnütz. Zumal auch erst ab 16 Threads und grossen Speichermengen relevant.

Das kann man so pauschal nicht sagen. Das ist von Benchmark zu Benchmark unterschiedlich. Und mit großen Datenmengen hat das nichts zu tun, denn es wird der L2-Cache als Transaktionspuffer genutzt, und der begrenzt eine Transaktion auf 256kB.

SAP HANA profitiert von TSX übrigens massiv.

Außerdem besitzt AMD keine Implementierung, sondern hat vor 6 Jahren Transactional Memory spezifiziert, und nie implementiert. Du kannst davon ausgehen, dass AMD keine inkompatible Lösung implementieren wird, sondern irgendwann TSX.

Zuletzt bearbeitet:

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.962

- Renomée

- 446

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Relevanz?Das kann man so pauschal nicht sagen. Das ist von Benchmark zu Benchmark unterschiedlich. Und mit großen Datenmengen hat das nichts zu tun, denn es wird der L2-Cache als Transaktionspuffer genutzt, und der begrenzt eine Transaktion auf 256kB.

Irgendein SAP HANA System mit weniger als 16 Threads?SAP HANA profitiert von TSX übrigens massiv.

Link lesen?Außerdem besitzt AMD keine Implementierung, sondern hat vor 6 Jahren Transactional Memory spezifiziert, und nie implementiert. Du kannst davon ausgehen, dass AMD keine inkompatible Lösung implementieren wird, sondern irgendwann TSX.

Zumal AMD eine eigene Implementierung besitzt: ASF http://developer.amd.com/community/b...specification/

Opteron

Redaktion

☆☆☆☆☆☆

Was ist unter 4fach SMT zu verstehen?

4 Threads pro Kern anstatt 2 wie bei Hyperthreading.

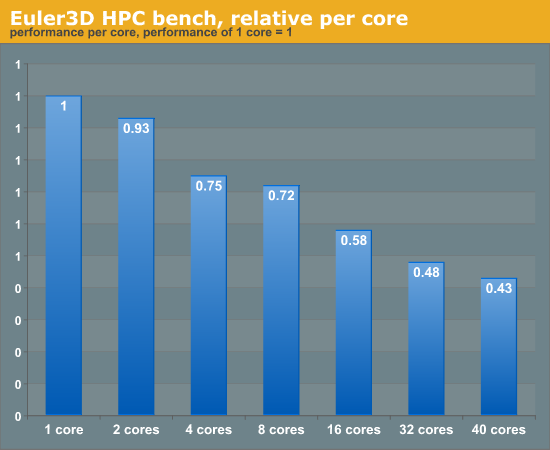

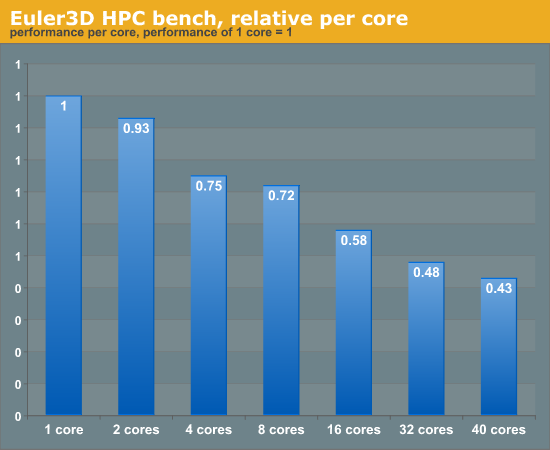

Die Single-Thread Performance würde darunter natürlich leiden, aber der Gesamtdurchsatz und damit auch Perf/Watt könnte - bei stark parallelisierbaren Aufgaben - steigen.

Für den Endanwender eher uninteressant - abgesehen natürlich von unsere Boinc-Gruppe

SPINA

Grand Admiral Special

- Mitglied seit

- 07.12.2003

- Beiträge

- 18.122

- Renomée

- 986

- Mein Laptop

- Lenovo IdeaPad Gaming 3 (15ARH05-82EY003NGE)

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- ASUS ProArt B550-Creator

- Kühlung

- AMD Wraith Prism

- Speicher

- 2x Micron 32GB PC4-25600E (MTA18ASF4G72AZ-3G2R)

- Grafikprozessor

- Sapphire Pulse Radeon RX 7600 8GB

- Display

- LG Electronics 27UD58P-B

- SSD

- Samsung 980 PRO (MZ-V8P1T0CW)

- HDD

- 2x Samsung 870 QVO (MZ-77Q2T0BW)

- Optisches Laufwerk

- HL Data Storage BH16NS55

- Gehäuse

- Lian Li PC-7NB

- Netzteil

- Seasonic PRIME Gold 650W

- Betriebssystem

- Debian 12.x (x86-64)

- Verschiedenes

- ASUS TPM-M R2.0

Der Link bestätigt Elcaros Aussage. Hast du ihn selbst gelesen?Link lesen?

Allerdings würde ich ASF und TSX nicht vergleichen wollen. Die Ausrichtung ist nicht deckungsgleich.ASF is an experimental architecture extension currently in proposal stage.

AMD has not yet committed to including this feature into any future CPU product.

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.962

- Renomée

- 446

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Also echt jetzt. Lies zumindest mal meine Beiträge.

AMD is continuing to work on ASF, which has several substantive differences from TSX; privileged instructions, forward progress guarantees and an absence of register rollback on abort are just a few examples. AMD and Intel face a choice, fragmenting the x86 ecosystem with incompatible extensions, or harmonizing ASF and TSX.

SPINA

Grand Admiral Special

- Mitglied seit

- 07.12.2003

- Beiträge

- 18.122

- Renomée

- 986

- Mein Laptop

- Lenovo IdeaPad Gaming 3 (15ARH05-82EY003NGE)

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- ASUS ProArt B550-Creator

- Kühlung

- AMD Wraith Prism

- Speicher

- 2x Micron 32GB PC4-25600E (MTA18ASF4G72AZ-3G2R)

- Grafikprozessor

- Sapphire Pulse Radeon RX 7600 8GB

- Display

- LG Electronics 27UD58P-B

- SSD

- Samsung 980 PRO (MZ-V8P1T0CW)

- HDD

- 2x Samsung 870 QVO (MZ-77Q2T0BW)

- Optisches Laufwerk

- HL Data Storage BH16NS55

- Gehäuse

- Lian Li PC-7NB

- Netzteil

- Seasonic PRIME Gold 650W

- Betriebssystem

- Debian 12.x (x86-64)

- Verschiedenes

- ASUS TPM-M R2.0

Du stellst dich heute aber an. Ich wollte nur mit einem sprachlichen Missverständnis aufräumen:

Ander als TSX, welches in Haswell, Broadwell und Skylake (teils experimentell) bereits implementiert wurde.

Elcaros hat nicht mehr und nicht weniger gesagt, dass ASF zwar spezifiziert ist, aber noch in der Praxis angelangt ist.Also echt jetzt. Lies zumindest mal meine Beiträge.

Ander als TSX, welches in Haswell, Broadwell und Skylake (teils experimentell) bereits implementiert wurde.

Opteron

Redaktion

☆☆☆☆☆☆

HMm .. ASF ... hatten wir mal Anno dazumal besprochen.

Würde mich nicht wundern, wenn das in der Zwischenzeit gestrichen und der/die Verantwortlichen entlassen wurden. Für Zen wird für solche Sonderfunktionen wohl erstmal kein Platz gewesen sein, aber schauen wir mal.

Würde mich nicht wundern, wenn das in der Zwischenzeit gestrichen und der/die Verantwortlichen entlassen wurden. Für Zen wird für solche Sonderfunktionen wohl erstmal kein Platz gewesen sein, aber schauen wir mal.

Ähnliche Themen

- Antworten

- 12

- Aufrufe

- 3K

- Antworten

- 18

- Aufrufe

- 5K

- Antworten

- 781

- Aufrufe

- 106K

- Antworten

- 111

- Aufrufe

- 17K

- Antworten

- 0

- Aufrufe

- 143K