App installieren

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: This feature may not be available in some browsers.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Bulldozer 2.0 / BDver2: Sepang, Terramar, Komodo, Trinity, Vishera

WindHund

Grand Admiral Special

- Mitglied seit

- 30.01.2008

- Beiträge

- 12.225

- Renomée

- 536

- Standort

- Im wilden Süden (0711)

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- NumberFields@home

- Lieblingsprojekt

- none, try all

- Meine Systeme

- RYZEN R9 3900XT @ ASRock Taichi X570 & ASUS RX Vega64

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5950X

- Mainboard

- ASRock 570X Taichi P5.05 Certified

- Kühlung

- AlphaCool Eisblock XPX, 366x40mm Radiator 6l Brutto m³

- Speicher

- 2x 16 GiB DDR4-3600 CL26 Kingston (Dual Rank, unbuffered ECC)

- Grafikprozessor

- 1x ASRock Radeon RX 6950XT Formula OC 16GByte GDDR6 VRAM

- Display

- SAMSUNG Neo QLED QN92BA 43" up to 4K@144Hz FreeSync PP HDR10+

- SSD

- WD_Black SN850 PCI-Express 4.0 NVME

- HDD

- 3 Stück

- Optisches Laufwerk

- 1x HL-DT-ST BD-RE BH10LS30 SATA2

- Soundkarte

- HD Audio (onboard)

- Gehäuse

- SF-2000 Big Tower

- Netzteil

- Corsair RM1000X (80+ Gold)

- Tastatur

- Habe ich

- Maus

- Han I

- Betriebssystem

- Windows 10 x64 Professional (up to date!)

- Webbrowser

- @Chrome.Google & Edge Chrome

@Opteron

Bezüglich diesem Post : http://www.planet3dnow.de/vbulletin/showpost.php?p=4465288&postcount=3533

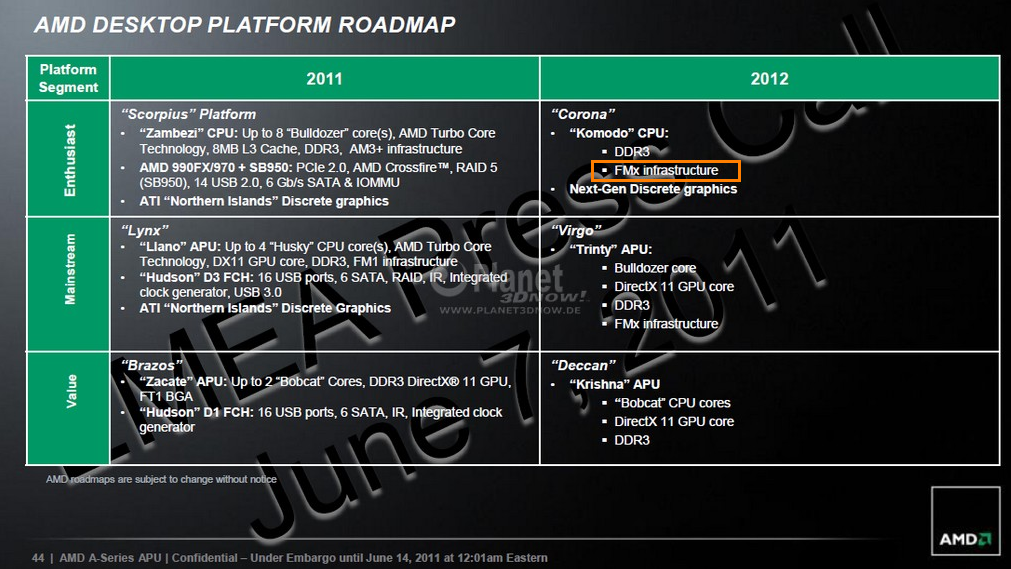

Das könnte auch eine APU sein! (siehe Anhang)

Quelle

Bezüglich diesem Post : http://www.planet3dnow.de/vbulletin/showpost.php?p=4465288&postcount=3533

Aja, zuvor hieß es noch, dass sie working 28nm silicon hätten, war - glaub ich GPU bezogen.

Das könnte auch eine APU sein! (siehe Anhang)

Quelle

Zuletzt bearbeitet:

nazgul99

Grand Admiral Special

- Mitglied seit

- 01.05.2005

- Beiträge

- 3.592

- Renomée

- 224

- Standort

- Irgendwo in der Nähe

- Mein Laptop

- ThinkPad Edge E145 / 8GB / M500 480GB / Kubuntu /// Asus U38N / 6GB / Matt / Postville / Kubuntu/W8

- Details zu meinem Desktop

- Prozessor

- AMD A10-7800

- Mainboard

- MSI A88XI AC

- Kühlung

- Scythe Shuriken Rev.2

- Speicher

- 2x 8GB DDR3-2133

- Grafikprozessor

- IGP

- Display

- HP LP2465, MVA, 1920x1200, 24"

- SSD

- Samsung 850 EVO 500GB

- HDD

- ST9500325AS 500GB

- Optisches Laufwerk

- ja, so'n USB-Dings

- Soundkarte

- onboard, optisch -> SMSL Q5 PRO -> ELAC EL60

- Gehäuse

- Silverstone ML06B

- Netzteil

- SST-ST30SF

- Betriebssystem

- Kubuntu

- Webbrowser

- Firefox

- Verschiedenes

- Synology DS414slim 3x 1,5 TB RAID5

Was soll die Nummer mit Speicher pro Kern? Jedem Kern steht der volle installierte Speicher zur Verfügung*, den durch die Kerne zu teilen, macht keinen Sinn. Speicher pro Workload mit soundso viel Speicherbedarf macht Sinn, alles Andere nicht. Wenn ich auf jedem Kern eine VM laufen lasse (oder eine andere Anwendung, die viel Speicher exklusiv beansprucht), interessiert Speicher pro Kern, aber eigentlich geht es da wieder um Speicher pro Anwendung.

Und statt "wir" möchte ich beim Festhängen an der 3GB-Grenze lieber doch ein "viele" setzen.

*in einem UMA-System, bei NUMA relativiert sich das graduell. Und auch ein K10.x- oder BD-System mit einem Sockel und einem Die ist ein UMA-System, NUMA kommt erst mit mehreren Dies ins Spiel.

Und statt "wir" möchte ich beim Festhängen an der 3GB-Grenze lieber doch ein "viele" setzen.

*in einem UMA-System, bei NUMA relativiert sich das graduell. Und auch ein K10.x- oder BD-System mit einem Sockel und einem Die ist ein UMA-System, NUMA kommt erst mit mehreren Dies ins Spiel.

Zuletzt bearbeitet:

Opteron

Redaktion

☆☆☆☆☆☆

Jo, aber die Krux ist, dass der Core an sich erstmal kein RAM brauchtZum RAM.

Wer heute sagt, 4GB reichen, der hat die 65kByte-Aussage von Bill Gates noch nicht verstanden.

Sepang wird 10 Cores haben. Wie viel GB pro Core hat man, wenn man 8GB installiert? Richtig 800MB.

Erstmal braucht man Software die irgendwas auf dem Kern berechnet. Im Desktopbereich sehe ich da keine großen Speicherfresser. Bisher war das ja immer Windows, aber Win8 soll jetzt sogar auf ARMs laufen, da bin ich mal gespannt. Schon Win7 hat sich ja vornehm zurückgehalten.

Gegenargument:

Wieviel Kerne/Threads gibts auf ner Grafikkarte und wievel VRAM haben die?

Da bin ich gerne mit dabei, da haben wir dann nur unterschiedliche Sichtweisen. Ich seh das aus Desktop/Game Sicht, Du aus Workstationperspektive.----------------------------------------------

Ganz kleiner Einwurf von mir.

Wir entwickeln mit VS2010 und mussten/durften feststellen, dass sich VS2010 sehr über Hauptspeicher freut. Alle Entwicklungsrechner sind heute mit 8GB ausgerüstet - es war nichtmal schwierig dies bei der Geschäftsführung durch zu bringen - kost ja nix. Der Produktivitätsvorteil ist enorm.

Ich bin gerade in einem Projekt tätig, wo ich 4 Instanzen von VS2010 offen habe und damit debugge.

----------------------------------------------

Dann schreitet das Thema Virtualisierung immer weiter. Ich sehe es so, wer ein wirklich sicheres System haben will, der kommt um Virtualisierung nicht mehr herum. Bank-Geschäfte in einer sicheren virtualisierten Umgebung, surfen in gefährlicheren Foren in einer ganz anderen Umgebung und beide berühren sich nicht.

Workstations hatten schon immer grob die doppelte RAMausstattung der Standard Rechner. von daher ok.

VMs .. da reichen für ne billige Banking VM ebenfalls 8GB auf ~3-4Jahres Sicht.

Das oder wg. der Festplatte. Ne SSD rein und es flutscht.Windows 7 wird doch nur deshalb als sehr langsam wahrgenommen, weil der Virenscanner alles für sich in beschlag nimmt. Windows XP lief damals bei mir auf einem K6-3 mit 500MHZ oder auf einem Celeron-ULV mit 600MHz.

Ok, ich glaube Dir, aber was sind dabei dann die Auswirkungen auf den RAM Bedarf?Zukünftig trennt man die Sachen soweit voneinander(Speichermässig), dass ein Bufferflow nicht mehr von einem Prozess auf den anderen zugreifen kann. Ein Bufferoverflow kann dann nicht mehr aus der eigenen OS-Instanz rausgreifen.

Wenn Du das auf die Workstations und/oder auf Desktopneukäufe und nicht auf den Marktdurchschnitt beziehst, bin ich da auch dabei.Zurück vom Ausflug. 8GB werden in den nächsten 1 1/2 Jahren Standard. 16GB wird premium, aber in 3-4Jahren auch Standard sein.

Ehh .. Komodo wird weder Laptop noch DTR CPU, sondern Enthusiasten Dickschiff(Desktop) Prozessor, steht doch so auf der Roadmap:Wo ich eigentlich hin will.

Wo soll Komodo eigentlich eingebaut werden?

Wird Komodo eine Laptop bzw. Desktop-Replacement-CPU?

(Ich habe nochmal eine Nacht drüber geschlafen, deshalb klingt es jetzt schon wieder anders).

Die Volumen werden im Laptop Markt gemacht, deshalb kann ich mir nicht mehr vorstellen, dass man einen eigenen Die für den Nischen-Markt "Mainboard-Bastler, die mehr als Llano brauchen" macht. Deshalb glaube ich auch nicht, dass Komodo wirklich 5 Module/10 Int-Cores haben wird(das passt nie und nimmer in ein Desktop-Replacement).

Desktop Plattform und Ethusiasten Segment. Das ist eindeutig. Im Mobilebereich kommt nur die Trinity APU, mit vermutlich 2Modulen, ohne L3 und mit nur 1MB L2, und ein paar mehr VLIW4 Shader. Recht viel mehr dürfte in 32nm flächenmäßig nicht drin sein.

Garantiert nicht, was will ein Ethusiast CPU ohne L3?Komodo wird eine 4 Module-CPU mit nicht besonders grossem Die sein, evtl. sogar ganz ohne L3-Cache, so wie wir es bei den heutigen Propus-Dies sehen. Komodo wird auch kein Triple-Channel bekommen.

Jo, und weil man im Enthuasiasten Bereich ohne L3 keinen Blumentopf gewinntDesktop-BD hat nur deshalb einen L3-Cache, weil Desktop & Server-Die gleich sind.

Nachdem AMD die (vor)letzte Roadmap bei Komodo auf 6-10 Kerne aktualisierte "riecht" eigentlich alles nach der üblichen Server Die = Enthusiasten Die Strategie. Es sei denn, sie feuern wieder nen Versuchsballon wie Thuban ab. Aber dafür gibts im Moment keine Anzeichen. Falls sie eDRAM oder TRAM ausprobieren sollten, können sie das gleich mit einem Server=Enthusiast Desktop Die machen.

Zu Boinc:

Naja, der RAM Verbrauch dort ist ebenfall eher workstation Niveau. Für einen "Normaluser" ist das kein Maßstab.

.

EDIT :

.

Jo, klar, deswegen nur das "glaub ich", hab da nur mit einem Ohr zugehört, aber die Frage zuvor war (glaub ich^^), irgendwas zu GPU Ramping oder so.@Opteron

Bezüglich diesem Post : http://www.planet3dnow.de/vbulletin/showpost.php?p=4465288&postcount=3533

Das könnte auch eine APU sein! (siehe Anhang)

Quelle

Nachdem das Transcript jetzt draußen, ist, kann mans ja jetzt eh nachprüfen.

Ist dann aber Bobcat bezogen, da böte sich er andere Sammelthread an, hier gehts nur über Bulldozer. Wobei - Spekulationen sind dort auch eher schlecht .. hmm, vielleicht ein neuer Thread..

.

EDIT :

.

Durchgesickerte Roadmap in China, Update hier:

http://www.planet3dnow.de/vbulletin/showthread.php?p=4323465#Juli_2011_(Inoffiziell__unbestätigt_)

Was mich wundert:

Piledriver ist sowohl der CPU Kern von Trinity als auch Komodo. Weiß jemand, ob sich der Codenamen auch auf den L2 bezieht, oder nicht? Ist wohl ne Grauzone ...

nazgul99

Grand Admiral Special

- Mitglied seit

- 01.05.2005

- Beiträge

- 3.592

- Renomée

- 224

- Standort

- Irgendwo in der Nähe

- Mein Laptop

- ThinkPad Edge E145 / 8GB / M500 480GB / Kubuntu /// Asus U38N / 6GB / Matt / Postville / Kubuntu/W8

- Details zu meinem Desktop

- Prozessor

- AMD A10-7800

- Mainboard

- MSI A88XI AC

- Kühlung

- Scythe Shuriken Rev.2

- Speicher

- 2x 8GB DDR3-2133

- Grafikprozessor

- IGP

- Display

- HP LP2465, MVA, 1920x1200, 24"

- SSD

- Samsung 850 EVO 500GB

- HDD

- ST9500325AS 500GB

- Optisches Laufwerk

- ja, so'n USB-Dings

- Soundkarte

- onboard, optisch -> SMSL Q5 PRO -> ELAC EL60

- Gehäuse

- Silverstone ML06B

- Netzteil

- SST-ST30SF

- Betriebssystem

- Kubuntu

- Webbrowser

- Firefox

- Verschiedenes

- Synology DS414slim 3x 1,5 TB RAID5

Durchgesickerte Roadmap in China, Update hier:

http://www.planet3dnow.de/vbulletin/showthread.php?p=4323465#Juli_2011_(Inoffiziell__unbestätigt_)

Was mich wundert:

Piledriver ist sowohl der CPU Kern von Trinity als auch Komodo. Weiß jemand, ob sich der Codenamen auch auf den L2 bezieht, oder nicht? Ist wohl ne Grauzone ...

Wow, was ich interessant finde: bei Komodo und Trinity steht als Sockel FM2, nicht mehr verbrämt FMx, was ja theoretisch immernoch zwei verschiedene Sockel hätten sein können.

deadohiosky

Gesperrt

- Mitglied seit

- 13.07.2011

- Beiträge

- 1.624

- Renomée

- 26

Um ehrlich zu sein finde ich viel interessanter, dass Deccan bzw. Wichita den FCH integriert hat.

.

EDIT :

.

Ich hoffe schwer, dass Fm1 aufwärtskompatibel zu FM2 ist... (dafür spricht auch die Beibehaltung der Chipsätze A55 und A75)

Außerdem: Turbo Core 3.0

RAID 5 Unterstützung

.

EDIT :

.

Ich hoffe schwer, dass Fm1 aufwärtskompatibel zu FM2 ist... (dafür spricht auch die Beibehaltung der Chipsätze A55 und A75)

Außerdem: Turbo Core 3.0

RAID 5 Unterstützung

Zuletzt bearbeitet:

erde-m

Grand Admiral Special

- Mitglied seit

- 23.03.2002

- Beiträge

- 3.272

- Renomée

- 452

- Standort

- TF

- Mitglied der Planet 3DNow! Kavallerie!

- Lieblingsprojekt

- LHC

- Meine Systeme

- AMD Ryzen9 5950X+64 GB DDR3600+RX6900XT, AMD Epyc 7V12+256 GB ECC DDR3200+R VII, AMD Ryzen 5 2500U

- BOINC-Statistiken

- Mein Laptop

- HP Envy x360 15-bq102ng Ryzen 5 2500U

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen9 5950X

- Mainboard

- Asus Prime X470-Pro

- Kühlung

- be quiet Silent Loop 280mm

- Speicher

- 64GB (4x16GB) G.Skill TridentZ Neo F4-3600C16-64GTZNC Quad Kit

- Grafikprozessor

- AMD Radeon RX 6900XT

- Display

- Acer Pro Designer PE320QK

- SSD

- M2: 2x Samsung 970Evo Plus 1TB

- HDD

- WDC WD100EFAX

- Soundkarte

- Onboard

- Gehäuse

- Fractal Define 7 Clear Tempered Glass White

- Netzteil

- bequiet Dark Power 12 1000W

- Tastatur

- Logitech G815

- Maus

- Logitech G402

- Betriebssystem

- Linux Mint 21.2; Win10Pro-64Bit

- Webbrowser

- Firefox

- Verschiedenes

- Qnap Single-port Aquantia AQC107 10GbE

- Internetanbindung

- ▼225 MBit ▲45 MBit

Ob der FM2 dann Triple-Channel ermöglicht? Für CPU mit 10 Cores ja nicht das schlechteste und für die APUs auch mehr Bandbreite für die GPU. Was bedeutet, das auch Trinity einen Triple-Channel-Controller bekommen müßte? Damit wäre es aber wohl nichts mit FM1-kompatibel zu den Llano-Boards.

Durchgesickerte Roadmap in China, Update hier:

...

und beim Chipsatz für 2012 "Hudson" steht auch nix mehr von PCIe - könnte ja dann als Bestätigung für in Bulldozer 2 integriertes PCIe angesehen werden...

.

EDIT :

.

link aus 3dcenter forum:

http://www.brightsideofnews.com/new...rmance-projections-for-bulldozer-opteron.aspx

rasmus

Admiral Special

- Mitglied seit

- 07.07.2008

- Beiträge

- 1.191

- Renomée

- 47

- Mein Laptop

- Notebook, was ist das?

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 5 3600

- Mainboard

- MSI B450M PRO-VDH MAX

- Kühlung

- Luft

- Speicher

- 32 GB Gskill Ripjaws

- Grafikprozessor

- Nvidia 3070 ti FE

- Display

- Asus PB278Q 27" 2560*1440

- SSD

- Ja

- HDD

- auch

- Optisches Laufwerk

- ja

- Soundkarte

- onboard

- Gehäuse

- irgendwas mit glas

- Netzteil

- thermaltake toughpower pf1 750W

- Maus

- Rat 9

- Betriebssystem

- Win 7 64bit, Win 10 64 bit

- Webbrowser

- Firefox

- Verschiedenes

- http://valid.canardpc.com/show_oc.php?id=628058

Gibt es inzwischen eigentlich schon Infos zu Hudson D4?

aus 3dcenter -forum:

Bulldozer Opteron Frequenzen und Kerneanzahlen:

Opteron 6220 8cores @ 3,0GHz

Opteron 6234 12cores @ 2,4GHz

Opteron 6272 16cores @ 2,1GHz

Opteron 6276 16cores @ 2,3GHz

http://configurator.gateway.com/configurator/skuSelection/skus/ar385f1

Bulldozer Opteron Frequenzen und Kerneanzahlen:

Opteron 6220 8cores @ 3,0GHz

Opteron 6234 12cores @ 2,4GHz

Opteron 6272 16cores @ 2,1GHz

Opteron 6276 16cores @ 2,3GHz

http://configurator.gateway.com/configurator/skuSelection/skus/ar385f1

Opteron

Redaktion

☆☆☆☆☆☆

aus 3dcenter -forum:

Bulldozer Opteron Frequenzen und Kerneanzahlen:

Opteron 6220 8cores @ 3,0GHz

Opteron 6234 12cores @ 2,4GHz

Opteron 6272 16cores @ 2,1GHz

Opteron 6276 16cores @ 2,3GHz

http://configurator.gateway.com/configurator/skuSelection/skus/ar385f1

Das ist BD1, der bald kommt, hier diskutieren wir aber schon über BD2

Trotzdem Danke für den Link, ne P3D News gabs aber auch schon:

http://www.planet3dnow.de/cgi-bin/newspub/viewnews.cgi?id=1311594374

ONH

Grand Admiral Special

Die wenigen Infos deuten darauf hin das D4 ein D3 mit +2SATA 6Gbit/s +RAID 5 sein wird.Gibt es inzwischen eigentlich schon Infos zu Hudson D4?

rasmus

Admiral Special

- Mitglied seit

- 07.07.2008

- Beiträge

- 1.191

- Renomée

- 47

- Mein Laptop

- Notebook, was ist das?

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 5 3600

- Mainboard

- MSI B450M PRO-VDH MAX

- Kühlung

- Luft

- Speicher

- 32 GB Gskill Ripjaws

- Grafikprozessor

- Nvidia 3070 ti FE

- Display

- Asus PB278Q 27" 2560*1440

- SSD

- Ja

- HDD

- auch

- Optisches Laufwerk

- ja

- Soundkarte

- onboard

- Gehäuse

- irgendwas mit glas

- Netzteil

- thermaltake toughpower pf1 750W

- Maus

- Rat 9

- Betriebssystem

- Win 7 64bit, Win 10 64 bit

- Webbrowser

- Firefox

- Verschiedenes

- http://valid.canardpc.com/show_oc.php?id=628058

Ziemlich lahm, dann könnte ja theoretisch der A75 auch Crossfire mit 2x16 oder nicht? Ich habe bisher nur 2x8 gesehen.

Eine APU mit wirklich umschaltbarer Grafik und echter Crossfireoption wäre nämlich mal was, wofür ich einen Bulldozer (und wohl auch Komodo) stehen ließe.

Eine APU mit wirklich umschaltbarer Grafik und echter Crossfireoption wäre nämlich mal was, wofür ich einen Bulldozer (und wohl auch Komodo) stehen ließe.

nazgul99

Grand Admiral Special

- Mitglied seit

- 01.05.2005

- Beiträge

- 3.592

- Renomée

- 224

- Standort

- Irgendwo in der Nähe

- Mein Laptop

- ThinkPad Edge E145 / 8GB / M500 480GB / Kubuntu /// Asus U38N / 6GB / Matt / Postville / Kubuntu/W8

- Details zu meinem Desktop

- Prozessor

- AMD A10-7800

- Mainboard

- MSI A88XI AC

- Kühlung

- Scythe Shuriken Rev.2

- Speicher

- 2x 8GB DDR3-2133

- Grafikprozessor

- IGP

- Display

- HP LP2465, MVA, 1920x1200, 24"

- SSD

- Samsung 850 EVO 500GB

- HDD

- ST9500325AS 500GB

- Optisches Laufwerk

- ja, so'n USB-Dings

- Soundkarte

- onboard, optisch -> SMSL Q5 PRO -> ELAC EL60

- Gehäuse

- Silverstone ML06B

- Netzteil

- SST-ST30SF

- Betriebssystem

- Kubuntu

- Webbrowser

- Firefox

- Verschiedenes

- Synology DS414slim 3x 1,5 TB RAID5

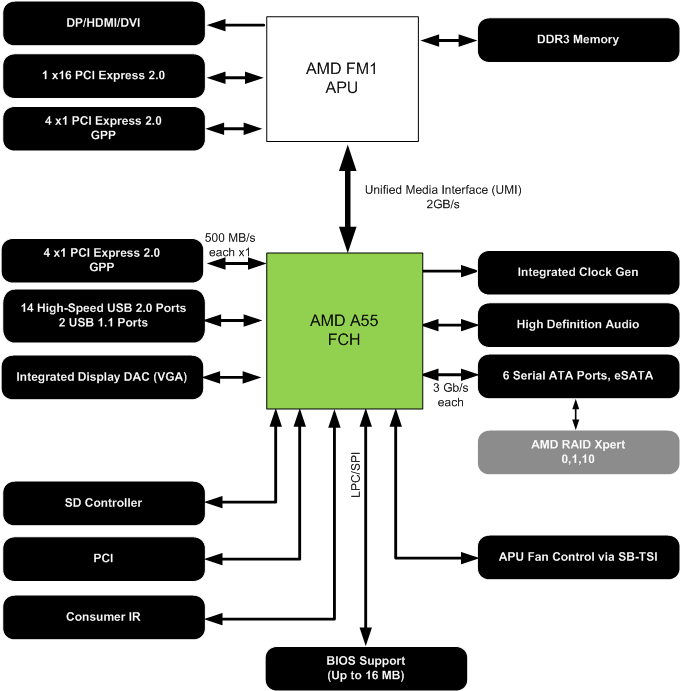

rasmus: Du bist hier offenbar noch im HyperTransport-Chipssatz-Schema unterwegs. Es ist wie einst bei der Integration der Speichercontroller: die Links für den PEG-Slot werden direkt von der APU versorgt. Die Southbridge/FCH führt nur vier PCIe-Lanes heraus, das macht Sinn, da sie auch nur mit deren vier an die CPU/APU angebunden ist. Plus weitere vier, die aber hauptsächlich für die Übertragung der Grafiksignale der iGPU vorgesehen sind.

rasmus

Admiral Special

- Mitglied seit

- 07.07.2008

- Beiträge

- 1.191

- Renomée

- 47

- Mein Laptop

- Notebook, was ist das?

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 5 3600

- Mainboard

- MSI B450M PRO-VDH MAX

- Kühlung

- Luft

- Speicher

- 32 GB Gskill Ripjaws

- Grafikprozessor

- Nvidia 3070 ti FE

- Display

- Asus PB278Q 27" 2560*1440

- SSD

- Ja

- HDD

- auch

- Optisches Laufwerk

- ja

- Soundkarte

- onboard

- Gehäuse

- irgendwas mit glas

- Netzteil

- thermaltake toughpower pf1 750W

- Maus

- Rat 9

- Betriebssystem

- Win 7 64bit, Win 10 64 bit

- Webbrowser

- Firefox

- Verschiedenes

- http://valid.canardpc.com/show_oc.php?id=628058

Hallo nazgul,

ich meine das hier :

Ich hätte aber gerne : Erweiterungsslots: 2x PCIe 2.0 x16, ...

Und natürlich echte switchable Grafik von APU auf discrete

ich meine das hier :

Erweiterungsslots: 1x PCIe 2.0 x16, 1x PCIe 2.0 x16 (elektrisch nur x4)

Ich hätte aber gerne : Erweiterungsslots: 2x PCIe 2.0 x16, ...

Und natürlich echte switchable Grafik von APU auf discrete

nazgul99

Grand Admiral Special

- Mitglied seit

- 01.05.2005

- Beiträge

- 3.592

- Renomée

- 224

- Standort

- Irgendwo in der Nähe

- Mein Laptop

- ThinkPad Edge E145 / 8GB / M500 480GB / Kubuntu /// Asus U38N / 6GB / Matt / Postville / Kubuntu/W8

- Details zu meinem Desktop

- Prozessor

- AMD A10-7800

- Mainboard

- MSI A88XI AC

- Kühlung

- Scythe Shuriken Rev.2

- Speicher

- 2x 8GB DDR3-2133

- Grafikprozessor

- IGP

- Display

- HP LP2465, MVA, 1920x1200, 24"

- SSD

- Samsung 850 EVO 500GB

- HDD

- ST9500325AS 500GB

- Optisches Laufwerk

- ja, so'n USB-Dings

- Soundkarte

- onboard, optisch -> SMSL Q5 PRO -> ELAC EL60

- Gehäuse

- Silverstone ML06B

- Netzteil

- SST-ST30SF

- Betriebssystem

- Kubuntu

- Webbrowser

- Firefox

- Verschiedenes

- Synology DS414slim 3x 1,5 TB RAID5

rasmus: Was auch immer du gern an mehr als 4 PCIe-Lanes hättest: Solange die APU oder später Komodo* auf FM2 dies nicht zur Verfügung stellt, wirst Du's nicht bekommen. Und mit dem FCH hat das nichts zu tun. Capiche?

*dort ist es allerdings wahrscheinlich, deshalb wird FM2 wohl auch mehr Pins haben müssen als FM1

NEIN!

*dort ist es allerdings wahrscheinlich, deshalb wird FM2 wohl auch mehr Pins haben müssen als FM1

dann könnte ja theoretisch der A75 auch Crossfire mit 2x16 oder nicht?

NEIN!

Onkel_Dithmeyer

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 22.04.2008

- Beiträge

- 12.943

- Renomée

- 4.014

- Standort

- Zlavti

- Aktuelle Projekte

- Universe@home

- Lieblingsprojekt

- Universe@home

- Meine Systeme

- cd0726792825f6f563c8fc4afd8a10b9

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- Ryzen 9 3900X @4000 MHz//1,15V

- Mainboard

- MSI X370 XPOWER GAMING TITANIUM

- Kühlung

- Custom Wasserkühlung vom So. G34

- Speicher

- 4x8 GB @ 3000 MHz

- Grafikprozessor

- Radeon R9 Nano

- Display

- HP ZR30W & HP LP3065

- SSD

- 2 TB ADATA

- Optisches Laufwerk

- LG

- Soundkarte

- Im Headset

- Gehäuse

- Xigmatek

- Netzteil

- BeQuiet Dark Pro 9

- Tastatur

- GSkill KM570

- Maus

- GSkill MX780

- Betriebssystem

- Ubuntu 20.04

- Webbrowser

- Firefox Version 94715469

- Internetanbindung

- ▼100 Mbit ▲5 Mbit

Es hat auch was mit der FCH zu tun. So stellt beim A74 mit Llano die APU 1x16 + 4x1 Lanes zur Verfügung und die FCH setzt noch mal 4x1 dazu. Theroretisch könnte man der FCH auch 1x16 Lanes zur verfügung stellen, wenn man sie entsprechend umbaut. Macht aber wenig Sinn, wenn man betrachtet, dass das Interkonnect zwischen APU und FCH nur 2GB/s schafft. Den Wert erreicht man mit genau vier PCIe-2.0-Lanes. Insofern müsste man auch noch die Verbindung aufpumpen. Sinn macht das Ganze dann aber reichlich wenig. Für Crossfire ist dies Plattform schlicht nicht geeignet und auch nie konzipiert worden.

rasmus

Admiral Special

- Mitglied seit

- 07.07.2008

- Beiträge

- 1.191

- Renomée

- 47

- Mein Laptop

- Notebook, was ist das?

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 5 3600

- Mainboard

- MSI B450M PRO-VDH MAX

- Kühlung

- Luft

- Speicher

- 32 GB Gskill Ripjaws

- Grafikprozessor

- Nvidia 3070 ti FE

- Display

- Asus PB278Q 27" 2560*1440

- SSD

- Ja

- HDD

- auch

- Optisches Laufwerk

- ja

- Soundkarte

- onboard

- Gehäuse

- irgendwas mit glas

- Netzteil

- thermaltake toughpower pf1 750W

- Maus

- Rat 9

- Betriebssystem

- Win 7 64bit, Win 10 64 bit

- Webbrowser

- Firefox

- Verschiedenes

- http://valid.canardpc.com/show_oc.php?id=628058

Ja, jetzt ist der Groschen gefallen

Schade eigentlich, aber kann man nichts machen. Und danke für die Aufklärung @Naz&O.

Planet3dnow! Da werden Sie geholfen.

Schade eigentlich, aber kann man nichts machen. Und danke für die Aufklärung @Naz&O.

Planet3dnow! Da werden Sie geholfen.

Opteron

Redaktion

☆☆☆☆☆☆

Nö, FM2 rüstet ganz sicher PCIe 3.0 nach, da reichen die Lanes so wie jetzt. Wird dann ja alles doppelt so schnell.rasmus: Was auch immer du gern an mehr als 4 PCIe-Lanes hättest: Solange die APU oder später Komodo* auf FM2 dies nicht zur Verfügung stellt, wirst Du's nicht bekommen. Und mit dem FCH hat das nichts zu tun. Capiche?

*dort ist es allerdings wahrscheinlich, deshalb wird FM2 wohl auch mehr Pins haben müssen als FM1

Onkel_Dithmeyer

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 22.04.2008

- Beiträge

- 12.943

- Renomée

- 4.014

- Standort

- Zlavti

- Aktuelle Projekte

- Universe@home

- Lieblingsprojekt

- Universe@home

- Meine Systeme

- cd0726792825f6f563c8fc4afd8a10b9

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- Ryzen 9 3900X @4000 MHz//1,15V

- Mainboard

- MSI X370 XPOWER GAMING TITANIUM

- Kühlung

- Custom Wasserkühlung vom So. G34

- Speicher

- 4x8 GB @ 3000 MHz

- Grafikprozessor

- Radeon R9 Nano

- Display

- HP ZR30W & HP LP3065

- SSD

- 2 TB ADATA

- Optisches Laufwerk

- LG

- Soundkarte

- Im Headset

- Gehäuse

- Xigmatek

- Netzteil

- BeQuiet Dark Pro 9

- Tastatur

- GSkill KM570

- Maus

- GSkill MX780

- Betriebssystem

- Ubuntu 20.04

- Webbrowser

- Firefox Version 94715469

- Internetanbindung

- ▼100 Mbit ▲5 Mbit

Nö, FM2 rüstet ganz sicher PCIe 3.0 nach, da reichen die Lanes so wie jetzt. Wird dann ja alles doppelt so schnell.

Hmmm? Wo ist das her? Finde da keine Infos zu

nazgul99

Grand Admiral Special

- Mitglied seit

- 01.05.2005

- Beiträge

- 3.592

- Renomée

- 224

- Standort

- Irgendwo in der Nähe

- Mein Laptop

- ThinkPad Edge E145 / 8GB / M500 480GB / Kubuntu /// Asus U38N / 6GB / Matt / Postville / Kubuntu/W8

- Details zu meinem Desktop

- Prozessor

- AMD A10-7800

- Mainboard

- MSI A88XI AC

- Kühlung

- Scythe Shuriken Rev.2

- Speicher

- 2x 8GB DDR3-2133

- Grafikprozessor

- IGP

- Display

- HP LP2465, MVA, 1920x1200, 24"

- SSD

- Samsung 850 EVO 500GB

- HDD

- ST9500325AS 500GB

- Optisches Laufwerk

- ja, so'n USB-Dings

- Soundkarte

- onboard, optisch -> SMSL Q5 PRO -> ELAC EL60

- Gehäuse

- Silverstone ML06B

- Netzteil

- SST-ST30SF

- Betriebssystem

- Kubuntu

- Webbrowser

- Firefox

- Verschiedenes

- Synology DS414slim 3x 1,5 TB RAID5

Praktisch ist dies aber nicht der Fall und wird es auch nicht, da es sinnlos ist, die Lanes erst durch den FCH zu führen, nur um sie dann exclusiv für die Graka(s) zu verwenden. Bei anderen Verbindungen wie Disk-I/O, USB3 etc. ist es nicht dramatisch, wenn es eine Überprovisionierung der Bandbreite der ausgehenden Datenleitungen ggü. den eingehenden (von CPU/APU) gibt, bei einem PEG-Slot (oder 2) wäre das aber nicht förderlich. Und es kämen sinnlos doppelte Leitungen und Latenz dazu. Also: Nein, PEG-Slots und FCH haben nichts miteinander zu tun, und wenn es so wäre, wäre es ein Trauerspiel.Es hat auch was mit der FCH zu tun. So stellt beim A74 mit Llano die APU 1x16 + 4x1 Lanes zur Verfügung und die FCH setzt noch mal 4x1 dazu. Theroretisch könnte man der FCH auch 1x16 Lanes zur verfügung stellen, wenn man sie entsprechend umbaut.

Was soll eigentlich "So stellt beim A74 mit Llano die APU 1x16 + 4x1 Lanes zur Verfügung" aussagen? Die APU 16+4 Lanes zur Verfgung, der FCH ist mit nochmal 4 angbunden. "Beim A74" (der im Übrigen A75 heißt) macht keinen Sinn, da er mit den 16+4 Lanes nichts zu tun hat. Die laufen an ihm vorbei. "Bei Llano" oder "bei FM1" würde Sinn machen.

Aber sind wir hier nicht im BD2-Thread? Na gut, da geht's ja mit FM2 auch um FCH-Bauweise.

.

EDIT :

.

Möglich (sofern FM2 tatsächlich PCIe 3.0 bietet), aber beim Generationswechsel PCI 1.1 -> 2.0 wurden auch weiterhin 16 Lanes pro PEG-Slot geschaltet, sonst hätten die "Enthusiasten" sofort wieder rumgeschrien.Nö, FM2 rüstet ganz sicher PCIe 3.0 nach, da reichen die Lanes so wie jetzt. Wird dann ja alles doppelt so schnell.

Onkel_Dithmeyer

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 22.04.2008

- Beiträge

- 12.943

- Renomée

- 4.014

- Standort

- Zlavti

- Aktuelle Projekte

- Universe@home

- Lieblingsprojekt

- Universe@home

- Meine Systeme

- cd0726792825f6f563c8fc4afd8a10b9

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- Ryzen 9 3900X @4000 MHz//1,15V

- Mainboard

- MSI X370 XPOWER GAMING TITANIUM

- Kühlung

- Custom Wasserkühlung vom So. G34

- Speicher

- 4x8 GB @ 3000 MHz

- Grafikprozessor

- Radeon R9 Nano

- Display

- HP ZR30W & HP LP3065

- SSD

- 2 TB ADATA

- Optisches Laufwerk

- LG

- Soundkarte

- Im Headset

- Gehäuse

- Xigmatek

- Netzteil

- BeQuiet Dark Pro 9

- Tastatur

- GSkill KM570

- Maus

- GSkill MX780

- Betriebssystem

- Ubuntu 20.04

- Webbrowser

- Firefox Version 94715469

- Internetanbindung

- ▼100 Mbit ▲5 Mbit

Praktisch ist dies aber nicht der Fall und wird es auch nicht, da es sinnlos ist, die Lanes erst durch den FCH zu führen, nur um sie dann exclusiv für die Graka(s) zu verwenden. Bei anderen Verbindungen wie Disk-I/O, USB3 etc. ist es nicht dramatisch, wenn es eine Überprovisionierung der Bandbreite der ausgehenden Datenleitungen ggü. den eingehenden (von CPU/APU) gibt, bei einem PEG-Slot (oder 2) wäre das aber nicht förderlich. Und es kämen sinnlos doppelte Leitungen und Latenz dazu. Also: Nein, PEG-Slots und FCH haben nichts miteinander zu tun, und wenn es so wäre, wäre es ein Trauerspiel.

Ich habe nur aufgezählt, was möglich ist. Man kann tatsächlich 4 PCIe-Lanes der FHC verwenden und nat. wäre es mit einigen modifikationen AMDs möglich gewesen auch 16 Lanes über die FHC bereitzustellen. Dass man das nicht macht, weil es unsinn wäre, habe ich bereits geschrieben.

Was soll eigentlich "So stellt beim A74 mit Llano die APU 1x16 + 4x1 Lanes zur Verfügung" aussagen? Die APU 16+4 Lanes zur Verfgung, der FCH ist mit nochmal 4 angbunden. "Beim A74" (der im Übrigen A75 heißt) macht keinen Sinn, da er mit den 16+4 Lanes nichts zu tun hat. Die laufen an ihm vorbei. "Bei Llano" oder "bei FM1" würde Sinn machen.

A75 nat. hab mich vertippt, entschuldige

Ich meinte, dass bei der Kombination von Llano mit dem A75 folgendes Einheiten die Lanes zur Verfügung stellen:

die APU 16+4

die FHC 4

Ich hoffe, das war verständlicher.

Ergänzend schreibe ich gerne noch dazu, dass die Lanes der FHC für Netzwerk, USB und sonstige Periferie-Controller gedacht sind, was man auch gut an der UMI getauften Verbindung zwischen APU und FHC, die mit 2GB/s für solche Aufgaben zu schwach ist. Im Vergleich dazu hat HT mit 51,2 GB/s deutlich mehr Potential für solche Aufgaben, wo man wieder die Einordnung in den Mainstream erkennt. Die Plattform ist eben nicht für Corssfire gedacht.

Ich hoffe das war jetzt ausführlich genug

nazgul99

Grand Admiral Special

- Mitglied seit

- 01.05.2005

- Beiträge

- 3.592

- Renomée

- 224

- Standort

- Irgendwo in der Nähe

- Mein Laptop

- ThinkPad Edge E145 / 8GB / M500 480GB / Kubuntu /// Asus U38N / 6GB / Matt / Postville / Kubuntu/W8

- Details zu meinem Desktop

- Prozessor

- AMD A10-7800

- Mainboard

- MSI A88XI AC

- Kühlung

- Scythe Shuriken Rev.2

- Speicher

- 2x 8GB DDR3-2133

- Grafikprozessor

- IGP

- Display

- HP LP2465, MVA, 1920x1200, 24"

- SSD

- Samsung 850 EVO 500GB

- HDD

- ST9500325AS 500GB

- Optisches Laufwerk

- ja, so'n USB-Dings

- Soundkarte

- onboard, optisch -> SMSL Q5 PRO -> ELAC EL60

- Gehäuse

- Silverstone ML06B

- Netzteil

- SST-ST30SF

- Betriebssystem

- Kubuntu

- Webbrowser

- Firefox

- Verschiedenes

- Synology DS414slim 3x 1,5 TB RAID5

So isses 1A!

Ich mag halt so unvollständige Aussagen nicht, da bezieht sich nachher jemand drauf und dann muss man doppelt nachhaken.

Ich mag halt so unvollständige Aussagen nicht, da bezieht sich nachher jemand drauf und dann muss man doppelt nachhaken.

Opteron

Redaktion

☆☆☆☆☆☆

Gibts auch nicht, aber AMD rüstet bei allen anderen CPUs in 2012 "PCIe Gen3" nach (Quelle siehe Signatur). Wenn ausgerechnet Trinity das nicht bekommen sollte, müßte ich mich schon sehr wundern.Hmmm? Wo ist das her? Finde da keine Infos zu

Wenns nicht so käme bräuchte man auch garantiert keinen Sockel FM2.

Allerhöchstens könnte man noch spekulieren, dass nur Komodo PCIe 3 bekommt, und Trinity aus stromspargründen bei 2.0 bleibt. Aber vermutlich reicht es auch, wenn man diese Grenze zw. mobile/desktop Trinitys zieht.

Nachdem es - so wie es ausschaut - keine Triple channel Enthusiasten Plattform gibt, sind die die-hard Enthusiasten AMD wohl ziemlich wurst. Sockel FM2 für Komodo verstärkt den Eindruck ja auch noch. Das ganze ist dann eher oberes Performance Segment, und dafür reicht dann 2x Pcie3 x8 oder 1xPCIe3 x16.Möglich (sofern FM2 tatsächlich PCIe 3.0 bietet), aber beim Generationswechsel PCI 1.1 -> 2.0 wurden auch weiterhin 16 Lanes pro PEG-Slot geschaltet, sonst hätten die "Enthusiasten" sofort wieder rumgeschrien.

Eventuell ne ähnlich Strategie wie bei den Grafikkarten, das super-high-end Segment läßt AMD aus. Nur hat man dieses Mal halt keine X2 Ersatzlösung im Petto ^^

Nach Dirks Rücktritt ist wohl eher großes Marktvolumen AMDs Schwerpunkt. Produkte für Randgruppen interessieren nicht mehr.

Zuletzt bearbeitet:

y33H@

Admiral Special

- Mitglied seit

- 16.05.2011

- Beiträge

- 1.768

- Renomée

- 10

Piledriver-basierte APUs für Mobile mit 35 bis 60 Watt. Klingt für mich bei zwei Modulen sparsamer als vier Husky-Kerne (und evtl sogar schneller).

Anhang anzeigen 23488

Anhang anzeigen 23488

Opteron

Redaktion

☆☆☆☆☆☆

Laut der Präsentation startet GF Ende des Jahres 20nm:

http://www.slideshare.net/marketingeda/globalfoundries-dac-2011-update

Zumindest startet da das erste "MWP". Weiß einer was das im Zusammenhang mit "Shuttel" bedeutet ?

Edit:

Ah bei GF stehts:

Also verschiedene Chips auf einem DIE? Klingt lustig ^^

So gesehen spekuliere ich dann mal auf einen Druckfehler, und anstatt 28nm, sollte das 20nm heißen. Wenn die jetzt in Q4 mit den ersten Prototypen anfangen, sollte der Dublin dann doch locker bis 2013 fertig werden. Aber naja - abwarten. In 20nm könnten sie dann eigentlich auch ein paar mehr Kerne aufs DIE bringen

Vermutlich werden die 28nm doch stimmen.

http://www.slideshare.net/marketingeda/globalfoundries-dac-2011-update

Zumindest startet da das erste "MWP". Weiß einer was das im Zusammenhang mit "Shuttel" bedeutet ?

Edit:

Ah bei GF stehts:

http://www.globalfoundries.com/services/global_shuttle.aspxMPW (Multi Project Wafer)

Also verschiedene Chips auf einem DIE? Klingt lustig ^^

So gesehen spekuliere ich dann mal auf einen Druckfehler, und anstatt 28nm, sollte das 20nm heißen. Wenn die jetzt in Q4 mit den ersten Prototypen anfangen, sollte der Dublin dann doch locker bis 2013 fertig werden. Aber naja - abwarten. In 20nm könnten sie dann eigentlich auch ein paar mehr Kerne aufs DIE bringen

Vermutlich werden die 28nm doch stimmen.

Zuletzt bearbeitet:

Ähnliche Themen

- Antworten

- 368

- Aufrufe

- 39K

- Antworten

- 28

- Aufrufe

- 20K

- Antworten

- 0

- Aufrufe

- 2K

G

- Antworten

- 0

- Aufrufe

- 2K

G

- Antworten

- 8

- Aufrufe

- 4K