App installieren

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: This feature may not be available in some browsers.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Was kommt (nach den ersten Deneb (K10.5+)) fuer den Desktop bis zum Launch der BD(APUs)?

- Ersteller TNT

- Erstellt am

nonworkingrich

Captain Special

- Mitglied seit

- 28.04.2006

- Beiträge

- 234

- Renomée

- 4

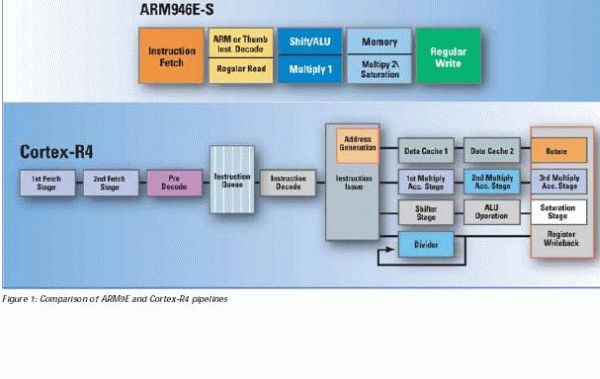

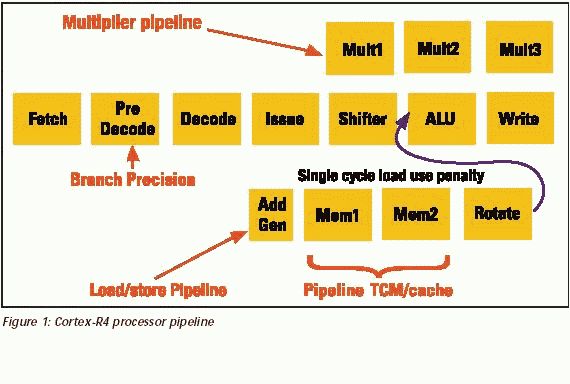

Beides keine schlechten Designs, der Cortex IMHO sogar ein exzellentes ... deren Problem ist eher, dass sie auf einen Markt zielen den big i für sich - und das heißt bei big i immer: ausschließlich für sich und das für alle Zeiten - beansprucht. Sollte mich sehrst wundern, wenn Intel bei abgekündigten ARM Netbooks und Notebooks nicht seine schnmutzigen Fiinger im Spiel hätte. K7 anyone?!Der Cortex-A9 ist ähnlich "weit verbreitet" wie der Via Nano

Bobo_Oberon

Grand Admiral Special

- Mitglied seit

- 18.01.2007

- Beiträge

- 5.045

- Renomée

- 190

Wobei man sagen kann, dass die Cortex-Kerne (auch die sehr Leistungsstarken der Serie 9) jetzt im Jahr 2009 integriert werden in die verschiedenen Mobilchips von Texas Instruments, Infineon, Qualcomm, Nvidia und weiteren ARM-Lizenznehmern Firmen. Misserfolg sieht anders ausBeides keine schlechten Designs, der Cortex IMHO sogar ein exzellentes ... deren Problem ist eher, dass sie auf einen Markt zielen den big i für sich - und das heißt bei big i immer: ausschließlich für sich und das für alle Zeiten - beansprucht. Sollte mich sehrst wundern, wenn Intel bei abgekündigten ARM Netbooks und Notebooks nicht seine schnmutzigen Fiinger im Spiel hätte. ...

Langfristig ersetzen die Cortex-Kerne alle bisherigen ARM-Kerne. Pi mal Daumen ging ARM damals davon aus, dass die Artisan-Chips in etwa 20 bis 30 Prozent leistungsfähiger sind, bei gleichen Transistorbedarf und sogar sparsam bleiben.

Das leistungsfähige Cortex-Design von Artisan führte zum Aufkauf seitens ARM Ende 2004.

Oder anders gesagt. Da wo ARM fett drin ist, da muss Intel erst mal (wieder) rein. In den Mobilfunktmarkt. Ob da der Atom wirklich in 32 nm schon gut genug dafür ist?

MFG Bobo(2009)

Opteron

Redaktion

☆☆☆☆☆☆

Maaaann ... ich zerleg nicht mich dabei, sondern Deine eigene Argumentation ... InO ist nicht notwendigerweise energiesparend, mach Dir doch wenigstensmal die Mühe und such, da Du aber anscheinend die Suche eher scheust: Das Ding hat 160W+ TDP.Du widerlegst dich selbst innerhalb von 10 Zeilen Text - das spart mir Arbeit. Der bisher in Serie verkaufte, höchstgetakte Prozessor ist -> richtig -> der Power6 mit 4,7GHz -> ist In-Order

Rechenleistung so lala, der Hit wars nicht, deswegen stampfen sie InO auch wieder ein.

Ja das Ding ist nagelneu .. genauso nagelneu wie der Bobcat 2011 sein wird, sollte als Beispiel dienen, dass die InO Zeiten vorbei sind, wenn sogar ARM jetzt damit anfängt.Der Cortex-A9 ist ähnlich "weit verbreitet" wie der Via Nano

Zumindest im anvisierten 1-10W Bereich.

Lass uns dieses Thema bitte nicht mehr weitervertiefen.

Jo lassen wirs, falls noch was ist bitte per PM, sonst langweilen wir eh nur die Mitleser

@Crashtest:

Jo, aber wieso K8 = 0Fh war/ist, weiss keiner ...0Fh ist eigentlich 15, nach der Analogie wäre K8 also K15, passt nicht so gut. Ergo ist die K10 = 10fh Analogie ebenso falsch wie 11h = K11, d.h. der K11 Name ist wider Erwarten doch nicht besetzt.

Der Bulldozer kann gerne family 12h sein, aber deswegen trotzdem K11 heißen, denn dass der Turion Ultra K11 wäre, steht nirgends, da steht nur family 11h, und das bedeutet nichts.

ciao

Alex

gruffi

Grand Admiral Special

- Mitglied seit

- 08.03.2008

- Beiträge

- 5.393

- Renomée

- 65

- Standort

- vorhanden

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 5 1600

- Mainboard

- MSI B350M PRO-VDH

- Kühlung

- Wraith Spire

- Speicher

- 2x 8 GB DDR4-2400 CL16

- Grafikprozessor

- XFX Radeon R7 260X

- Display

- LG W2361

- SSD

- Crucial CT250BX100SSD1

- HDD

- Toshiba DT01ACA200

- Optisches Laufwerk

- LG Blu-Ray-Brenner BH16NS40

- Soundkarte

- Realtek HD Audio

- Gehäuse

- Sharkoon MA-I1000

- Netzteil

- be quiet! Pure Power 9 350W

- Betriebssystem

- Windows 10 Professional 64-bit

- Webbrowser

- Mozilla Firefox

- Verschiedenes

- https://valid.x86.fr/mb4f0j

Mal ein Gedankenspiel am Rande, wie wahrscheinlich ist es, dass Bobcat auf Bulldozer basiert? Also 1 Kern mit 2 INT Einheiten für 2 Threads. Das sollte doch ausreichend Bums sein, um zumindest Atom in seine Schranken zu verweisen und in 32 nm bei moderaten Taktraten die angepeilten 1-10 W nicht zu überschreiten. Uncore und Stromsparmechanismen werden dann sicherlich auf ein so minimalistisches Design angepasst. Oder wäre ein altgedientes Design, wie zB der K8, eine plausiblere Basis?

Opteron

Redaktion

☆☆☆☆☆☆

Seh ich ähnlich, halt ein halber Bulldozer, siehe letzte Seite:Mal ein Gedankenspiel am Rande, wie wahrscheinlich ist es, dass Bobcat auf Bulldozer basiert? Also 1 Kern mit 2 INT Einheiten für 2 Threads. Das sollte doch ausreichend Bums sein, um zumindest Atom in seine Schranken zu verweisen und in 32 nm bei moderaten Taktraten die angepeilten 1-10 W nicht zu überschreiten.

http://www.planet3dnow.de/vbulletin/showthread.php?p=4024787#post4024787

Das reicht, auf alle Fälle. K8 sollte zwar in 32nm auch sehr kompakt sein, aber 2 Threads sollten es aktuell schon sein, auch für nen 1-10W Prozessor. Dazu kommt bei so nem Teil noch der Lerneffekt für den großen Bulldozer, man darf ja nie vergessen das AMD nicht soviele Entwickler hat, da ist so ein Testprozessor sicherlich nicht verkehrt.

Wenn ich AMD wäre, würde ich es so machen, aber mal schauen, was am Ende rauskommt

Jein ... eventuell gibts den schon noch, nur benützt AMDs Marketingabteilung den nicht:Ganz davon abgesehen das es sowieso keine "Kx" Codenamen mehr bei AMD verwendet werden, also ist diese ganze Diskussion müßig.

http://www.amdzone.com/phpbb3/viewtopic.php?f=52&t=136584&p=163537#p163537There is an internal code name for the core that we would never use publicly.

Ob der internal code name jetzt K11 is, oder was anderes .. .kA.

12h ist auch unsicher, vielleicht kommt Fusion eher ^^

ciao

Alex

Zuletzt bearbeitet:

rkinet

Grand Admiral Special

Das wäre eine logische Antwort von AMD und würde tatsächlich low power ermöglichen.Mal ein Gedankenspiel am Rande, wie wahrscheinlich ist es, dass Bobcat auf Bulldozer basiert?

Also 1 Kern mit 2 INT Einheiten für 2 Threads. Das sollte doch ausreichend Bums sein, um zumindest Atom in seine Schranken zu verweisen und in 32 nm bei moderaten Taktraten die angepeilten 1-10 W nicht zu überschreiten.

Eher unwahrscheinlich dass AMD seine Ingenieure zur Resteverwertung per K8 anleitet.

Ge0rgy

Grand Admiral Special

- Mitglied seit

- 14.07.2006

- Beiträge

- 4.322

- Renomée

- 82

- Mein Laptop

- Lenovo Thinkpad X60s

- Details zu meinem Desktop

- Prozessor

- Phenom II 955 BE

- Mainboard

- DFI LanParty DK 790FXB-M3H5

- Kühlung

- Noctua NH-U12P

- Speicher

- 4GB OCZ Platinum DDR1600 7-7-7 @ 1333 6-6-6

- Grafikprozessor

- Radeon 4850 1GB

- HDD

- Western Digital Caviar Black 1TB

- Netzteil

- Enermax Modu 525W

- Betriebssystem

- Linux, Vista x64

- Webbrowser

- Firefox 3.5

in anlehnung an Evergreen bei den GPUs könnte man sich da so einiges lustiges vorstellen.

Überhaupt ist das ei kalauer, die Grafikchips sind nach Pflänzchen benannt und die CPUs nach etwas dass das Grünzeugs plattmacht

Überhaupt ist das ei kalauer, die Grafikchips sind nach Pflänzchen benannt und die CPUs nach etwas dass das Grünzeugs plattmacht

Markus Everson

Grand Admiral Special

ARM ist In-Order, weil energieeffizienter

ATOM ist In-Order weil energieeffizienter

Gegenthese: Atom ist I-O weil billiger.

.

EDIT :

.

Mal ein Gedankenspiel am Rande, wie wahrscheinlich ist es, dass Bobcat auf Bulldozer basiert? [...] um zumindest Atom in seine Schranken zu verweisen

Geringe Wahrscheinlichkeit, denke ich. Atom ist leistungsschwach in der Gegenwart und zu leistungsschwach in der nächsten Zukunft. Bobcat muß daher deutlich mehr Leistung liefern als der heutige Atom, eher in Richtung der heutigen ULV Cores.

Dr@

Grand Admiral Special

- Mitglied seit

- 19.05.2009

- Beiträge

- 12.791

- Renomée

- 4.066

- Standort

- Baden-Württemberg

- Aktuelle Projekte

- Collatz Conjecture

- Meine Systeme

- Zacate E-350 APU

- BOINC-Statistiken

- Mein Laptop

- FSC Lifebook S2110, HP Pavilion dm3-1010eg

- Details zu meinem Laptop

- Prozessor

- Turion 64 MT37, Neo X2 L335, E-350

- Mainboard

- E35M1-I DELUXE

- Speicher

- 2x1 GiB DDR-333, 2x2 GiB DDR2-800, 2x2 GiB DDR3-1333

- Grafikprozessor

- RADEON XPRESS 200m, HD 3200, HD 4330, HD 6310

- Display

- 13,3", 13,3" , Dell UltraSharp U2311H

- HDD

- 100 GB, 320 GB, 120 GB +500 GB

- Optisches Laufwerk

- DVD-Brenner

- Betriebssystem

- WinXP SP3, Vista SP2, Win7 SP1 64-bit

- Webbrowser

- Firefox 13

...

Jein ... eventuell gibts den schon noch, nur benützt AMDs Marketingabteilung den nicht:

http://www.amdzone.com/phpbb3/viewtopic.php?f=52&t=136584&p=163537#p163537

Ob der internal code name jetzt K11 is, oder was anderes .. .kA.

12h ist auch unsicher, vielleicht kommt Fusion eher ^^

Die letzte Mikroarchitektur hatte auch keine Kx Bezeichnung und es wurde auch mehrfach gesagt, dass auch intern keine Kx Bezeichnungen mehr verwendet werden. Eine K10 Mikroarchitektur hat es nie gegeben.

MfG @

Dresdenboy

Redaktion

☆☆☆☆☆☆

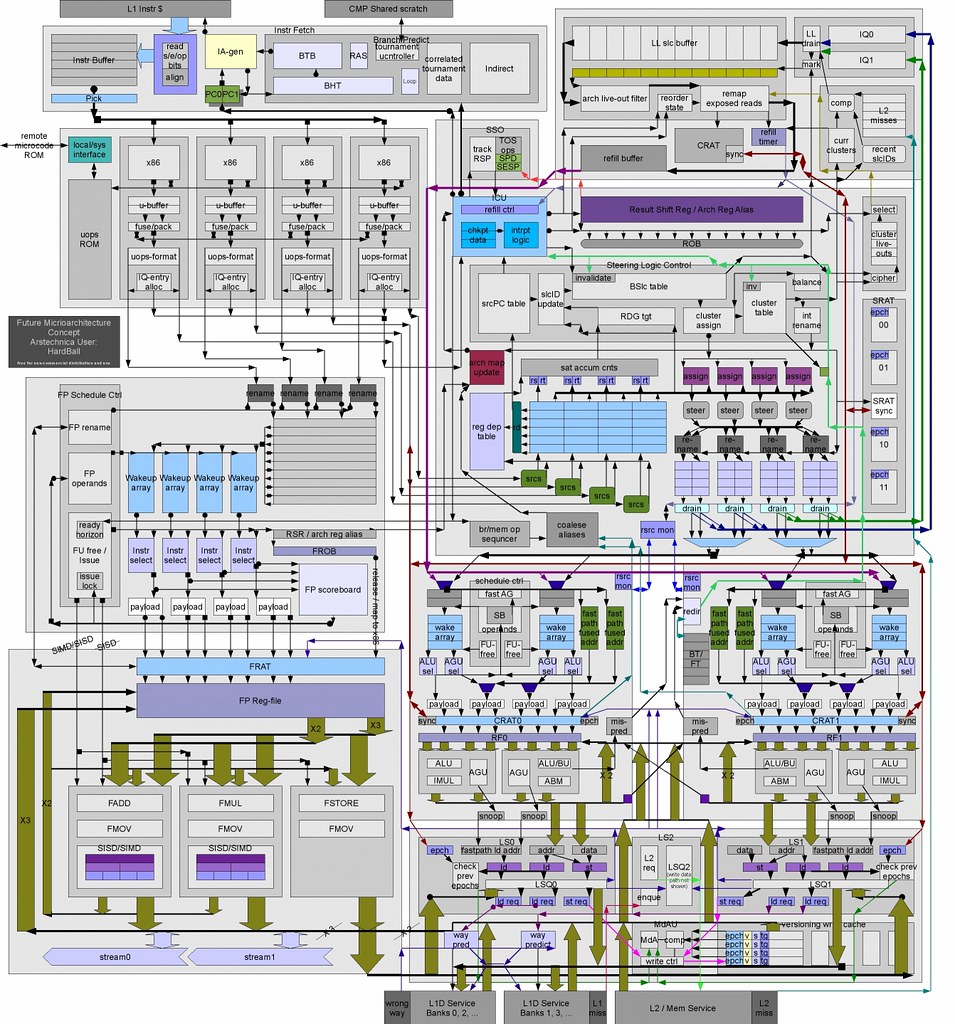

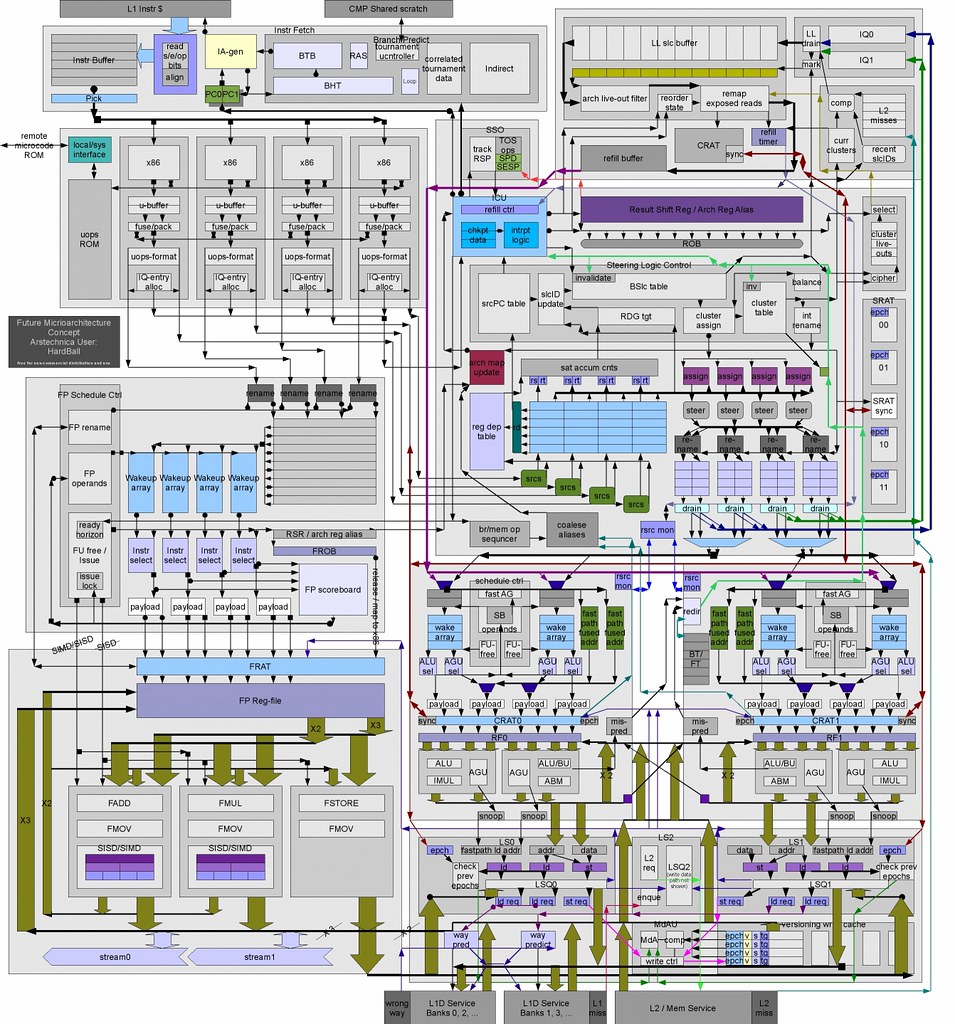

Etwas Diskussionsstoff:

http://forums.anandtech.com/messageview.aspx?catid=28&threadid=2332684&enterthread=y

Ein Bild daraus:

Das ist auf jeden Fall x86 und soll von einer kommenden Architektur abgeleitet sein... Erstmal ist spannend, wie realistisch das Design ist.

http://forums.anandtech.com/messageview.aspx?catid=28&threadid=2332684&enterthread=y

Ein Bild daraus:

Das ist auf jeden Fall x86 und soll von einer kommenden Architektur abgeleitet sein... Erstmal ist spannend, wie realistisch das Design ist.

Opteron

Redaktion

☆☆☆☆☆☆

Hmmm sieht aus wie der Health Care Plan der USA ^^ ...

Hier is es ein bisschen größer:

http://img3.abload.de/img/x86_next_genthc6.jpg

(ohne grottigen Flash Krams).

Muss doch wohl oder übel Bulldozer sein, CMP Scratch und der Loop Detektor in der BranchPrediciton hat Intel wohl weniger, auch wenn man nicht weiss, was SandyBridge bringen wird.

Edit

Naja, wenn mans dann mal genau anschaut, kommt eigentlich DDboys Schema raus...

ciao

Alex

Hier is es ein bisschen größer:

http://img3.abload.de/img/x86_next_genthc6.jpg

(ohne grottigen Flash Krams).

Muss doch wohl oder übel Bulldozer sein, CMP Scratch und der Loop Detektor in der BranchPrediciton hat Intel wohl weniger, auch wenn man nicht weiss, was SandyBridge bringen wird.

Edit

Naja, wenn mans dann mal genau anschaut, kommt eigentlich DDboys Schema raus...

ciao

Alex

Zuletzt bearbeitet:

Dresdenboy

Redaktion

☆☆☆☆☆☆

Danke für die große VersionHmmm sieht aus wie der Health Care Plan der USA ^^ ...

Hier is es ein bisschen größer:

http://img3.abload.de/img/x86_next_genthc6.jpg

(ohne grottigen Flash Krams).

Muss doch wohl oder übel Bulldozer sein, CMP Scratch und der Loop Detektor in der BranchPrediciton hat Intel wohl weniger, auch wenn man nicht weiss, was SandyBridge bringen wird.

Edit

Naja, wenn mans dann mal genau anschaut, kommt eigentlich DDboys Schema raus...

Den Bulldozer habe ich darin auch erkannt, mit vielen Details, die nicht von mir stammen. Inwiefern nun die "Bekannten aus der Industrie" von "Hard Ball" eine Rolle spielen, wissen wir nicht. Aber Begriffe wie "Drain", "Payload" oder "epoch" stammen zumindest nicht aus den Patenten (soweit ich das überblicke). Ich werde mal darüber bloggen, just for the record..

Opteron

Redaktion

☆☆☆☆☆☆

Jo das mit den Epoch schaut interessant aus, scheint ne Art Sparversion von Transactional Memory zu sein, erinnert irgendwie an NCQ bei den Festplatten:

http://pages.cs.wisc.edu/~isca2005/slides/08A-01.PPT

http://www.cs.duke.edu/ari/spider-web/spring05/slides-1-19.ppt

Edit:

Wobei dir Frage aufkommt, wie das jetzt im Moment geht, round robin wie der L3 Zugriff ?

ciao

Alex

http://pages.cs.wisc.edu/~isca2005/slides/08A-01.PPT

http://www.cs.duke.edu/ari/spider-web/spring05/slides-1-19.ppt

Edit:

Wobei dir Frage aufkommt, wie das jetzt im Moment geht, round robin wie der L3 Zugriff ?

ciao

Alex

Zuletzt bearbeitet:

mocad_tom

Admiral Special

- Mitglied seit

- 17.06.2004

- Beiträge

- 1.234

- Renomée

- 52

Nochmal ein paar Spekulationen dazu, von woher die Dinge geleaked sein könnten:

Ich habe es mal von irgendwo her klingeln hören, dass Sam Naffziger auf der ISSCC 2010 vom 7.-11. Februar einen Vortrag halten soll.

Call for Papers endet am 14. September

Natürlich kann das auch purer Zufall sein.

Grüße,

Tom

Ich habe es mal von irgendwo her klingeln hören, dass Sam Naffziger auf der ISSCC 2010 vom 7.-11. Februar einen Vortrag halten soll.

Call for Papers endet am 14. September

Natürlich kann das auch purer Zufall sein.

Grüße,

Tom

Markus Everson

Grand Admiral Special

Muss doch wohl oder übel Bulldozer sein,

Das kann gar nicht sein, der einzige wahre Schaltplan von Bulldozer wurde von mir am Freitag abend in der Pizzeria "Taverna" auf eine Serviette gemalt. Alle anderen Fanzeichnungen entbehren jeder Grundlage.

Scherz beiseite und Dresdenboy bitte nicht falsch verstehen. Aber das hat doch mit Spekulation nur mehr am Rande zu tun wenn sich ein paar Fanboys mit einem fröhlichen "zeigst Du mir Deins zeig ich Dir meins" ihre Phantasien zuposten. Fehlt nur noch das rkinet sich künstlerisch betätigt. Falls er neben seiner Beratertätigkeit für das AMD-Management dazu noch Zeit findet.

SPawner

Fleet Captain Special

- Mitglied seit

- 25.08.2008

- Beiträge

- 292

- Renomée

- 4

Hmm er schreibt selbst:

Also ein Student (oder vllt. doch ein Grundschüler? ^^) der das Diagram zuhause gemacht hat.

I'm still in grad school

Also ein Student (oder vllt. doch ein Grundschüler? ^^) der das Diagram zuhause gemacht hat.

Triskaine

Lt. Commander

- Mitglied seit

- 19.01.2009

- Beiträge

- 105

- Renomée

- 12

Ich habe ihn jetzt mal drauf angesprochen, mal schauen wie er reagiert. Hier die links zu den beiden threads:

http://episteme.arstechnica.com/eve/forums/a/tpc/f/77909774/m/574007521041

http://forums.anandtech.com/messageview.aspx?FTVAR_FORUMVIEWTMP=Linear&catid=28&threadid=2332684

http://episteme.arstechnica.com/eve/forums/a/tpc/f/77909774/m/574007521041

http://forums.anandtech.com/messageview.aspx?FTVAR_FORUMVIEWTMP=Linear&catid=28&threadid=2332684

mocad_tom

Admiral Special

- Mitglied seit

- 17.06.2004

- Beiträge

- 1.234

- Renomée

- 52

Wahnsinn, wieviele Befehle werden da wohl on the fly unterwegs sein und wie viel wird durch eine falsche Spekulation mit einem Wisch ausradiert.

RAT -> register alias table

SRAT -> ?Source?RAT

CRAT -> WTF

Schaut euch nur mal den "Versioning write Cache" an, so wie es aussieht - ich kann mich täuschen - gibt es die Möglichkeit vier unterschiedliche Szenarios gleichzeitig zu versionieren und sich praktisch für ein Szenario zu entscheiden.

http://www.realworldtech.com/page.cfm?ArticleID=RWT040208182719&p=6

Der Transistor-Count pro Kern (ohne Caches) ist bei Nehalem deutlich angestiegen - bei Bulldozer wird dies noch deutlich stärker ansteigen. Vor allen Dingen könnte das Konzept endlich den so lange erhofften L0-Cache mitbringen, wenn auch nur für Integer (dort, wo es am meisten bringt).

Grüße,

Tom

.

EDIT :

.

Habe ich eigentlich schon erwähnt, dass es an solchen Tagen immer besonders lohnenswert ist einen Blick auf die Seiten von Hiroshige Goto zu werfen

http://pc.watch.impress.co.jp/docs/column/kaigai/

Noch ist aber nichts zählbares dabei rausgekommen.

Grüße,

Tom

RAT -> register alias table

SRAT -> ?Source?RAT

CRAT -> WTF

Schaut euch nur mal den "Versioning write Cache" an, so wie es aussieht - ich kann mich täuschen - gibt es die Möglichkeit vier unterschiedliche Szenarios gleichzeitig zu versionieren und sich praktisch für ein Szenario zu entscheiden.

http://www.realworldtech.com/page.cfm?ArticleID=RWT040208182719&p=6

Intel hat beim Sprung von Core 2 auf Nehalem mächtig an den Reorder Buffers etc. pp. gedreht, aber das sieht mir nach deutlich mehr aus.As with Core 2, the register alias table (RAT) points each architectural register into either the Re-Order Buffer (ROB) or the Retirement Register File (RRF) and holds the most recent speculative state (whereas the RRF holds the most recent non-speculative and committed state). The RAT can rename up to 4 uops each cycle, giving each one a destination register in the ROB. The renamed instructions then read their source operands and issue into the unified Reservation Station (RS), which is used by all instruction types. The ROB was enlarged from 96 to 128 entries with Nehalem, and the RS grew from 32 to 36 entries. Both the ROB and RS are shared across the two threads, but using different policies.

Der Transistor-Count pro Kern (ohne Caches) ist bei Nehalem deutlich angestiegen - bei Bulldozer wird dies noch deutlich stärker ansteigen. Vor allen Dingen könnte das Konzept endlich den so lange erhofften L0-Cache mitbringen, wenn auch nur für Integer (dort, wo es am meisten bringt).

Grüße,

Tom

.

EDIT :

.

Habe ich eigentlich schon erwähnt, dass es an solchen Tagen immer besonders lohnenswert ist einen Blick auf die Seiten von Hiroshige Goto zu werfen

http://pc.watch.impress.co.jp/docs/column/kaigai/

Noch ist aber nichts zählbares dabei rausgekommen.

Grüße,

Tom

Dresdenboy

Redaktion

☆☆☆☆☆☆

Das kann gar nicht sein, der einzige wahre Schaltplan von Bulldozer wurde von mir am Freitag abend in der Pizzeria "Taverna" auf eine Serviette gemalt. Alle anderen Fanzeichnungen entbehren jeder Grundlage.

Scherz beiseite und Dresdenboy bitte nicht falsch verstehen. Aber das hat doch mit Spekulation nur mehr am Rande zu tun wenn sich ein paar Fanboys mit einem fröhlichen "zeigst Du mir Deins zeig ich Dir meins" ihre Phantasien zuposten. Fehlt nur noch das rkinet sich künstlerisch betätigt. Falls er neben seiner Beratertätigkeit für das AMD-Management dazu noch Zeit findet.

Ich finde, dass der Junge viel zu viel auf einmal richtig bzw. zumindest passend und plausibel in der Zeichnung hat. Sehr vieles davon kann in AMDs Patenten gefunden werden. Das alles zu erfassen, zu plausibilisieren, zusammenzubringen und auch noch zu zeichnen erfordert viel Aufwand.

Weiterhin ergeben fast alle Dinge Sinn. Jemand aus einer Graduate School kann bei uns mit einem Doktoranden gleichstehen. Aber soviel Sinn auf einmal in eine Zeichnung zu integrieren klappt entweder nur mit tiefgründigen Kenntnissen (min. etwas davon im Studium gehabt) oder einer Vorlage... Was meinte mocad_tom noch...?

Ein bisschen kommt es mir aber auch vor (Alternativerklärung) wie wenn Däniken die Bibel dahingehend deutet, dass Ahnungslosere etwas über komplexe Dinge berichteten, jehnseits ihres Verständnisses.

Opteron

Redaktion

☆☆☆☆☆☆

Naja, das er ne Vorlag hatte, ist mit dem Text doch klar:Weiterhin ergeben fast alle Dinge Sinn. Jemand aus einer Graduate School kann bei uns mit einem Doktoranden gleichstehen. Aber soviel Sinn auf einmal in eine Zeichnung zu integrieren klappt entweder nur mit tiefgründigen Kenntnissen (min. etwas davon im Studium gehabt) oder einer Vorlage... Was meinte mocad_tom noch...?

Ein bisschen kommt es mir aber auch vor (Alternativerklärung) wie wenn Däniken die Bibel dahingehend deutet, dass Ahnungslosere etwas über komplexe Dinge berichteten, jehnseits ihres Verständnisses.

Nachdem das immernoch recht genau ist, wird er sich kaum auf Dein letztes Bildchen beziehenIt is actually roughly based on a commercial microarchitecture that might be coming on market in the near to medium term (depends on what you consider "near"); but I have altered, omitted, and replaced a number of architectural elements and mechanisms so that nothing useful in terms of the original design or specifications could be deciphered, while still ending up with a functional conceptual design.

ciao

Alex

Markus Everson

Grand Admiral Special

Ich finde, dass der Junge viel zu viel auf einmal richtig bzw. zumindest passend und plausibel in der Zeichnung hat [...] erfordert viel Aufwand [...] ergeben fast alle Dinge Sinn [...] soviel Sinn auf einmal in eine Zeichnung zu integrieren [...]

Kurz zusammengefaßt: Du möchtest gerne glauben das es wahr ist. Was nichts verkehrtes ist.

Aber hier wird teilweise auf diese Zeichnungen referenziert als wären sie faktenbasiert. Es muß aber bis zum Nachweis des Gegenteils davon ausgegangen werden das sie genauso wie Deine Zeichnungen lediglich Spekulation sind die mehr oder weniger nahe an der Wirklichkeit liegen _können_.

mocad_tom

Admiral Special

- Mitglied seit

- 17.06.2004

- Beiträge

- 1.234

- Renomée

- 52

Ich will nochmal kurz auf meine Spekulation auf der Seite davor eingehen.

Mein Punkt war

- Bulldozer wird ein richtig dickes Transistoren-Monster

- um im Idle (C0 und min-P-State) Strom zu sparen wird Bulldozer komplett stromlos gemacht und Bobcat, ein Prozessor, der genau den gleichen Befehlsumfang und genau den gleichen Register-Satz besitzt übernimmt die Arbeit

Diese Idee ist nicht komplett aus der Luft gegriffen sondern wird bereits (in ähnlicher Form) im Smartphone ihres Vertrauens eingesetzt.

Ich fand die Meldung damals so witzig, dass ich sie gleich Bookmarken musste:

http://mobile.msmobiles.com/news.php?id=1993

Kurz zusammengefasst - im ARM710 stecken zwei Kerne

- ein energie-sparender ARM7 zum Betreiben von GSM

- ein ARM9, auf dem Windows Mobile läuft

Erklärung:

Das Smartphone bucht sich in das GSM-Netz ein, der ARM7-Kern ist dauernd am Laufen, er benötigt extrem wenig Energie, irgendwo im Bereich von 1-2mA. Würde der ARM9-Kern dauernd laufen wäre dies nie im Leben zu erreichen, da der ARM9 deutlich zu viele Transistoren mit Strom versorgen müsste.

Pointe in der Geschichte ATI Technologies liefert das RT-Unix

Grüße,

Tom

Mein Punkt war

- Bulldozer wird ein richtig dickes Transistoren-Monster

- um im Idle (C0 und min-P-State) Strom zu sparen wird Bulldozer komplett stromlos gemacht und Bobcat, ein Prozessor, der genau den gleichen Befehlsumfang und genau den gleichen Register-Satz besitzt übernimmt die Arbeit

Diese Idee ist nicht komplett aus der Luft gegriffen sondern wird bereits (in ähnlicher Form) im Smartphone ihres Vertrauens eingesetzt.

Ich fand die Meldung damals so witzig, dass ich sie gleich Bookmarken musste:

http://mobile.msmobiles.com/news.php?id=1993

HTC SmartPhones (HTC Voyager, HTC Tanager, HTC Canary) are powered by TI OMAP 710a from Texas Instruments - a processor that unites 2 processor cores: 1. energy-saving ARM7 for GSM and peripherals, 2. ARM9 for applications. Smartphone operating system, that runs on top of Windows CE core, is running over the ARM9 processor core. But what operating system is running on the ARM7 processor core? Answer: Unix.

... or exactly speaking a special kind of Unix - Real Time Unix. After analysis of the ROM image dumps, the following was found:

Copyright (c) 1993 ATI - Nucleus PLUS - Version 1.0.G1.1

Texas Instruments delivers to hardware manufacturers (like HTC) a reference design + reference operating system for ARM7 (based on the "Nucleus PLUS") - so that manufacturers can try out features - like GSM, Bluetooth, battery loading control, camera, etc.

HTC however takes this reference operating system for ARM7, adds on top of it some non-essential features like SIM lock and says "ready!". In this way Microsoft Smartphones from HTC are running both Unix and Windows in parallel: Unix makes the dirty work and Windows gets the clear stuff.

Kurz zusammengefasst - im ARM710 stecken zwei Kerne

- ein energie-sparender ARM7 zum Betreiben von GSM

- ein ARM9, auf dem Windows Mobile läuft

Erklärung:

Das Smartphone bucht sich in das GSM-Netz ein, der ARM7-Kern ist dauernd am Laufen, er benötigt extrem wenig Energie, irgendwo im Bereich von 1-2mA. Würde der ARM9-Kern dauernd laufen wäre dies nie im Leben zu erreichen, da der ARM9 deutlich zu viele Transistoren mit Strom versorgen müsste.

Pointe in der Geschichte ATI Technologies liefert das RT-Unix

Grüße,

Tom

nonworkingrich

Captain Special

- Mitglied seit

- 28.04.2006

- Beiträge

- 234

- Renomée

- 4

Das ist ne andere ATI als du wahrscheinlich meinst, oder?Pointe in der Geschichte ATI Technologies liefert das RT-Unix

Accelerated Technology(R), the Embedded Systems Division of Mentor Graphics Corporation

Ähnliche Themen

- Antworten

- 0

- Aufrufe

- 933

- Antworten

- 80

- Aufrufe

- 15K

- Antworten

- 2

- Aufrufe

- 3K

- Antworten

- 764

- Aufrufe

- 101K

- Antworten

- 8

- Aufrufe

- 2K

![Augen rollen (sarkastisch) :] :]](https://www.planet3dnow.de/vbulletin/images/smilies/rolleyes.gif)