App installieren

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: This feature may not be available in some browsers.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

News Llano Athlons und Semprons CPUs (ohne Grafik) ? [Update]

- Ersteller Crashtest

- Erstellt am

User-News

Von Crashtest

Hinweis: Diese "User-News" wurde nicht von der Planet 3DNow! Redaktion veröffentlicht, sondern vom oben genannten Leser, der persönlich für den hier veröffentlichten Inhalt haftet.Das AMD'sche Namenschaos bei der Family 12h könnte in die nächste Runde gehen wenn man dem AGESA innerhalb der BIOSe traut, da findet man:

Weiter enden nicht alle auf APU sondern einige auf Processor sodass es sich offenbar um CPU handeln könnte ( IGP-Teil deaktiviert ? )

Triple- und Quadcore Semprons

Quelle : BIOS F3G des Gigabyte GA-A75-UD4H (rev. 1.0) @ http://www.gigabyte.com/products/product-page.aspx?pid=3927#dl

Nachtrag 09.07.2011:

Bestätigt durch ASUS F1A75-V Pro

Update 27.12.2011

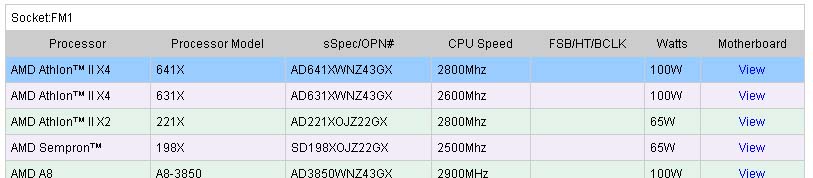

AMD hat die Produktspezifikationen für die Athlons und Semprons freigegeben (beides PDFs)

AGESA LlanoPI V1.1.0.2

AMD Sempron(tm) II 1

AMD Athlon(tm) II 1

AMD E2-1

AMD Sempron(tm) II

AMD Athlon(tm) II

AMD Sempron(tm) FM1

AMD Athlon(tm) FM1

AMD Sempron(tm) 1

AMD A4-33

AMD E2-32

AMD Sempron(tm) II X2 2

AMD Athlon(tm) II X2 2

AMD A4-34

AMD A4-3

AMD E2-3

AMD Sempron(tm) II X2

AMD Athlon(tm) II X2

AMD Sempron(tm) FM1 X2

AMD Athlon(tm) FM1 X2

AMD Sempron(tm) X2 1

AMD Sempron(tm) X2 2

AMD A6-34

AMD Sempron(tm) II X3 3

AMD Athlon(tm) II X3 3

AMD A6-36

AMD A6-35

AMD A6-3

AMD Sempron(tm) II X3

AMD Athlon(tm) II X3

AMD Sempron(tm) FM1 X3

AMD Athlon(tm) FM1 X3

AMD Athlon(tm) II X3 4

AMD A8-35

AMD Sempron(tm) II X4 4

AMD Athlon(tm) II X4 4

AMD A8-38

AMD A8-3

AMD Sempron(tm) II X4

AMD Athlon(tm) II X4

AMD Sempron(tm) FM1 X4

AMD Athlon(tm) FM1 X4

AMD Athlon(tm) II X4 6

Weiter enden nicht alle auf APU sondern einige auf Processor sodass es sich offenbar um CPU handeln könnte ( IGP-Teil deaktiviert ? )

APU with Radeon(tm) HD Graphics

Processor

P APU with Radeon(tm) HD Graphics

0 APU with Radeon(tm) HD Graphics

0P APU with Radeon(tm) HD Graphics

0 Processor

Dual-Core Processor

0 Dual-Core Processor

Triple-Core Processor

0 Triple-Core Processor

Quad-Core Processor

0 Quad-Core Processor

Triple- und Quadcore Semprons

Quelle : BIOS F3G des Gigabyte GA-A75-UD4H (rev. 1.0) @ http://www.gigabyte.com/products/product-page.aspx?pid=3927#dl

Nachtrag 09.07.2011:

Bestätigt durch ASUS F1A75-V Pro

Update 27.12.2011

AMD hat die Produktspezifikationen für die Athlons und Semprons freigegeben (beides PDFs)

Zuletzt bearbeitet:

OBrian

Moderation MBDB, ,

- Mitglied seit

- 16.10.2000

- Beiträge

- 17.031

- Renomée

- 267

- Standort

- NRW

- Details zu meinem Desktop

- Prozessor

- Phenom II X4 940 BE, C2-Stepping (undervolted)

- Mainboard

- Gigabyte GA-MA69G-S3H (BIOS F7)

- Kühlung

- Noctua NH-U12F

- Speicher

- 4 GB DDR2-800 ADATA/OCZ

- Grafikprozessor

- Radeon HD 5850

- Display

- NEC MultiSync 24WMGX³

- SSD

- Samsung 840 Evo 256 GB

- HDD

- WD Caviar Green 2 TB (WD20EARX)

- Optisches Laufwerk

- Samsung SH-S183L

- Soundkarte

- Creative X-Fi EM mit YouP-PAX-Treibern, Headset: Sennheiser PC350

- Gehäuse

- Coolermaster Stacker, 120mm-Lüfter ersetzt durch Scythe S-Flex, zusätzliche Staubfilter

- Netzteil

- BeQuiet 500W PCGH-Edition

- Betriebssystem

- Windows 7 x64

- Webbrowser

- Firefox

- Verschiedenes

- Tastatur: Zowie Celeritas Caseking-Mod (weiße Tasten)

Möglicherweise irgendwas Teildeaktiviertes für Asien

Crashtest

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 11.11.2008

- Beiträge

- 9.311

- Renomée

- 1.434

- Standort

- Leipzig

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- Collatz, yoyo, radac

- Lieblingsprojekt

- yoyo

- Meine Systeme

- Ryzen: 2x1600, 5x1700, 1x2700,1x3600, 1x5600X; EPYC 7V12 und Kleinzeuch

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Lenovo IdeaPad 5 14ALC05

- Details zu meinem Desktop

- Prozessor

- Ryzen 7950X / Ryzen 4750G

- Mainboard

- ASRock B650M PGRT / X570D4U

- Kühlung

- be quiet! Dark Rock Pro4 / Pure Rock Slim 2

- Speicher

- 64GB DDR5-5600 G Skill F5-5600J3036D16G / 32 GB DDR4-3200 ECC

- Grafikprozessor

- Raphael IGP / ASpeed AST-2500

- Display

- 27" Samsung LF27T450F

- SSD

- KINGSTON SNVS2000G

- HDD

- - / 8x Seagate IronWolf Pro 20TB

- Optisches Laufwerk

- 1x B.Ray - LG BD-RE BH16NS55

- Soundkarte

- onboard HD?

- Gehäuse

- zu kleines für die GPU

- Netzteil

- be quiet! Pure Power 11 400W / dito

- Tastatur

- CHERRY SECURE BOARD 1.0

- Maus

- Logitech RX250

- Betriebssystem

- Windows 10 19045.4355 / Server 20348.2402

- Webbrowser

- Edge 124.0.2478.51

- Verschiedenes

- U320 SCSI-Controller !!!!

- Internetanbindung

- ▼1000 MBit ▲82 MBit

Tja ich finde der Grafikteil im Zacante reicht für Office/Internet - wer mehr will verwendet eh eine richtige Grafikkarte. Und da AMD die Platform Sockel FMx weiter verwenden will, hätte ein CPU mit NB und PCI-Root-Complex ohne int. Grafik auch eine Daseinsberechtigung.

Leider steht noch nix im Revision Guide - wobei darin noch nicht einmal die Desktop APUs enthalten sind - AMD sollte mal ein Update freigeben.

Leider steht noch nix im Revision Guide - wobei darin noch nicht einmal die Desktop APUs enthalten sind - AMD sollte mal ein Update freigeben.

nazgul99

Grand Admiral Special

- Mitglied seit

- 01.05.2005

- Beiträge

- 3.592

- Renomée

- 224

- Standort

- Irgendwo in der Nähe

- Mein Laptop

- ThinkPad Edge E145 / 8GB / M500 480GB / Kubuntu /// Asus U38N / 6GB / Matt / Postville / Kubuntu/W8

- Details zu meinem Desktop

- Prozessor

- AMD A10-7800

- Mainboard

- MSI A88XI AC

- Kühlung

- Scythe Shuriken Rev.2

- Speicher

- 2x 8GB DDR3-2133

- Grafikprozessor

- IGP

- Display

- HP LP2465, MVA, 1920x1200, 24"

- SSD

- Samsung 850 EVO 500GB

- HDD

- ST9500325AS 500GB

- Optisches Laufwerk

- ja, so'n USB-Dings

- Soundkarte

- onboard, optisch -> SMSL Q5 PRO -> ELAC EL60

- Gehäuse

- Silverstone ML06B

- Netzteil

- SST-ST30SF

- Betriebssystem

- Kubuntu

- Webbrowser

- Firefox

- Verschiedenes

- Synology DS414slim 3x 1,5 TB RAID5

Schön, dass es hier immer wieder Schlaumeier gibt die wissen, was andere Leute brauchen oder nicht brauchenTja ich finde der Grafikteil im Zacante reicht für Office/Internet - wer mehr will verwendet eh eine richtige Grafikkarte.

![Augen rollen (sarkastisch) :] :]](https://www.planet3dnow.de/vbulletin/images/smilies/rolleyes.gif)

Mit derlei CPUs würde das Asus F1M75 ohne Display-Anschlüsse denn doch Sinn machen, allerdings wäre für das Low-End ein µATX-Board eigentlich angemessener.Und da AMD die Platform Sockel FMx weiter verwenden will, hätte ein CPU mit NB und PCI-Root-Complex ohne int. Grafik auch eine Daseinsberechtigung.

Auf products.amd.com auch noch nichtLeider steht noch nix im Revision Guide - wobei darin noch nicht einmal die Desktop APUs enthalten sind - AMD sollte mal ein Update freigeben.

pipip

Captain Special

- Mitglied seit

- 17.03.2011

- Beiträge

- 209

- Renomée

- 2

- Mein Laptop

- HP625

- Details zu meinem Laptop

- Prozessor

- N930@2Ghz , 0,9250Volt

- Speicher

- 4gig

- Grafikprozessor

- AMD HD4200

xD lustig wäre es wenn der Sempron II ohne Grafikeinheit besser overclocken lässt als seine Brüder mit iGP. Somit wäre dann so eine CPU für ein Asus F1M75 ohne Display-Anschlüsse wieder interessant.

Opteron

Redaktion

☆☆☆☆☆☆

Hmm .. hmm ..

eventuell sind das erstmal nur Platzhalter? Wenn ich mich recht erinnere, dann hattest Du doch mal geschrieben, dass die BDs in den AM3+ BIOSen noch als Athlon X8 oder so benannt waren, oder?

Wobei die unterscheidung nach Athlon und Sempron schon komisch ist ... was Sinn machen würde, wären vielleicht die kommenden 28nm Bobcat-Quads. Aber selbst die sollten ja ne IGP mitbekommen...

eventuell sind das erstmal nur Platzhalter? Wenn ich mich recht erinnere, dann hattest Du doch mal geschrieben, dass die BDs in den AM3+ BIOSen noch als Athlon X8 oder so benannt waren, oder?

Wobei die unterscheidung nach Athlon und Sempron schon komisch ist ... was Sinn machen würde, wären vielleicht die kommenden 28nm Bobcat-Quads. Aber selbst die sollten ja ne IGP mitbekommen...

Zuletzt bearbeitet:

Bobo_Oberon

Grand Admiral Special

- Mitglied seit

- 18.01.2007

- Beiträge

- 5.045

- Renomée

- 190

Interessante Spekulationen ... vor allem wenn man das paradoxe Asus-Mainboard noch dazu betrachtet.

Da wird wohl aus dem geplanten sehr einfachen übersichtlichen Sticker-Ratingeine Begriffsvielfalt ein echtes Chaos werden ... Wie viel hat AMD einer PR-Agentur bezahlt, damit die Sticker-/Labelitis Einhalt geboten wird? 8)

Aber wer kauft denn solche grafiklosen APUs? In eine Officekiste eines Marken-OEMs kommen die ziemlich sicher nicht rein. Und vor allem wie "teuer" werden solche K*-APUs?

MFG Bobo(2011)

* = K -> "Kaputt"

Da wird wohl aus dem geplanten sehr einfachen übersichtlichen Sticker-Rating

Aber wer kauft denn solche grafiklosen APUs? In eine Officekiste eines Marken-OEMs kommen die ziemlich sicher nicht rein. Und vor allem wie "teuer" werden solche K*-APUs?

MFG Bobo(2011)

* = K -> "Kaputt"

Möglicherweise irgendwas Teildeaktiviertes für Asien

Ich denke, dass AMD - wenn noch etwas auf Lager ist, was bisher in die Produktfamilie nicht so passte, da teildefekt oder sonst irgendwas, es gern auf den Markt wirft. Es also durchaus vorstellbar, dass 'so etwas' regional begrenzt angeboten wird.

Und so soll es ja nicht am Namen scheitern...

Ich erwarte so wieso, dass K10.5 in Reinkultur uns noch ein Weilchen erhalten bleibt und er noch weit ins Jahr 2012 verkauft werden wird - ob nun noch produziert oder von der Halde ist erst einmal egal.

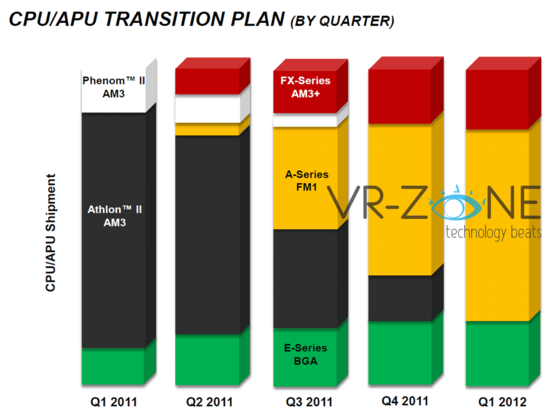

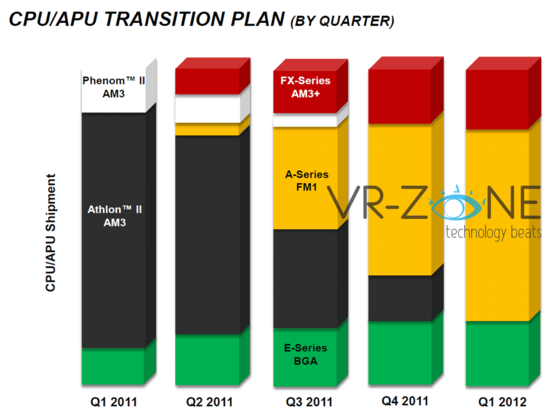

Das hier mag schon wieder ueberholt sein - und war vielleicht mal der Produktionsplan/wunsch.

Und auch hier sieht man, dass zu meist K10.5 Kerne AMD Pforte verlassen bis hinein ins Q03. Von der Anzahl sogar mehr als die kleinen APUs.

Bobo_Oberon

Grand Admiral Special

- Mitglied seit

- 18.01.2007

- Beiträge

- 5.045

- Renomée

- 190

Was mich wohl am meisten beeindruckt ist der sehr hohe Anteil von Athlon-Produkten. Da bin echt überrascht - die CPU-Margen dürften wirklich grottig sein, wenns nicht noch die kleinen Bobcat-Produkte gäbe.

Auch die Zeitpunkte erscheinen doch recht merkwürdig. Selbst wenn die Quartale die "Eingänge" bei AMD bezeichnen, also die Lieferung von GlobalFoundries und TSMC empfangen.

Denn der Wareneingang als Chip bei AMD bedeutet ja noch lange nicht der Verkauf eines Prozessorprodukts an die OEMs und die Endkunden an der Ladentheke. Also mit anderen Worten, letzte Woche befanden wir uns aus Endkundensicht noch im Balken des ersten Quartals und sind nun aktuell am Anfang des zweiten Balkens. Der Juli ist hingegen nun schon das dritte Quartal - ...

Da fällt mir ein, wie bezeichnet denn AMD die jeweiligen Quartale? Diese börsentechnische Bilanzierungseinteilung hat mitunter gar nichts mit den richtigen kalendarischen Einteilungen zu tun?! Nun ja, wie dem auch sei - ob verschoben oder nicht, so wirds sich wohl von der Marktaufteilung bei AMD bewegen.

MFG Bobo(2011)

Crashtest

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 11.11.2008

- Beiträge

- 9.311

- Renomée

- 1.434

- Standort

- Leipzig

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- Collatz, yoyo, radac

- Lieblingsprojekt

- yoyo

- Meine Systeme

- Ryzen: 2x1600, 5x1700, 1x2700,1x3600, 1x5600X; EPYC 7V12 und Kleinzeuch

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Lenovo IdeaPad 5 14ALC05

- Details zu meinem Desktop

- Prozessor

- Ryzen 7950X / Ryzen 4750G

- Mainboard

- ASRock B650M PGRT / X570D4U

- Kühlung

- be quiet! Dark Rock Pro4 / Pure Rock Slim 2

- Speicher

- 64GB DDR5-5600 G Skill F5-5600J3036D16G / 32 GB DDR4-3200 ECC

- Grafikprozessor

- Raphael IGP / ASpeed AST-2500

- Display

- 27" Samsung LF27T450F

- SSD

- KINGSTON SNVS2000G

- HDD

- - / 8x Seagate IronWolf Pro 20TB

- Optisches Laufwerk

- 1x B.Ray - LG BD-RE BH16NS55

- Soundkarte

- onboard HD?

- Gehäuse

- zu kleines für die GPU

- Netzteil

- be quiet! Pure Power 11 400W / dito

- Tastatur

- CHERRY SECURE BOARD 1.0

- Maus

- Logitech RX250

- Betriebssystem

- Windows 10 19045.4355 / Server 20348.2402

- Webbrowser

- Edge 124.0.2478.51

- Verschiedenes

- U320 SCSI-Controller !!!!

- Internetanbindung

- ▼1000 MBit ▲82 MBit

Der Grund für CPUs auf Sockel FMx könnte ganz einfach die Tatsache sein, dass AMD den Sockel AM3+ an der kurzen Leine hält und außer dem Bulldozer da nix mehr kommt - und nebenbei die Produktion für Sockel AM3 CPUs eingestellt wird - nur nicht jeder will ein Bulldozer und nicht jeder will ne IGP.

Zum Thema Platzhalter ala Octal-Core Phenom:

es sind viel zu viele, insb. da da FM1 dabei steht ...

Zum Thema Platzhalter ala Octal-Core Phenom:

es sind viel zu viele, insb. da da FM1 dabei steht ...

Zuletzt bearbeitet:

was früher einmal HORUS genannt wurde -und einer anderen Firma gehörte -

ist bei AMD seit NEXGEN auf der Prozessorseite -seit der ominösen FUSION Ankündigung in 2006/07- eher kaum etwas wenn überhaupt dazugekommen.

Was dazugekommen ist, scheint -in Worten von Hector Ruiz- zu sein: "Man modularisiert hier ein wenig und da ein wenig".

Genau das zeigt sich bislang.

Ob die Athlon in Phenom "Ummodularisierung" reicht?

Jedenfalls gibt es genug und in den letzten Jahren AUSSCHLIESSLICHE Meldungen und Produkteinführungen , die sich quasi NUR auf ATI beziehen.

Kein Wunder also, dass der Börsenwert von AMD, kaum noch an den Kaufpreis von ATI heranreicht.

Vielmehr schlägt sich nieder, dass seit der nicht beherrschbaren Niederlage gegen den "Core 2 Duo"

-seitdem sind 1 Mrd Intel Gelder zudem noch in den Konzern geflossen,

um nicht die vorhergehenden unendlichen Subventionsmillionen der Staaten aufzulisten-

kaum ein nennenswerter Deut in der Entwicklung der Prozessoren geflossen ist;

ABSOLUTR ERHEBLICHE Anteile an den Fabrikationsanlagen Global Foundries und Spansion

ABER ABGEFLOSSEN sind.

Dieser Tage ist 2011. Seit 05 / 06 / 07 wird Fusion angekündigt. UND Bulldozer.

Der C2D ist kaum erreicht,

Und jetzt soll als Erguss einer Unternehmensstruktur ein Sempron X3 rauskommen ?

Ausgelutscht ist Nexgen.

Mittlerweile ausgelutscht das KnowHow von ATI.

Jetzt kommt ein wenig Software drauf.

Irgendein unendliches Abgemisch während der trewiberinstallation, und die Büchse läuft danach genau so doof wie vorher.

Da muss man schon die letzten 10 Jahre nicht gelebt haben oder einer Webseite in Gruen betreiben,

ist bei AMD seit NEXGEN auf der Prozessorseite -seit der ominösen FUSION Ankündigung in 2006/07- eher kaum etwas wenn überhaupt dazugekommen.

Was dazugekommen ist, scheint -in Worten von Hector Ruiz- zu sein: "Man modularisiert hier ein wenig und da ein wenig".

Genau das zeigt sich bislang.

Ob die Athlon in Phenom "Ummodularisierung" reicht?

Jedenfalls gibt es genug und in den letzten Jahren AUSSCHLIESSLICHE Meldungen und Produkteinführungen , die sich quasi NUR auf ATI beziehen.

Kein Wunder also, dass der Börsenwert von AMD, kaum noch an den Kaufpreis von ATI heranreicht.

Vielmehr schlägt sich nieder, dass seit der nicht beherrschbaren Niederlage gegen den "Core 2 Duo"

-seitdem sind 1 Mrd Intel Gelder zudem noch in den Konzern geflossen,

um nicht die vorhergehenden unendlichen Subventionsmillionen der Staaten aufzulisten-

kaum ein nennenswerter Deut in der Entwicklung der Prozessoren geflossen ist;

ABSOLUTR ERHEBLICHE Anteile an den Fabrikationsanlagen Global Foundries und Spansion

ABER ABGEFLOSSEN sind.

Dieser Tage ist 2011. Seit 05 / 06 / 07 wird Fusion angekündigt. UND Bulldozer.

Der C2D ist kaum erreicht,

Und jetzt soll als Erguss einer Unternehmensstruktur ein Sempron X3 rauskommen ?

Ausgelutscht ist Nexgen.

Mittlerweile ausgelutscht das KnowHow von ATI.

Jetzt kommt ein wenig Software drauf.

Irgendein unendliches Abgemisch während der trewiberinstallation, und die Büchse läuft danach genau so doof wie vorher.

Da muss man schon die letzten 10 Jahre nicht gelebt haben oder einer Webseite in Gruen betreiben,

@kalkzone

sonst ist bei Dir aber schon noch alles klar?

Bobcat ist ein voller Erfolg als Ontario/Zacate und ist ein voller Fusion-Prozessor. wer soll den entwickelt haben, wenn nicht AMD?

Llano ist zugegeben beim Prozessorteil leistungstechnisch nicht auf dem höchsten Niveau, dafür in seiner Notebookform erstmals beim Stromsparen konkurrenzfähig dank ausgefeiltem Power- und Clockgating. Und das ist auch ein Fusion-Prozessor.

Nur weil die Prozessoren hier auftauchen heißt das auch noch nicht, dass das auch auf den Markt kommt. Aber das scheint dich irgendwie nicht zu interessieren, weil das deinen etwas unglücklichen Ausfluss von wirren Gedanken zu einem höchst lächerlichen Vorgang gemacht hätte.

Ich frag mich gerade ob dein Beitrag satirisch gemeint ist oder du etwas zuviel gelbe Gallenflüssigkeit angesammelt hast.....

sonst ist bei Dir aber schon noch alles klar?

Bobcat ist ein voller Erfolg als Ontario/Zacate und ist ein voller Fusion-Prozessor. wer soll den entwickelt haben, wenn nicht AMD?

Llano ist zugegeben beim Prozessorteil leistungstechnisch nicht auf dem höchsten Niveau, dafür in seiner Notebookform erstmals beim Stromsparen konkurrenzfähig dank ausgefeiltem Power- und Clockgating. Und das ist auch ein Fusion-Prozessor.

Ist ja nicht so, dass Intel massiv Marktmissbrauch betrieben und damit AMD die Ressourcen zur Entwicklung abgegraben hat.kalkzone schrieb:-seitdem sind 1 Mrd Intel Gelder zudem noch in den Konzern geflossen,

um nicht die vorhergehenden unendlichen Subventionsmillionen der Staaten aufzulisten-

Nur weil die Prozessoren hier auftauchen heißt das auch noch nicht, dass das auch auf den Markt kommt. Aber das scheint dich irgendwie nicht zu interessieren, weil das deinen etwas unglücklichen Ausfluss von wirren Gedanken zu einem höchst lächerlichen Vorgang gemacht hätte.

Ich frag mich gerade ob dein Beitrag satirisch gemeint ist oder du etwas zuviel gelbe Gallenflüssigkeit angesammelt hast.....

Zuletzt bearbeitet:

Crashtest

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 11.11.2008

- Beiträge

- 9.311

- Renomée

- 1.434

- Standort

- Leipzig

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- Collatz, yoyo, radac

- Lieblingsprojekt

- yoyo

- Meine Systeme

- Ryzen: 2x1600, 5x1700, 1x2700,1x3600, 1x5600X; EPYC 7V12 und Kleinzeuch

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Lenovo IdeaPad 5 14ALC05

- Details zu meinem Desktop

- Prozessor

- Ryzen 7950X / Ryzen 4750G

- Mainboard

- ASRock B650M PGRT / X570D4U

- Kühlung

- be quiet! Dark Rock Pro4 / Pure Rock Slim 2

- Speicher

- 64GB DDR5-5600 G Skill F5-5600J3036D16G / 32 GB DDR4-3200 ECC

- Grafikprozessor

- Raphael IGP / ASpeed AST-2500

- Display

- 27" Samsung LF27T450F

- SSD

- KINGSTON SNVS2000G

- HDD

- - / 8x Seagate IronWolf Pro 20TB

- Optisches Laufwerk

- 1x B.Ray - LG BD-RE BH16NS55

- Soundkarte

- onboard HD?

- Gehäuse

- zu kleines für die GPU

- Netzteil

- be quiet! Pure Power 11 400W / dito

- Tastatur

- CHERRY SECURE BOARD 1.0

- Maus

- Logitech RX250

- Betriebssystem

- Windows 10 19045.4355 / Server 20348.2402

- Webbrowser

- Edge 124.0.2478.51

- Verschiedenes

- U320 SCSI-Controller !!!!

- Internetanbindung

- ▼1000 MBit ▲82 MBit

Tja nun sind diese CPU-Name auch in wenigstens einem BIOS von ASUS aufgetaucht ...

Also freuen wir uns doch auf Athlon II, Quadcore Sempron and Friends im Sockel FM1 gewandt - ohne (funktionierenden) Grafikteil , packen eine "richtige" Grafik dazu und daddeln einwenig mehr als mit der integrierten Grafik möglich ist ..

, packen eine "richtige" Grafik dazu und daddeln einwenig mehr als mit der integrierten Grafik möglich ist ..

Also freuen wir uns doch auf Athlon II, Quadcore Sempron and Friends im Sockel FM1 gewandt - ohne (funktionierenden) Grafikteil

, packen eine "richtige" Grafik dazu und daddeln einwenig mehr als mit der integrierten Grafik möglich ist ..

, packen eine "richtige" Grafik dazu und daddeln einwenig mehr als mit der integrierten Grafik möglich ist ..Onkel_Dithmeyer

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 22.04.2008

- Beiträge

- 12.949

- Renomée

- 4.038

- Standort

- Zlavti

- Aktuelle Projekte

- Universe@home

- Lieblingsprojekt

- Universe@home

- Meine Systeme

- cd0726792825f6f563c8fc4afd8a10b9

- BOINC-Statistiken

- Details zu meinem Desktop

- Prozessor

- Ryzen 9 3900X @4000 MHz//1,15V

- Mainboard

- MSI X370 XPOWER GAMING TITANIUM

- Kühlung

- Custom Wasserkühlung vom So. G34

- Speicher

- 4x8 GB @ 3000 MHz

- Grafikprozessor

- Radeon R9 Nano

- Display

- HP ZR30W & HP LP3065

- SSD

- 2 TB ADATA

- Optisches Laufwerk

- LG

- Soundkarte

- Im Headset

- Gehäuse

- Xigmatek

- Netzteil

- BeQuiet Dark Pro 9

- Tastatur

- GSkill KM570

- Maus

- GSkill MX780

- Betriebssystem

- Ubuntu 20.04

- Webbrowser

- Firefox Version 94715469

- Internetanbindung

- ▼100 Mbit ▲5 Mbit

Liest sich schon recht lustig ^^

Crashtest

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 11.11.2008

- Beiträge

- 9.311

- Renomée

- 1.434

- Standort

- Leipzig

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- Collatz, yoyo, radac

- Lieblingsprojekt

- yoyo

- Meine Systeme

- Ryzen: 2x1600, 5x1700, 1x2700,1x3600, 1x5600X; EPYC 7V12 und Kleinzeuch

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Lenovo IdeaPad 5 14ALC05

- Details zu meinem Desktop

- Prozessor

- Ryzen 7950X / Ryzen 4750G

- Mainboard

- ASRock B650M PGRT / X570D4U

- Kühlung

- be quiet! Dark Rock Pro4 / Pure Rock Slim 2

- Speicher

- 64GB DDR5-5600 G Skill F5-5600J3036D16G / 32 GB DDR4-3200 ECC

- Grafikprozessor

- Raphael IGP / ASpeed AST-2500

- Display

- 27" Samsung LF27T450F

- SSD

- KINGSTON SNVS2000G

- HDD

- - / 8x Seagate IronWolf Pro 20TB

- Optisches Laufwerk

- 1x B.Ray - LG BD-RE BH16NS55

- Soundkarte

- onboard HD?

- Gehäuse

- zu kleines für die GPU

- Netzteil

- be quiet! Pure Power 11 400W / dito

- Tastatur

- CHERRY SECURE BOARD 1.0

- Maus

- Logitech RX250

- Betriebssystem

- Windows 10 19045.4355 / Server 20348.2402

- Webbrowser

- Edge 124.0.2478.51

- Verschiedenes

- U320 SCSI-Controller !!!!

- Internetanbindung

- ▼1000 MBit ▲82 MBit

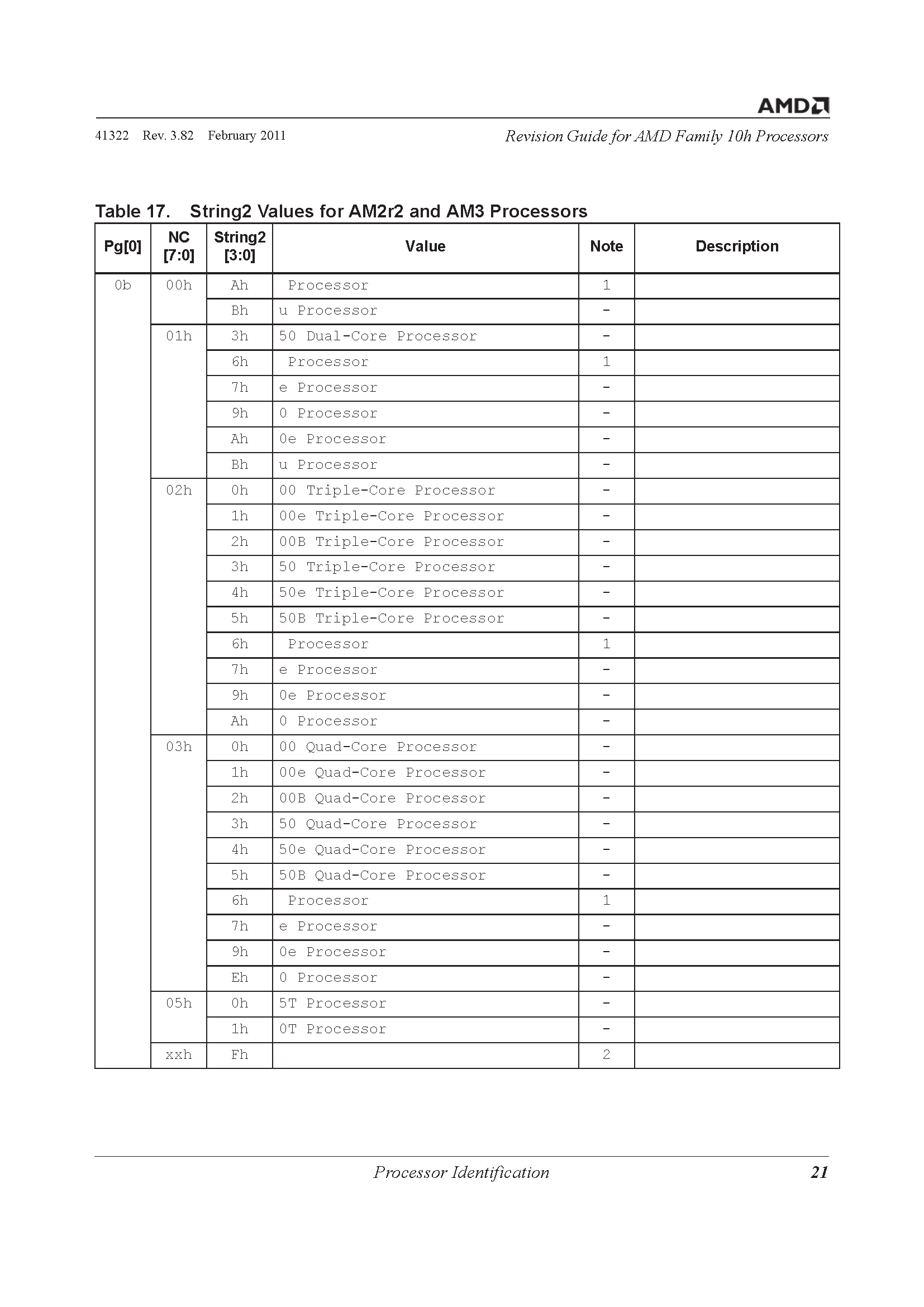

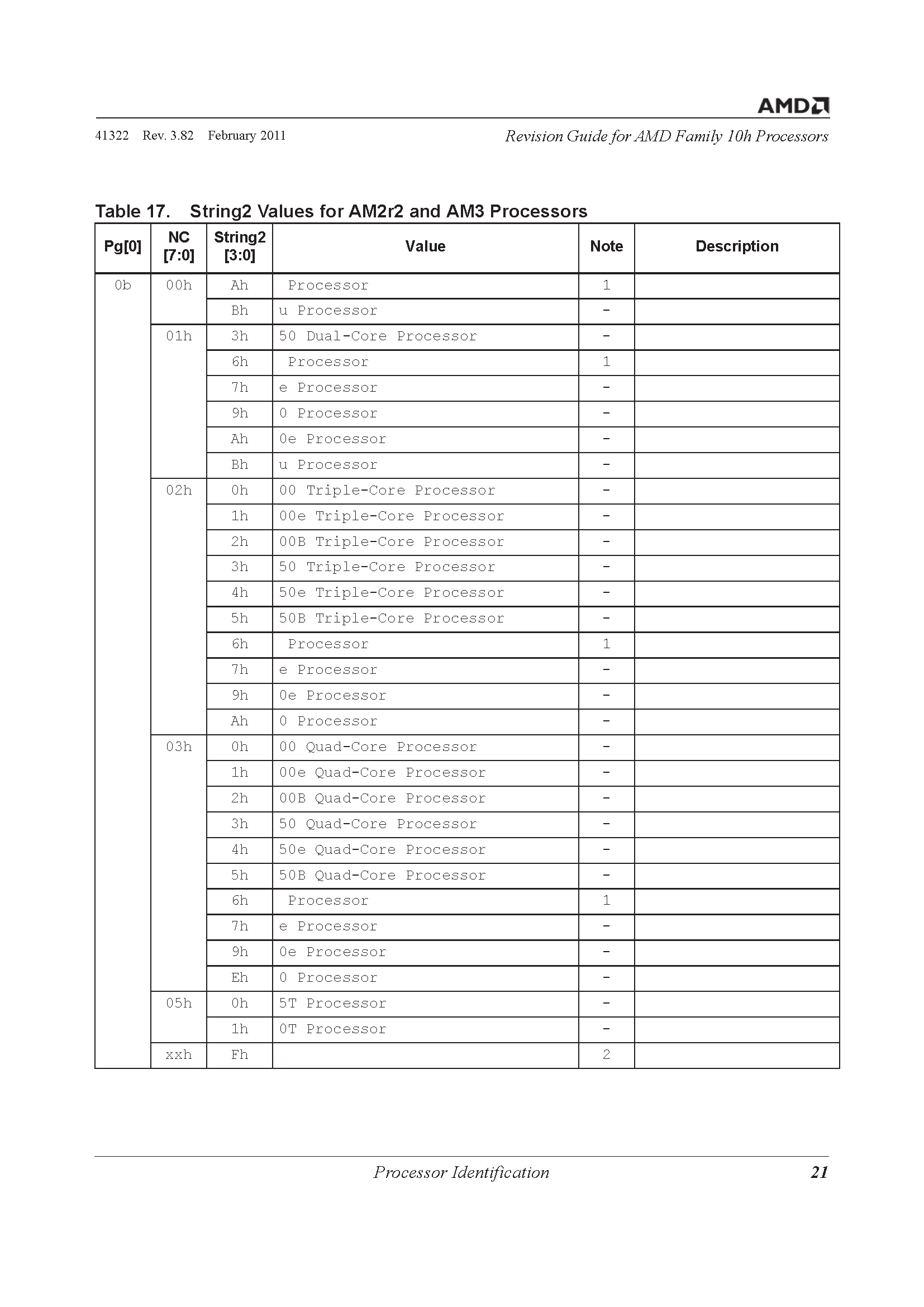

ist halt ne AGESA Liste aus der Matrix

daraus wird der "CPU-Namen-String" zusammengebaut:

etwa "AMD Sempron(tm) II 1" + Zahl + "Processor"

zum Vergleich mal die K10-Namen-Strings

daraus wird halt entsprechend der BrandID, Anzahl der Kerne (-1) uswusf halt der String zusammengebaut und er MSR in die CPU geschrieben

daraus wird der "CPU-Namen-String" zusammengebaut:

etwa "AMD Sempron(tm) II 1" + Zahl + "Processor"

zum Vergleich mal die K10-Namen-Strings

daraus wird halt entsprechend der BrandID, Anzahl der Kerne (-1) uswusf halt der String zusammengebaut und er MSR in die CPU geschrieben

Crashtest

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 11.11.2008

- Beiträge

- 9.311

- Renomée

- 1.434

- Standort

- Leipzig

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- Collatz, yoyo, radac

- Lieblingsprojekt

- yoyo

- Meine Systeme

- Ryzen: 2x1600, 5x1700, 1x2700,1x3600, 1x5600X; EPYC 7V12 und Kleinzeuch

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Lenovo IdeaPad 5 14ALC05

- Details zu meinem Desktop

- Prozessor

- Ryzen 7950X / Ryzen 4750G

- Mainboard

- ASRock B650M PGRT / X570D4U

- Kühlung

- be quiet! Dark Rock Pro4 / Pure Rock Slim 2

- Speicher

- 64GB DDR5-5600 G Skill F5-5600J3036D16G / 32 GB DDR4-3200 ECC

- Grafikprozessor

- Raphael IGP / ASpeed AST-2500

- Display

- 27" Samsung LF27T450F

- SSD

- KINGSTON SNVS2000G

- HDD

- - / 8x Seagate IronWolf Pro 20TB

- Optisches Laufwerk

- 1x B.Ray - LG BD-RE BH16NS55

- Soundkarte

- onboard HD?

- Gehäuse

- zu kleines für die GPU

- Netzteil

- be quiet! Pure Power 11 400W / dito

- Tastatur

- CHERRY SECURE BOARD 1.0

- Maus

- Logitech RX250

- Betriebssystem

- Windows 10 19045.4355 / Server 20348.2402

- Webbrowser

- Edge 124.0.2478.51

- Verschiedenes

- U320 SCSI-Controller !!!!

- Internetanbindung

- ▼1000 MBit ▲82 MBit

Crashtest

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 11.11.2008

- Beiträge

- 9.311

- Renomée

- 1.434

- Standort

- Leipzig

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- Collatz, yoyo, radac

- Lieblingsprojekt

- yoyo

- Meine Systeme

- Ryzen: 2x1600, 5x1700, 1x2700,1x3600, 1x5600X; EPYC 7V12 und Kleinzeuch

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Lenovo IdeaPad 5 14ALC05

- Details zu meinem Desktop

- Prozessor

- Ryzen 7950X / Ryzen 4750G

- Mainboard

- ASRock B650M PGRT / X570D4U

- Kühlung

- be quiet! Dark Rock Pro4 / Pure Rock Slim 2

- Speicher

- 64GB DDR5-5600 G Skill F5-5600J3036D16G / 32 GB DDR4-3200 ECC

- Grafikprozessor

- Raphael IGP / ASpeed AST-2500

- Display

- 27" Samsung LF27T450F

- SSD

- KINGSTON SNVS2000G

- HDD

- - / 8x Seagate IronWolf Pro 20TB

- Optisches Laufwerk

- 1x B.Ray - LG BD-RE BH16NS55

- Soundkarte

- onboard HD?

- Gehäuse

- zu kleines für die GPU

- Netzteil

- be quiet! Pure Power 11 400W / dito

- Tastatur

- CHERRY SECURE BOARD 1.0

- Maus

- Logitech RX250

- Betriebssystem

- Windows 10 19045.4355 / Server 20348.2402

- Webbrowser

- Edge 124.0.2478.51

- Verschiedenes

- U320 SCSI-Controller !!!!

- Internetanbindung

- ▼1000 MBit ▲82 MBit

Auch hier hat man diese 'APUs/CPUs' gefunden.

Und zwar scheint Biostar sie auch schon zu kennen.

Computerbase hat nur CPU-World kopiert ...

ps.

die Semprons & Athlons sind CPUs - kein aktivierbarer GPU-Teil, daher vermeide ich APU.

Crashtest

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 11.11.2008

- Beiträge

- 9.311

- Renomée

- 1.434

- Standort

- Leipzig

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- Collatz, yoyo, radac

- Lieblingsprojekt

- yoyo

- Meine Systeme

- Ryzen: 2x1600, 5x1700, 1x2700,1x3600, 1x5600X; EPYC 7V12 und Kleinzeuch

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Lenovo IdeaPad 5 14ALC05

- Details zu meinem Desktop

- Prozessor

- Ryzen 7950X / Ryzen 4750G

- Mainboard

- ASRock B650M PGRT / X570D4U

- Kühlung

- be quiet! Dark Rock Pro4 / Pure Rock Slim 2

- Speicher

- 64GB DDR5-5600 G Skill F5-5600J3036D16G / 32 GB DDR4-3200 ECC

- Grafikprozessor

- Raphael IGP / ASpeed AST-2500

- Display

- 27" Samsung LF27T450F

- SSD

- KINGSTON SNVS2000G

- HDD

- - / 8x Seagate IronWolf Pro 20TB

- Optisches Laufwerk

- 1x B.Ray - LG BD-RE BH16NS55

- Soundkarte

- onboard HD?

- Gehäuse

- zu kleines für die GPU

- Netzteil

- be quiet! Pure Power 11 400W / dito

- Tastatur

- CHERRY SECURE BOARD 1.0

- Maus

- Logitech RX250

- Betriebssystem

- Windows 10 19045.4355 / Server 20348.2402

- Webbrowser

- Edge 124.0.2478.51

- Verschiedenes

- U320 SCSI-Controller !!!!

- Internetanbindung

- ▼1000 MBit ▲82 MBit

Nachtrag :

Nu ist auch bei CPU-World ein Verweis auf diesen Fred:

Nu ist auch bei CPU-World ein Verweis auf diesen Fred:

Update: The first, or one of the first reports regarding existence of Athlon II and Sempron-branded Llano CPUs, was published a month ago by user "Crashtest" in Planet3DNow! forum. According to his report, which is based on information from AMD AGESA code for Llano processors, the socket FM1 platform may potentially utilize large number of family names, based on Athlon and Sempron brands. Full list of family names is provided in the linked thread, and we will only point out a few the most interesting ones: Athlon II X3 4xx, E2-1xxx, Sempron II X3, amd Sempron II X4.

Markus Everson

Grand Admiral Special

die Semprons & Athlons sind CPUs - kein aktivierbarer GPU-Teil

Wie kommt man denn zu so einer Aussage? AMD müßte vom K10 ein weiteres Die für FM1 und mit PCIE-Rootkomplex ableiten um keinen GPU-Teil an Bord zu haben.

Das wäre möglich, ist aber extrem unwahrscheinlich. Die Wahrscheinlichkeit spricht dafür das es sich um kastrierte Llanos handelt - und die wiederum haben einen GPU-Teil. Womit wir bei der Frage sind ob dieser GPU-Teil freischaltbar ist. Diese Frage läßt sich aber vorab nicht klären, AMD hat hier bei den X3 und X2 gezeigt das die einfache Denkweise "damit würden wir Geld verschenken") nicht zwingend die Entscheidung beeinflußt.

Crashtest

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 11.11.2008

- Beiträge

- 9.311

- Renomée

- 1.434

- Standort

- Leipzig

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- Collatz, yoyo, radac

- Lieblingsprojekt

- yoyo

- Meine Systeme

- Ryzen: 2x1600, 5x1700, 1x2700,1x3600, 1x5600X; EPYC 7V12 und Kleinzeuch

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Lenovo IdeaPad 5 14ALC05

- Details zu meinem Desktop

- Prozessor

- Ryzen 7950X / Ryzen 4750G

- Mainboard

- ASRock B650M PGRT / X570D4U

- Kühlung

- be quiet! Dark Rock Pro4 / Pure Rock Slim 2

- Speicher

- 64GB DDR5-5600 G Skill F5-5600J3036D16G / 32 GB DDR4-3200 ECC

- Grafikprozessor

- Raphael IGP / ASpeed AST-2500

- Display

- 27" Samsung LF27T450F

- SSD

- KINGSTON SNVS2000G

- HDD

- - / 8x Seagate IronWolf Pro 20TB

- Optisches Laufwerk

- 1x B.Ray - LG BD-RE BH16NS55

- Soundkarte

- onboard HD?

- Gehäuse

- zu kleines für die GPU

- Netzteil

- be quiet! Pure Power 11 400W / dito

- Tastatur

- CHERRY SECURE BOARD 1.0

- Maus

- Logitech RX250

- Betriebssystem

- Windows 10 19045.4355 / Server 20348.2402

- Webbrowser

- Edge 124.0.2478.51

- Verschiedenes

- U320 SCSI-Controller !!!!

- Internetanbindung

- ▼1000 MBit ▲82 MBit

Freischalten - kann durchaus gehen wenn:

- AMD kein Lasercut gemacht hat

- der GPU-Teil funktioniert !

Ich gehe davon aus dass es entweder teildeaktivierte oder teildefekte Llanos sind:

- ggf. weniger Cache

- ggf. kaputte GPU

Warum sonst sollte es FM1-Boards ohne GPU-Ausgänge geben ?!

- AMD kein Lasercut gemacht hat

- der GPU-Teil funktioniert !

Ich gehe davon aus dass es entweder teildeaktivierte oder teildefekte Llanos sind:

- ggf. weniger Cache

- ggf. kaputte GPU

Warum sonst sollte es FM1-Boards ohne GPU-Ausgänge geben ?!

Markus Everson

Grand Admiral Special

Warum sonst sollte es FM1-Boards ohne GPU-Ausgänge geben ?!

Gibt es? Ok, war mir schon wieder entfallen. Aber wie AMD stehts betont ist die Grafik ja nur ein Nebenkriegsschauplatz im APU-Schlachtfeld.

Crashtest

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 11.11.2008

- Beiträge

- 9.311

- Renomée

- 1.434

- Standort

- Leipzig

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- Collatz, yoyo, radac

- Lieblingsprojekt

- yoyo

- Meine Systeme

- Ryzen: 2x1600, 5x1700, 1x2700,1x3600, 1x5600X; EPYC 7V12 und Kleinzeuch

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Lenovo IdeaPad 5 14ALC05

- Details zu meinem Desktop

- Prozessor

- Ryzen 7950X / Ryzen 4750G

- Mainboard

- ASRock B650M PGRT / X570D4U

- Kühlung

- be quiet! Dark Rock Pro4 / Pure Rock Slim 2

- Speicher

- 64GB DDR5-5600 G Skill F5-5600J3036D16G / 32 GB DDR4-3200 ECC

- Grafikprozessor

- Raphael IGP / ASpeed AST-2500

- Display

- 27" Samsung LF27T450F

- SSD

- KINGSTON SNVS2000G

- HDD

- - / 8x Seagate IronWolf Pro 20TB

- Optisches Laufwerk

- 1x B.Ray - LG BD-RE BH16NS55

- Soundkarte

- onboard HD?

- Gehäuse

- zu kleines für die GPU

- Netzteil

- be quiet! Pure Power 11 400W / dito

- Tastatur

- CHERRY SECURE BOARD 1.0

- Maus

- Logitech RX250

- Betriebssystem

- Windows 10 19045.4355 / Server 20348.2402

- Webbrowser

- Edge 124.0.2478.51

- Verschiedenes

- U320 SCSI-Controller !!!!

- Internetanbindung

- ▼1000 MBit ▲82 MBit

Nu ist es zum Teil ganz offiziel von AMD

AMD hat endlich den Revision Guide der Fam 12 aktualisiert ... http://support.amd.com/us/Processor_TechDocs/44739.pdf

und da steht tatsächlich bei einigen Processor und nicht APU

AMD hat endlich den Revision Guide der Fam 12 aktualisiert ... http://support.amd.com/us/Processor_TechDocs/44739.pdf

und da steht tatsächlich bei einigen Processor und nicht APU

Zuletzt bearbeitet:

ONH

Grand Admiral Special

Ja, hab mich auch gewundert, vor 2 Tagen als ich da mal durchgescrollt habe auf der suche nach einer definiton von AMD was der unterschied E2/A-Series sein soll, aber dann nicht daran gedacht das hier zu posten.

Crashtest

Redaktion

☆☆☆☆☆☆

- Mitglied seit

- 11.11.2008

- Beiträge

- 9.311

- Renomée

- 1.434

- Standort

- Leipzig

- Mitglied der Planet 3DNow! Kavallerie!

- Aktuelle Projekte

- Collatz, yoyo, radac

- Lieblingsprojekt

- yoyo

- Meine Systeme

- Ryzen: 2x1600, 5x1700, 1x2700,1x3600, 1x5600X; EPYC 7V12 und Kleinzeuch

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Lenovo IdeaPad 5 14ALC05

- Details zu meinem Desktop

- Prozessor

- Ryzen 7950X / Ryzen 4750G

- Mainboard

- ASRock B650M PGRT / X570D4U

- Kühlung

- be quiet! Dark Rock Pro4 / Pure Rock Slim 2

- Speicher

- 64GB DDR5-5600 G Skill F5-5600J3036D16G / 32 GB DDR4-3200 ECC

- Grafikprozessor

- Raphael IGP / ASpeed AST-2500

- Display

- 27" Samsung LF27T450F

- SSD

- KINGSTON SNVS2000G

- HDD

- - / 8x Seagate IronWolf Pro 20TB

- Optisches Laufwerk

- 1x B.Ray - LG BD-RE BH16NS55

- Soundkarte

- onboard HD?

- Gehäuse

- zu kleines für die GPU

- Netzteil

- be quiet! Pure Power 11 400W / dito

- Tastatur

- CHERRY SECURE BOARD 1.0

- Maus

- Logitech RX250

- Betriebssystem

- Windows 10 19045.4355 / Server 20348.2402

- Webbrowser

- Edge 124.0.2478.51

- Verschiedenes

- U320 SCSI-Controller !!!!

- Internetanbindung

- ▼1000 MBit ▲82 MBit

So nach langem Suchen etwas AGESA Source-Code

1. Für Sockel FM1:

2. Für Sockel FS1:

1. Für Sockel FM1:

Code:

/* $NoKeywords:$ */

/**

* @file

*

* AMD CPU BrandId related functions and structures.

*

* Contains code that provides CPU BrandId information

*

* @xrefitem bom "File Content Label" "Release Content"

* @e project: AGESA

* @e sub-project: CPU/Family/0x12

* @e \$Revision: 52412 $ @e \$Date: 2011-05-06 08:13:56 +0800 (Fri, 06 May 2011) $

*

*/

/*

******************************************************************************

*

* Copyright (c) 2011, Advanced Micro Devices, Inc.

* All rights reserved.

*

* Redistribution and use in source and binary forms, with or without

* modification, are permitted provided that the following conditions are met:

* * Redistributions of source code must retain the above copyright

* notice, this list of conditions and the following disclaimer.

* * Redistributions in binary form must reproduce the above copyright

* notice, this list of conditions and the following disclaimer in the

* documentation and/or other materials provided with the distribution.

* * Neither the name of Advanced Micro Devices, Inc. nor the names of

* its contributors may be used to endorse or promote products derived

* from this software without specific prior written permission.

*

* THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND

* ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED

* WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE

* DISCLAIMED. IN NO EVENT SHALL ADVANCED MICRO DEVICES, INC. BE LIABLE FOR ANY

* DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES

* (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES;

* LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND

* ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT

* (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS

* SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

******************************************************************************

*/

/*----------------------------------------------------------------------------------------

* M O D U L E S U S E D

*----------------------------------------------------------------------------------------

*/

#include "AGESA.h"

#include "cpuRegisters.h"

#include "cpuEarlyInit.h"

#include "F12PackageType.h"

/*----------------------------------------------------------------------------------------

* D E F I N I T I O N S A N D M A C R O S

*----------------------------------------------------------------------------------------

*/

/*----------------------------------------------------------------------------------------

* T Y P E D E F S A N D S T R U C T U R E S

*----------------------------------------------------------------------------------------

*/

/*----------------------------------------------------------------------------------------

* P R O T O T Y P E S O F L O C A L F U N C T I O N S

*----------------------------------------------------------------------------------------

*/

/*----------------------------------------------------------------------------------------

* E X P O R T E D F U N C T I O N S

*----------------------------------------------------------------------------------------

*/

// String1

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_A4_3[] = "AMD A4-3";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_A4_33[] = "AMD A4-33";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_A4_34[] = "AMD A4-34";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_A6_3[] = "AMD A6-3";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_A6_34[] = "AMD A6-34";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_A6_35[] = "AMD A6-35";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_A6_36[] = "AMD A6-36";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_A8_3[] = "AMD A8-3";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_A8_35[] = "AMD A8-35";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_A8_38[] = "AMD A8-38";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_E2_1[] = "AMD E2-1";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_E2_12[] = "AMD E2-12";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_E2_3[] = "AMD E2-3";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_E2_32[] = "AMD E2-32";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_Athlon_II[] = "AMD Athlon(tm) II ";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_Athlon_II_1[] = "AMD Athlon(tm) II 1";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_Athlon_II_X2[] = "AMD Athlon(tm) II X2 ";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_Athlon_II_X2_2[] = "AMD Athlon(tm) II X2 2";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_Athlon_II_X3[] = "AMD Athlon(tm) II X3 ";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_Athlon_II_X3_3[] = "AMD Athlon(tm) II X3 3";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_Athlon_II_X3_4[] = "AMD Athlon(tm) II X3 4";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_Athlon_II_X4_4[] = "AMD Athlon(tm) II X4 4";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_Athlon_II_X4_6[] = "AMD Athlon(tm) II X4 6";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_Athlon_II_X4[] = "AMD Athlon(tm) II X4 ";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_Athlon_FM1[] = "AMD Athlon(tm) FM1 ";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_Athlon_FM1_X2[] = "AMD Athlon(tm) FM1 X2 ";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_Athlon_FM1_X3[] = "AMD Athlon(tm) FM1 X3 ";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_Athlon_FM1_X4[] = "AMD Athlon(tm) FM1 X4 ";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_Sempron_1[] = "AMD Sempron(tm) 1";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_Sempron_X2_1[] = "AMD Sempron(tm) X2 1";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_Sempron_X2_2[] = "AMD Sempron(tm) X2 2";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_Sempron_II[] = "AMD Sempron(tm) II ";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_Sempron_II_1[] = "AMD Sempron(tm) II 1";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_Sempron_II_X2[] = "AMD Sempron(tm) II X2 ";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_Sempron_II_X2_2[] = "AMD Sempron(tm) II X2 2";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_Sempron_II_X3[] = "AMD Sempron(tm) II X3 ";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_Sempron_II_X3_3[] = "AMD Sempron(tm) II X3 3";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_Sempron_II_X4_4[] = "AMD Sempron(tm) II X4 4";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_Sempron_II_X4[] = "AMD Sempron(tm) II X4 ";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_Sempron_FM1[] = "AMD Sempron(tm) FM1 ";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_Sempron_FM1_X2[] = "AMD Sempron(tm) FM1 X2 ";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_Sempron_FM1_X3[] = "AMD Sempron(tm) FM1 X3 ";

CONST CHAR8 ROMDATA str_F12_Fm1_AMD_Sempron_FM1_X4[] = "AMD Sempron(tm) FM1 X4 ";

// String2

CONST CHAR8 ROMDATA str_F12_Fm1_APU[] = " APU with Radeon(tm) HD Graphics";

CONST CHAR8 ROMDATA str_F12_Fm1_0_APU[] = "0 APU with Radeon(tm) HD Graphics";

CONST CHAR8 ROMDATA str_F12_Fm1_P_APU[] = "P APU with Radeon(tm) HD Graphics";

CONST CHAR8 ROMDATA str_F12_Fm1_0P_APU[] = "0P APU with Radeon(tm) HD Graphics";

CONST CHAR8 ROMDATA str_F12_Fm1_Processor[] = " Processor";

CONST CHAR8 ROMDATA str_F12_Fm1_0_Processor[] = "0 Processor";

CONST CHAR8 ROMDATA str_F12_Fm1_DC_Processor[] = " Dual-Core Processor";

CONST CHAR8 ROMDATA str_F12_Fm1_0_DC_Processor[] = "0 Dual-Core Processor";

CONST CHAR8 ROMDATA str_F12_Fm1_TC_Processor[] = " Triple-Core Processor";

CONST CHAR8 ROMDATA str_F12_Fm1_0_TC_Processor[] = "0 Triple-Core Processor";

CONST CHAR8 ROMDATA str_F12_Fm1_QC_Processor[] = " Quad-Core Processor";

CONST CHAR8 ROMDATA str_F12_Fm1_0_QC_Processor[] = "0 Quad-Core Processor";

/*---------------------------------------------------------------------------------------

* T Y P E D E F S, S T R U C T U R E S, E N U M S

*---------------------------------------------------------------------------------------

*/

CONST AMD_CPU_BRAND ROMDATA CpuF12LnBrandIdString1ArrayFm1[] =

{

// FM1

{1, 0, 1, LN_SOCKET_FM1, str_F12_Fm1_AMD_E2_12, sizeof (str_F12_Fm1_AMD_E2_12)},

{1, 0, 2, LN_SOCKET_FM1, str_F12_Fm1_AMD_Sempron_II_1, sizeof (str_F12_Fm1_AMD_Sempron_II_1)},

{1, 0, 3, LN_SOCKET_FM1, str_F12_Fm1_AMD_Athlon_II_1, sizeof (str_F12_Fm1_AMD_Athlon_II_1)},

{1, 0, 4, LN_SOCKET_FM1, str_F12_Fm1_AMD_E2_1, sizeof (str_F12_Fm1_AMD_E2_1)},

{1, 0, 5, LN_SOCKET_FM1, str_F12_Fm1_AMD_Sempron_II, sizeof (str_F12_Fm1_AMD_Sempron_II)},

{1, 0, 6, LN_SOCKET_FM1, str_F12_Fm1_AMD_Athlon_II, sizeof (str_F12_Fm1_AMD_Athlon_II)},

{1, 0, 7, LN_SOCKET_FM1, str_F12_Fm1_AMD_Sempron_FM1, sizeof (str_F12_Fm1_AMD_Sempron_FM1)},

{1, 0, 8, LN_SOCKET_FM1, str_F12_Fm1_AMD_Athlon_FM1, sizeof (str_F12_Fm1_AMD_Athlon_FM1)},

{1, 0, 9, LN_SOCKET_FM1, str_F12_Fm1_AMD_Sempron_1, sizeof (str_F12_Fm1_AMD_Sempron_1)},

{2, 0, 1, LN_SOCKET_FM1, str_F12_Fm1_AMD_A4_33, sizeof (str_F12_Fm1_AMD_A4_33)},

{2, 0, 2, LN_SOCKET_FM1, str_F12_Fm1_AMD_E2_32, sizeof (str_F12_Fm1_AMD_E2_32)},

{2, 0, 3, LN_SOCKET_FM1, str_F12_Fm1_AMD_Sempron_II_X2_2, sizeof (str_F12_Fm1_AMD_Sempron_II_X2_2)},

{2, 0, 4, LN_SOCKET_FM1, str_F12_Fm1_AMD_Athlon_II_X2_2, sizeof (str_F12_Fm1_AMD_Athlon_II_X2_2)},

{2, 0, 5, LN_SOCKET_FM1, str_F12_Fm1_AMD_A4_34, sizeof (str_F12_Fm1_AMD_A4_34)},

{2, 0, 6, LN_SOCKET_FM1, str_F12_Fm1_AMD_A4_3, sizeof (str_F12_Fm1_AMD_A4_3)},

{2, 0, 7, LN_SOCKET_FM1, str_F12_Fm1_AMD_E2_3, sizeof (str_F12_Fm1_AMD_E2_3)},

{2, 0, 8, LN_SOCKET_FM1, str_F12_Fm1_AMD_Sempron_II_X2, sizeof (str_F12_Fm1_AMD_Sempron_II_X2)},

{2, 0, 9, LN_SOCKET_FM1, str_F12_Fm1_AMD_Athlon_II_X2, sizeof (str_F12_Fm1_AMD_Athlon_II_X2)},

{2, 0, 0xA, LN_SOCKET_FM1, str_F12_Fm1_AMD_Sempron_FM1_X2, sizeof (str_F12_Fm1_AMD_Sempron_FM1_X2)},

{2, 0, 0xB, LN_SOCKET_FM1, str_F12_Fm1_AMD_Athlon_FM1_X2, sizeof (str_F12_Fm1_AMD_Athlon_FM1_X2)},

{2, 0, 0xC, LN_SOCKET_FM1, str_F12_Fm1_AMD_Sempron_X2_1, sizeof (str_F12_Fm1_AMD_Sempron_X2_1)},

{2, 0, 0xD, LN_SOCKET_FM1, str_F12_Fm1_AMD_Sempron_X2_2, sizeof (str_F12_Fm1_AMD_Sempron_X2_2)},

{3, 0, 1, LN_SOCKET_FM1, str_F12_Fm1_AMD_A6_34, sizeof (str_F12_Fm1_AMD_A6_34)},

{3, 0, 2, LN_SOCKET_FM1, str_F12_Fm1_AMD_Sempron_II_X3_3, sizeof (str_F12_Fm1_AMD_Sempron_II_X3_3)},

{3, 0, 3, LN_SOCKET_FM1, str_F12_Fm1_AMD_Athlon_II_X3_3, sizeof (str_F12_Fm1_AMD_Athlon_II_X3_3)},

{3, 0, 4, LN_SOCKET_FM1, str_F12_Fm1_AMD_A6_36, sizeof (str_F12_Fm1_AMD_A6_36)},

{3, 0, 5, LN_SOCKET_FM1, str_F12_Fm1_AMD_A6_35, sizeof (str_F12_Fm1_AMD_A6_35)},

{3, 0, 6, LN_SOCKET_FM1, str_F12_Fm1_AMD_A6_3, sizeof (str_F12_Fm1_AMD_A6_3)},

{3, 0, 7, LN_SOCKET_FM1, str_F12_Fm1_AMD_Sempron_II_X3, sizeof (str_F12_Fm1_AMD_Sempron_II_X3)},

{3, 0, 8, LN_SOCKET_FM1, str_F12_Fm1_AMD_Athlon_II_X3, sizeof (str_F12_Fm1_AMD_Athlon_II_X3)},

{3, 0, 9, LN_SOCKET_FM1, str_F12_Fm1_AMD_Sempron_FM1_X3, sizeof (str_F12_Fm1_AMD_Sempron_FM1_X3)},

{3, 0, 0xA, LN_SOCKET_FM1, str_F12_Fm1_AMD_Athlon_FM1_X3, sizeof (str_F12_Fm1_AMD_Athlon_FM1_X3)},

{3, 0, 0xB, LN_SOCKET_FM1, str_F12_Fm1_AMD_Athlon_II_X3_4, sizeof (str_F12_Fm1_AMD_Athlon_II_X3_4)},

{4, 0, 1, LN_SOCKET_FM1, str_F12_Fm1_AMD_A8_35, sizeof (str_F12_Fm1_AMD_A8_35)},

{4, 0, 2, LN_SOCKET_FM1, str_F12_Fm1_AMD_A6_34, sizeof (str_F12_Fm1_AMD_A6_34)},

{4, 0, 3, LN_SOCKET_FM1, str_F12_Fm1_AMD_Sempron_II_X4_4, sizeof (str_F12_Fm1_AMD_Sempron_II_X4_4)},

{4, 0, 4, LN_SOCKET_FM1, str_F12_Fm1_AMD_Athlon_II_X4_4, sizeof (str_F12_Fm1_AMD_Athlon_II_X4_4)},

{4, 0, 5, LN_SOCKET_FM1, str_F12_Fm1_AMD_A8_38, sizeof (str_F12_Fm1_AMD_A8_38)},

{4, 0, 6, LN_SOCKET_FM1, str_F12_Fm1_AMD_A6_36, sizeof (str_F12_Fm1_AMD_A6_36)},

{4, 0, 7, LN_SOCKET_FM1, str_F12_Fm1_AMD_A8_3, sizeof (str_F12_Fm1_AMD_A8_3)},

{4, 0, 8, LN_SOCKET_FM1, str_F12_Fm1_AMD_A6_3, sizeof (str_F12_Fm1_AMD_A6_3)},

{4, 0, 9, LN_SOCKET_FM1, str_F12_Fm1_AMD_Sempron_II_X4, sizeof (str_F12_Fm1_AMD_Sempron_II_X4)},

{4, 0, 0xA, LN_SOCKET_FM1, str_F12_Fm1_AMD_Athlon_II_X4, sizeof (str_F12_Fm1_AMD_Athlon_II_X4)},

{4, 0, 0xB, LN_SOCKET_FM1, str_F12_Fm1_AMD_Sempron_FM1_X4, sizeof (str_F12_Fm1_AMD_Sempron_FM1_X4)},

{4, 0, 0xC, LN_SOCKET_FM1, str_F12_Fm1_AMD_Athlon_FM1_X4, sizeof (str_F12_Fm1_AMD_Athlon_FM1_X4)},

{4, 0, 0xD, LN_SOCKET_FM1, str_F12_Fm1_AMD_Athlon_II_X4_6, sizeof (str_F12_Fm1_AMD_Athlon_II_X4_6)},

}; //Cores, page, index, socket, stringstart, stringlength

CONST AMD_CPU_BRAND ROMDATA CpuF12LnBrandIdString2ArrayFm1[] =

{

// FM1

{1, 0, 1, LN_SOCKET_FM1, str_F12_Fm1_APU, sizeof (str_F12_Fm1_APU)},

{1, 0, 2, LN_SOCKET_FM1, str_F12_Fm1_Processor, sizeof (str_F12_Fm1_Processor)},

{1, 0, 3, LN_SOCKET_FM1, str_F12_Fm1_P_APU, sizeof (str_F12_Fm1_P_APU)},

{1, 0, 4, LN_SOCKET_FM1, str_F12_Fm1_0_APU, sizeof (str_F12_Fm1_0_APU)},

{1, 0, 5, LN_SOCKET_FM1, str_F12_Fm1_0P_APU, sizeof (str_F12_Fm1_0P_APU)},

{1, 0, 6, LN_SOCKET_FM1, str_F12_Fm1_0_Processor, sizeof (str_F12_Fm1_0_Processor)},

{2, 0, 1, LN_SOCKET_FM1, str_F12_Fm1_APU, sizeof (str_F12_Fm1_APU)},

{2, 0, 2, LN_SOCKET_FM1, str_F12_Fm1_DC_Processor, sizeof (str_F12_Fm1_DC_Processor)},

{2, 0, 3, LN_SOCKET_FM1, str_F12_Fm1_P_APU, sizeof (str_F12_Fm1_P_APU)},

{2, 0, 4, LN_SOCKET_FM1, str_F12_Fm1_0_APU, sizeof (str_F12_Fm1_0_APU)},

{2, 0, 5, LN_SOCKET_FM1, str_F12_Fm1_0P_APU, sizeof (str_F12_Fm1_0P_APU)},

{2, 0, 6, LN_SOCKET_FM1, str_F12_Fm1_0_DC_Processor, sizeof (str_F12_Fm1_0_DC_Processor)},

{3, 0, 1, LN_SOCKET_FM1, str_F12_Fm1_APU, sizeof (str_F12_Fm1_APU)},

{3, 0, 2, LN_SOCKET_FM1, str_F12_Fm1_P_APU, sizeof (str_F12_Fm1_P_APU)},

{3, 0, 3, LN_SOCKET_FM1, str_F12_Fm1_TC_Processor, sizeof (str_F12_Fm1_TC_Processor)},

{3, 0, 4, LN_SOCKET_FM1, str_F12_Fm1_0_APU, sizeof (str_F12_Fm1_0_APU)},

{3, 0, 5, LN_SOCKET_FM1, str_F12_Fm1_0P_APU, sizeof (str_F12_Fm1_0P_APU)},

{3, 0, 6, LN_SOCKET_FM1, str_F12_Fm1_0_TC_Processor, sizeof (str_F12_Fm1_0_TC_Processor)},

{4, 0, 1, LN_SOCKET_FM1, str_F12_Fm1_APU, sizeof (str_F12_Fm1_APU)},

{4, 0, 2, LN_SOCKET_FM1, str_F12_Fm1_P_APU, sizeof (str_F12_Fm1_P_APU)},

{4, 0, 3, LN_SOCKET_FM1, str_F12_Fm1_QC_Processor, sizeof (str_F12_Fm1_QC_Processor)},

{4, 0, 4, LN_SOCKET_FM1, str_F12_Fm1_0_APU, sizeof (str_F12_Fm1_0_APU)},

{4, 0, 5, LN_SOCKET_FM1, str_F12_Fm1_0P_APU, sizeof (str_F12_Fm1_0P_APU)},

{4, 0, 6, LN_SOCKET_FM1, str_F12_Fm1_0_QC_Processor, sizeof (str_F12_Fm1_0_QC_Processor)},

}; //Cores, page, index, socket, stringstart, stringlength

CONST CPU_BRAND_TABLE ROMDATA F12LnBrandIdString1ArrayFm1 = {

(sizeof (CpuF12LnBrandIdString1ArrayFm1) / sizeof (AMD_CPU_BRAND)),

CpuF12LnBrandIdString1ArrayFm1

};

CONST CPU_BRAND_TABLE ROMDATA F12LnBrandIdString2ArrayFm1 = {

(sizeof (CpuF12LnBrandIdString2ArrayFm1) / sizeof (AMD_CPU_BRAND)),

CpuF12LnBrandIdString2ArrayFm1

};2. Für Sockel FS1:

Code:

/* $NoKeywords:$ */

/**

* @file

*

* AMD CPU BrandId related functions and structures.

*

* Contains code that provides CPU BrandId information

*

* @xrefitem bom "File Content Label" "Release Content"

* @e project: AGESA

* @e sub-project: CPU/Family/0x12

* @e \$Revision: 46474 $ @e \$Date: 2011-02-03 05:46:17 +0800 (Thu, 03 Feb 2011) $

*

*/

/*

******************************************************************************

*

* Copyright (c) 2011, Advanced Micro Devices, Inc.

* All rights reserved.

*

* Redistribution and use in source and binary forms, with or without

* modification, are permitted provided that the following conditions are met:

* * Redistributions of source code must retain the above copyright

* notice, this list of conditions and the following disclaimer.

* * Redistributions in binary form must reproduce the above copyright

* notice, this list of conditions and the following disclaimer in the

* documentation and/or other materials provided with the distribution.

* * Neither the name of Advanced Micro Devices, Inc. nor the names of

* its contributors may be used to endorse or promote products derived

* from this software without specific prior written permission.

*

* THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS "AS IS" AND

* ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED

* WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE ARE

* DISCLAIMED. IN NO EVENT SHALL ADVANCED MICRO DEVICES, INC. BE LIABLE FOR ANY

* DIRECT, INDIRECT, INCIDENTAL, SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES

* (INCLUDING, BUT NOT LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES;

* LOSS OF USE, DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND

* ON ANY THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT

* (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE OF THIS

* SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

******************************************************************************

*/

/*----------------------------------------------------------------------------------------

* M O D U L E S U S E D

*----------------------------------------------------------------------------------------

*/

#include "AGESA.h"

#include "cpuRegisters.h"

#include "cpuEarlyInit.h"

#include "F12PackageType.h"

/*----------------------------------------------------------------------------------------

* D E F I N I T I O N S A N D M A C R O S

*----------------------------------------------------------------------------------------

*/

/*----------------------------------------------------------------------------------------

* T Y P E D E F S A N D S T R U C T U R E S

*----------------------------------------------------------------------------------------

*/

/*----------------------------------------------------------------------------------------

* P R O T O T Y P E S O F L O C A L F U N C T I O N S

*----------------------------------------------------------------------------------------

*/

/*----------------------------------------------------------------------------------------

* E X P O R T E D F U N C T I O N S

*----------------------------------------------------------------------------------------

*/

// String1

CONST CHAR8 ROMDATA str_F12_Fs1_AMD_A4_35[] = "AMD A4-35";

CONST CHAR8 ROMDATA str_F12_Fs1_AMD_A4_34[] = "AMD A4-34";

CONST CHAR8 ROMDATA str_F12_Fs1_AMD_A4_33[] = "AMD A4-33";

CONST CHAR8 ROMDATA str_F12_Fs1_AMD_A4_32[] = "AMD A4-32";

CONST CHAR8 ROMDATA str_F12_Fs1_AMD_E2_30[] = "AMD E2-30";

CONST CHAR8 ROMDATA str_F12_Fs1_AMD_E2_20[] = "AMD E2-20";

CONST CHAR8 ROMDATA str_F12_Fs1_AMD_E2_10[] = "AMD E2-10";

CONST CHAR8 ROMDATA str_F12_Fs1_AMD_A8_35[] = "AMD A8-35";

CONST CHAR8 ROMDATA str_F12_Fs1_AMD_A8_34[] = "AMD A8-34";

CONST CHAR8 ROMDATA str_F12_Fs1_AMD_A6_34[] = "AMD A6-34";

CONST CHAR8 ROMDATA str_F12_Fs1_AMD_A6_33[] = "AMD A6-33";

// String2

CONST CHAR8 ROMDATA str_F12_Fs1_M_APU[] = "M APU with Radeon(tm) HD Graphics";

CONST CHAR8 ROMDATA str_F12_Fs1_MX_APU[] = "MX APU with Radeon(tm) HD Graphics";

CONST CHAR8 ROMDATA str_F12_Fs1_ML_APU[] = "ML APU with Radeon(tm) HD Graphics";

CONST CHAR8 ROMDATA str_F12_Fs1_MZ_APU[] = "MZ APU with Radeon(tm) HD Graphics";

CONST CHAR8 ROMDATA str_F12_Fs1_MC_APU[] = "MC APU with Radeon(tm) HD Graphics";

CONST CHAR8 ROMDATA str_F12_Fs1_MF_Processor[] = "MF Processor";

CONST CHAR8 ROMDATA str_F12_Fs1_MG_Processor[] = "MG Processor";

CONST CHAR8 ROMDATA str_F12_Fs1_MF_DC_Processor[] = "MF Dual-Core Processor";

CONST CHAR8 ROMDATA str_F12_Fs1_MG_DC_Processor[] = "MG Dual-Core Processor";

CONST CHAR8 ROMDATA str_F12_Fs1_MF_TC_Processor[] = "MF Triple-Core Processor";

CONST CHAR8 ROMDATA str_F12_Fs1_MG_TC_Processor[] = "MG Triple-Core Processor";

CONST CHAR8 ROMDATA str_F12_Fs1_MF_QC_Processor[] = "MF Quad-Core Processor";

CONST CHAR8 ROMDATA str_F12_Fs1_MG_QC_Processor[] = "MG Quad-Core Processor";

/*---------------------------------------------------------------------------------------

* T Y P E D E F S, S T R U C T U R E S, E N U M S

*---------------------------------------------------------------------------------------

*/

CONST AMD_CPU_BRAND ROMDATA CpuF12LnBrandIdString1ArrayFs1[] =

{

// FS1

{1, 0, 1, LN_SOCKET_FS1, str_F12_Fs1_AMD_A4_35, sizeof (str_F12_Fs1_AMD_A4_35)},

{2, 0, 1, LN_SOCKET_FS1, str_F12_Fs1_AMD_A4_35, sizeof (str_F12_Fs1_AMD_A4_35)},

{1, 0, 2, LN_SOCKET_FS1, str_F12_Fs1_AMD_A4_34, sizeof (str_F12_Fs1_AMD_A4_34)},

{2, 0, 2, LN_SOCKET_FS1, str_F12_Fs1_AMD_A4_34, sizeof (str_F12_Fs1_AMD_A4_34)},

{1, 0, 3, LN_SOCKET_FS1, str_F12_Fs1_AMD_A4_33, sizeof (str_F12_Fs1_AMD_A4_33)},

{2, 0, 3, LN_SOCKET_FS1, str_F12_Fs1_AMD_A4_33, sizeof (str_F12_Fs1_AMD_A4_33)},

{1, 0, 4, LN_SOCKET_FS1, str_F12_Fs1_AMD_A4_32, sizeof (str_F12_Fs1_AMD_A4_32)},

{2, 0, 4, LN_SOCKET_FS1, str_F12_Fs1_AMD_A4_32, sizeof (str_F12_Fs1_AMD_A4_32)},

{1, 0, 5, LN_SOCKET_FS1, str_F12_Fs1_AMD_E2_30, sizeof (str_F12_Fs1_AMD_E2_30)},

{2, 0, 5, LN_SOCKET_FS1, str_F12_Fs1_AMD_E2_30, sizeof (str_F12_Fs1_AMD_E2_30)},

{1, 0, 6, LN_SOCKET_FS1, str_F12_Fs1_AMD_E2_20, sizeof (str_F12_Fs1_AMD_E2_20)},

{2, 0, 6, LN_SOCKET_FS1, str_F12_Fs1_AMD_E2_20, sizeof (str_F12_Fs1_AMD_E2_20)},

{1, 0, 7, LN_SOCKET_FS1, str_F12_Fs1_AMD_E2_10, sizeof (str_F12_Fs1_AMD_E2_10)},

{2, 0, 7, LN_SOCKET_FS1, str_F12_Fs1_AMD_E2_10, sizeof (str_F12_Fs1_AMD_E2_10)},

{3, 0, 1, LN_SOCKET_FS1, str_F12_Fs1_AMD_A8_35, sizeof (str_F12_Fs1_AMD_A8_35)},

{4, 0, 1, LN_SOCKET_FS1, str_F12_Fs1_AMD_A8_35, sizeof (str_F12_Fs1_AMD_A8_35)},

{3, 0, 2, LN_SOCKET_FS1, str_F12_Fs1_AMD_A8_34, sizeof (str_F12_Fs1_AMD_A8_34)},

{4, 0, 2, LN_SOCKET_FS1, str_F12_Fs1_AMD_A8_34, sizeof (str_F12_Fs1_AMD_A8_34)},

{3, 0, 3, LN_SOCKET_FS1, str_F12_Fs1_AMD_A6_34, sizeof (str_F12_Fs1_AMD_A6_34)},

{4, 0, 3, LN_SOCKET_FS1, str_F12_Fs1_AMD_A6_34, sizeof (str_F12_Fs1_AMD_A6_34)},

{3, 0, 4, LN_SOCKET_FS1, str_F12_Fs1_AMD_A6_33, sizeof (str_F12_Fs1_AMD_A6_33)},

{4, 0, 4, LN_SOCKET_FS1, str_F12_Fs1_AMD_A6_33, sizeof (str_F12_Fs1_AMD_A6_33)},

}; //Cores, page, index, socket, stringstart, stringlength

CONST AMD_CPU_BRAND ROMDATA CpuF12LnBrandIdString2ArrayFs1[] =

{

// FS1

{1, 0, 1, LN_SOCKET_FS1, str_F12_Fs1_M_APU, sizeof (str_F12_Fs1_M_APU)},

{2, 0, 1, LN_SOCKET_FS1, str_F12_Fs1_M_APU, sizeof (str_F12_Fs1_M_APU)},

{3, 0, 1, LN_SOCKET_FS1, str_F12_Fs1_M_APU, sizeof (str_F12_Fs1_M_APU)},

{4, 0, 1, LN_SOCKET_FS1, str_F12_Fs1_M_APU, sizeof (str_F12_Fs1_M_APU)},

{1, 0, 2, LN_SOCKET_FS1, str_F12_Fs1_MX_APU, sizeof (str_F12_Fs1_MX_APU)},

{2, 0, 2, LN_SOCKET_FS1, str_F12_Fs1_MX_APU, sizeof (str_F12_Fs1_MX_APU)},

{3, 0, 2, LN_SOCKET_FS1, str_F12_Fs1_MX_APU, sizeof (str_F12_Fs1_MX_APU)},

{4, 0, 2, LN_SOCKET_FS1, str_F12_Fs1_MX_APU, sizeof (str_F12_Fs1_MX_APU)},

{1, 0, 3, LN_SOCKET_FS1, str_F12_Fs1_ML_APU, sizeof (str_F12_Fs1_ML_APU)},

{2, 0, 3, LN_SOCKET_FS1, str_F12_Fs1_ML_APU, sizeof (str_F12_Fs1_ML_APU)},

{3, 0, 3, LN_SOCKET_FS1, str_F12_Fs1_ML_APU, sizeof (str_F12_Fs1_ML_APU)},

{4, 0, 3, LN_SOCKET_FS1, str_F12_Fs1_ML_APU, sizeof (str_F12_Fs1_ML_APU)},

{1, 0, 4, LN_SOCKET_FS1, str_F12_Fs1_MZ_APU, sizeof (str_F12_Fs1_MZ_APU)},

{2, 0, 4, LN_SOCKET_FS1, str_F12_Fs1_MZ_APU, sizeof (str_F12_Fs1_MZ_APU)},

{3, 0, 4, LN_SOCKET_FS1, str_F12_Fs1_MZ_APU, sizeof (str_F12_Fs1_MZ_APU)},

{4, 0, 4, LN_SOCKET_FS1, str_F12_Fs1_MZ_APU, sizeof (str_F12_Fs1_MZ_APU)},

{1, 0, 5, LN_SOCKET_FS1, str_F12_Fs1_MC_APU, sizeof (str_F12_Fs1_MC_APU)},

{2, 0, 5, LN_SOCKET_FS1, str_F12_Fs1_MC_APU, sizeof (str_F12_Fs1_MC_APU)},

{3, 0, 5, LN_SOCKET_FS1, str_F12_Fs1_MC_APU, sizeof (str_F12_Fs1_MC_APU)},

{4, 0, 5, LN_SOCKET_FS1, str_F12_Fs1_MC_APU, sizeof (str_F12_Fs1_MC_APU)},

{1, 0, 6, LN_SOCKET_FS1, str_F12_Fs1_MF_Processor, sizeof (str_F12_Fs1_MF_Processor)},

{1, 0, 7, LN_SOCKET_FS1, str_F12_Fs1_MG_Processor, sizeof (str_F12_Fs1_MG_Processor)},

{2, 0, 6, LN_SOCKET_FS1, str_F12_Fs1_MF_DC_Processor, sizeof (str_F12_Fs1_MF_DC_Processor)},

{2, 0, 7, LN_SOCKET_FS1, str_F12_Fs1_MG_DC_Processor, sizeof (str_F12_Fs1_MG_DC_Processor)},

{3, 0, 6, LN_SOCKET_FS1, str_F12_Fs1_MF_TC_Processor, sizeof (str_F12_Fs1_MF_TC_Processor)},

{3, 0, 7, LN_SOCKET_FS1, str_F12_Fs1_MG_TC_Processor, sizeof (str_F12_Fs1_MG_TC_Processor)},

{4, 0, 6, LN_SOCKET_FS1, str_F12_Fs1_MF_QC_Processor, sizeof (str_F12_Fs1_MF_QC_Processor)},

{4, 0, 7, LN_SOCKET_FS1, str_F12_Fs1_MG_QC_Processor, sizeof (str_F12_Fs1_MG_QC_Processor)},

}; //Cores, page, index, socket, stringstart, stringlength

CONST CPU_BRAND_TABLE ROMDATA F12LnBrandIdString1ArrayFs1 = {

(sizeof (CpuF12LnBrandIdString1ArrayFs1) / sizeof (AMD_CPU_BRAND)),

CpuF12LnBrandIdString1ArrayFs1

};

CONST CPU_BRAND_TABLE ROMDATA F12LnBrandIdString2ArrayFs1 = {

(sizeof (CpuF12LnBrandIdString2ArrayFs1) / sizeof (AMD_CPU_BRAND)),

CpuF12LnBrandIdString2ArrayFs1

};Ähnliche Themen

- Antworten

- 76

- Aufrufe

- 6K

- Antworten

- 15

- Aufrufe

- 824

- Antworten

- 824

- Aufrufe

- 58K

- Antworten

- 0

- Aufrufe

- 411