App installieren

How to install the app on iOS

Follow along with the video below to see how to install our site as a web app on your home screen.

Anmerkung: This feature may not be available in some browsers.

Du verwendest einen veralteten Browser. Es ist möglich, dass diese oder andere Websites nicht korrekt angezeigt werden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Du solltest ein Upgrade durchführen oder ein alternativer Browser verwenden.

Prognose-Board: Wie geht es bei AMD weiter? Entwicklungen / Strategien / Maßnahmen, die AMD betreffen bzw. die AMD treffen könnte

- Ersteller BavarianRealist

- Erstellt am

- Mitglied seit

- 16.10.2000

- Beiträge

- 24.371

- Renomée

- 9.696

- Standort

- East Fishkill, Minga, Xanten

- Aktuelle Projekte

- Je nach Gusto

- Meine Systeme

- Ryzen 9 5900X, Ryzen 7 3700X

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Samsung P35 (16 Jahre alt ;) )

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5900X

- Mainboard

- ASRock B550

- Speicher

- 2x 16 GB DDR4 3200

- Grafikprozessor

- GeForce GTX 1650

- Display

- 27 Zoll Acer + 24 Zoll DELL

- SSD

- Samsung 980 Pro 256 GB

- HDD

- diverse

- Soundkarte

- Onboard

- Gehäuse

- Fractal Design R5

- Netzteil

- be quiet! Straight Power 10 CM 500W

- Tastatur

- Logitech Cordless Desktop

- Maus

- Logitech G502

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox, Vivaldi

- Internetanbindung

- ▼250 MBit ▲40 MBit

AMD Working to Bring CXL Memory Tech to Future Consumer CPUs

AMD's Meet the Experts reveals a work in progress.

So you'll find over the next, you know, three to five years, you'll see it first in the server area, but you'll find moving down into the client [consumer] area, ways that we can make sure that memory and storage can communicate on the same bus through CXL.

Also frühestens was für Zen 6.

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Spannende Zahlen und Ausblick im Servermarkt: https://www.semianalysis.com/p/2023-datacenter-outlook-amd-and-intel

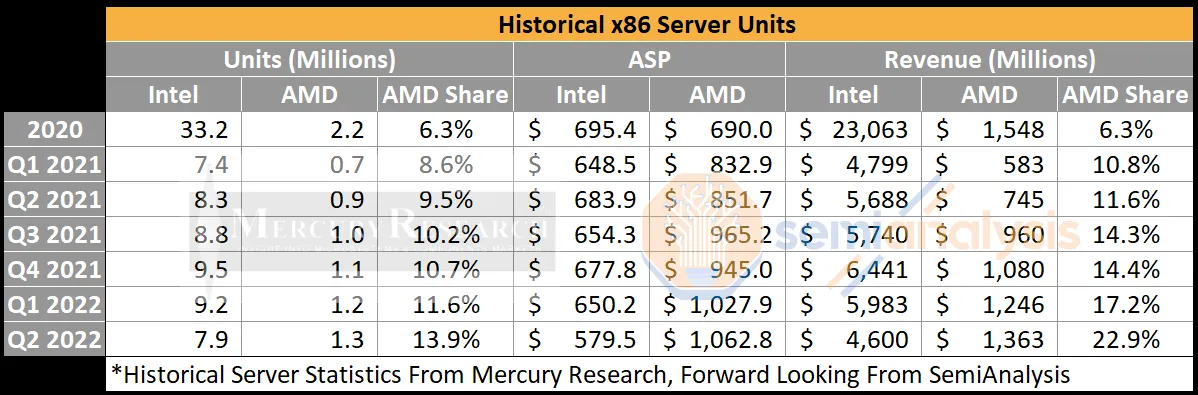

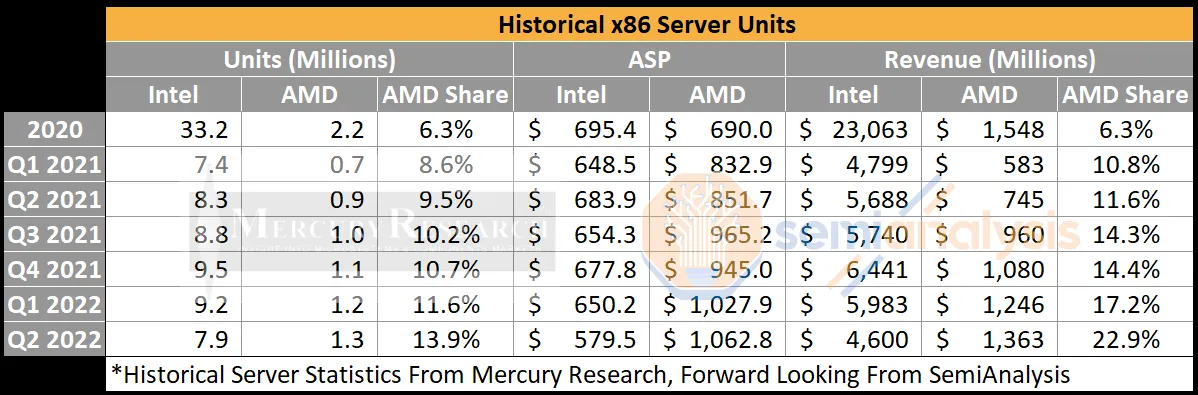

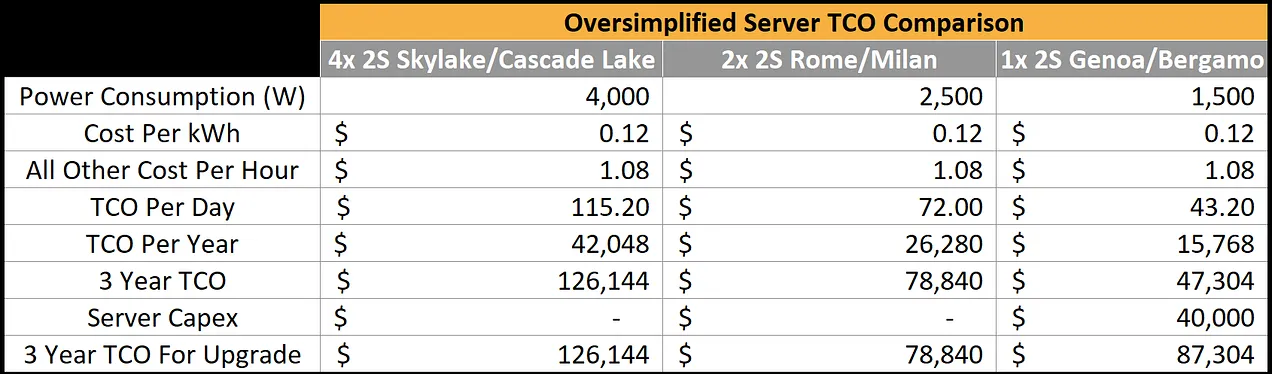

Die Betrachtung der TCO in der Folge zeigt wo der Zug hinfährt und eigentlich auch nicht mehr aufzuhalten ist. Das wird wohl Ende 2023 zu so etwas wie einem Dammbruch kommen bei Intel:In 2 years, AMD more than doubled its market share. Going forward, we expect AMD’s share of x86 server units to increase from 13.9% in Q2 2022 to 21.2% in Q4 2023.

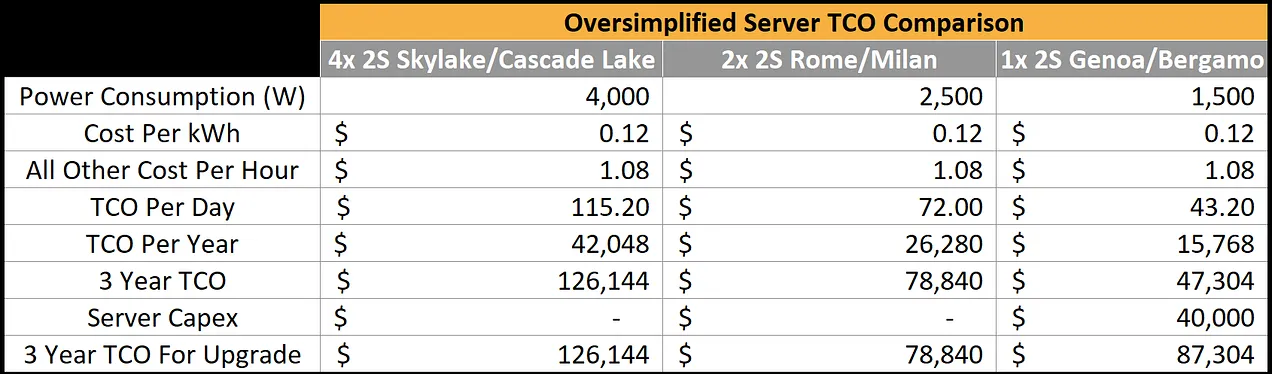

Genoa marks a big shift in TCO that makes it sensible to replace aging servers. 2S (socket) Genoa offers 4x the general-purpose performance at significantly better TCO versus 2S Skylake/Cascade Lake SP server. Initial capital expenditures for Genoa-based servers are considerably higher due to the cost of higher costs of the CPU, DDR5, and PCIe 5.0. Despite this big cost jump, Genoa and Bergamo-based servers will pay for themselves many times over versus keeping already depreciated servers deployed.

Under this oversimplified model, upgrading to a 2-socket Genoa-based server from 4 existing 2-socket Skylake/Cascade Lake-based servers (2 CPUs vs 8 CPUs) is a net present value positive transaction. The payback period for Capex spent is roughly ~18 months. The payback period for a Rome/Milan server upgrade would still be ~4 years. The improvements are even more significant when you start considering new features related to security, CXL, and AVX512.

Moving on to our incremental quarterly ramp for Zen 4-based server platforms, followed by the Q4 2022 and 2023 quarterly units, ASP, and revenue for Intel and AMD. The ramp starts slow, but picks up in Q1 2023 to 100,000 incremental quarterly units. This accelerates into the latter half of 2023 as AMD ramps down existing platforms and allocates more backend substrate supply from Rome/Milan to Genoa/Bergamo/Siena.

- Mitglied seit

- 16.10.2000

- Beiträge

- 24.371

- Renomée

- 9.696

- Standort

- East Fishkill, Minga, Xanten

- Aktuelle Projekte

- Je nach Gusto

- Meine Systeme

- Ryzen 9 5900X, Ryzen 7 3700X

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Samsung P35 (16 Jahre alt ;) )

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5900X

- Mainboard

- ASRock B550

- Speicher

- 2x 16 GB DDR4 3200

- Grafikprozessor

- GeForce GTX 1650

- Display

- 27 Zoll Acer + 24 Zoll DELL

- SSD

- Samsung 980 Pro 256 GB

- HDD

- diverse

- Soundkarte

- Onboard

- Gehäuse

- Fractal Design R5

- Netzteil

- be quiet! Straight Power 10 CM 500W

- Tastatur

- Logitech Cordless Desktop

- Maus

- Logitech G502

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox, Vivaldi

- Internetanbindung

- ▼250 MBit ▲40 MBit

Going forward, we expect AMD’s share of x86 server units to increase from 13.9% in Q2 2022 to 21.2% in Q4 2023.

Die Units sind ja gut und schön, aber das Eklatante sind ja die ASP und die Umsatzverteilung.

Für das dritte Quartal wird der Anteil von AMD da auch schon mit den bislang bekannten Zahlen etwa von 22,9% auf 25,6% steigen.

Wenn man sich die TCO von Genoa/Bergamo so anschaut, sehe ich AMD selbst in einem schrumpfenden Markt gut aufgestellt und die 21.2% Unitsanteil in Q4 2023 könnten sogar noch konservativ geschätzt sein.

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Das ist im Prinzip ein Selbstläufer für AMD in 2023 - wer investiert denn nicht, wenn in 3 Jahren mehr Geld übrig ist und das mitten in der Krise. Ich denke AMD wird hier 5nm Wafer dazu bestellen wenn Q1/2023 mal gelaufen ist. Selbst die Ablösung Rome/Milan sollte trotz DDR5 Kosten Ende 2023 attraktiv werden. Man wird auch sehen ob die 12 cent/kWh noch Bestand haben bis dahin - jeder Cent nach oben verbessert die Kaufargumentation.

Zuletzt bearbeitet:

Absatzprobleme: TSMCs Kunden kürzen Aufträge in größerem Umfang

Auftragsfertiger TSMC bekommt die Absatzschwierigkeiten seiner Kunden deutlicher zu spüren, denn sie sollen ihre Aufträge kürzen.

- Mitglied seit

- 16.10.2000

- Beiträge

- 24.371

- Renomée

- 9.696

- Standort

- East Fishkill, Minga, Xanten

- Aktuelle Projekte

- Je nach Gusto

- Meine Systeme

- Ryzen 9 5900X, Ryzen 7 3700X

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Samsung P35 (16 Jahre alt ;) )

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5900X

- Mainboard

- ASRock B550

- Speicher

- 2x 16 GB DDR4 3200

- Grafikprozessor

- GeForce GTX 1650

- Display

- 27 Zoll Acer + 24 Zoll DELL

- SSD

- Samsung 980 Pro 256 GB

- HDD

- diverse

- Soundkarte

- Onboard

- Gehäuse

- Fractal Design R5

- Netzteil

- be quiet! Straight Power 10 CM 500W

- Tastatur

- Logitech Cordless Desktop

- Maus

- Logitech G502

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox, Vivaldi

- Internetanbindung

- ▼250 MBit ▲40 MBit

Absatzprobleme: TSMCs Kunden kürzen Aufträge in größerem Umfang

Auftragsfertiger TSMC bekommt die Absatzschwierigkeiten seiner Kunden deutlicher zu spüren, denn sie sollen ihre Aufträge kürzen.www.computerbase.de

Ist allerdings sehr unspezifisch. Wir sollten mal schauen, ob nicht langsam irgendjemand gegensteuern wird über den Endpreis.

Raptor Lake ist ja günstiger geworden, als ich eigentlich erwartet hatte. Oder die Meldungen von Intels Preiserhöhungen waren alle Käse.

Mal schauen was AMD dann im GPU-Bereich macht. Vielleicht wirds durch MCM ja günstiger zu produzieren und man versucht was über den Preis.

Da hätte man ja dann darüber noch Wachstumspotential.

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Schon im Juli gab es Meldungen der gleichen Art, die bezogen sich auf 6/7nm, hatten aber auch mit dem geplanten Transit zu 5nm zu tun. Ich bin mir auch nicht sicher, ob das nicht nur Reduzierungen der Wafer ist, die Anfang des Jahres von TSMC sozusagen meistbietend versteigert wurde. Gut möglich, dass sich da einfach jeder auch den letzten Wafer sichern wollte. Diese Order mit Aufpreis könnten hier ebenfalls die gemeinten sein. Was man so liest ist, dass AMD im Gegensatz zu Nvidia da etwas flexibler agieren kann, als . Nvidia hatte Aufschub ins Q1/2023 bekommen. AMD gilt neben MediaTek und Apple als "preferred customer" bei TSMC. Siehe https://www.heise.de/news/AMD-Apple...den-bestellen-wohl-weniger-Wafer-7160187.html

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

So wie es scheint wird der Zen4-Threadripper ebenfalls nur noch in der PRO-Variante an OEMs gehen. Die Threadripper nutzen dertzeit Workstation Mainboard/Sockel WRX80 (Identisch zu SP3) - möglich, dass AMD den OEMs ermöglicht den selben Sockel für beides zu nutzen und entsprechend zu konfigurieren. Dann würde Zen4 Threadripper möglicherweise offiziell mit SP5 (oder einem Namen ähnlich sWRX12 für 12 Speicherkanäle)

Siehe: https://en.wikichip.org/wiki/amd/packages/socket_swrx8#Package_Description

Allerdings kam mir gerade der Gedanke ob AMD sich auch darauf vorbereitet ein oder 2 TR in Retail mit 32 Kernen für AM5 zu releasen, für all jene denen die Anzahl der PCIe lanes und Speicherkanäle nicht so wichtig sind, aber eben mehr als 16 Kerne und hoher Takt ihre Workloads unterstützen. Da ergibt sich ja eine Lücke die Intel nutzen kann um ihr Retail-HEDT wieder zu etablieren mit Sapphire Rapids.

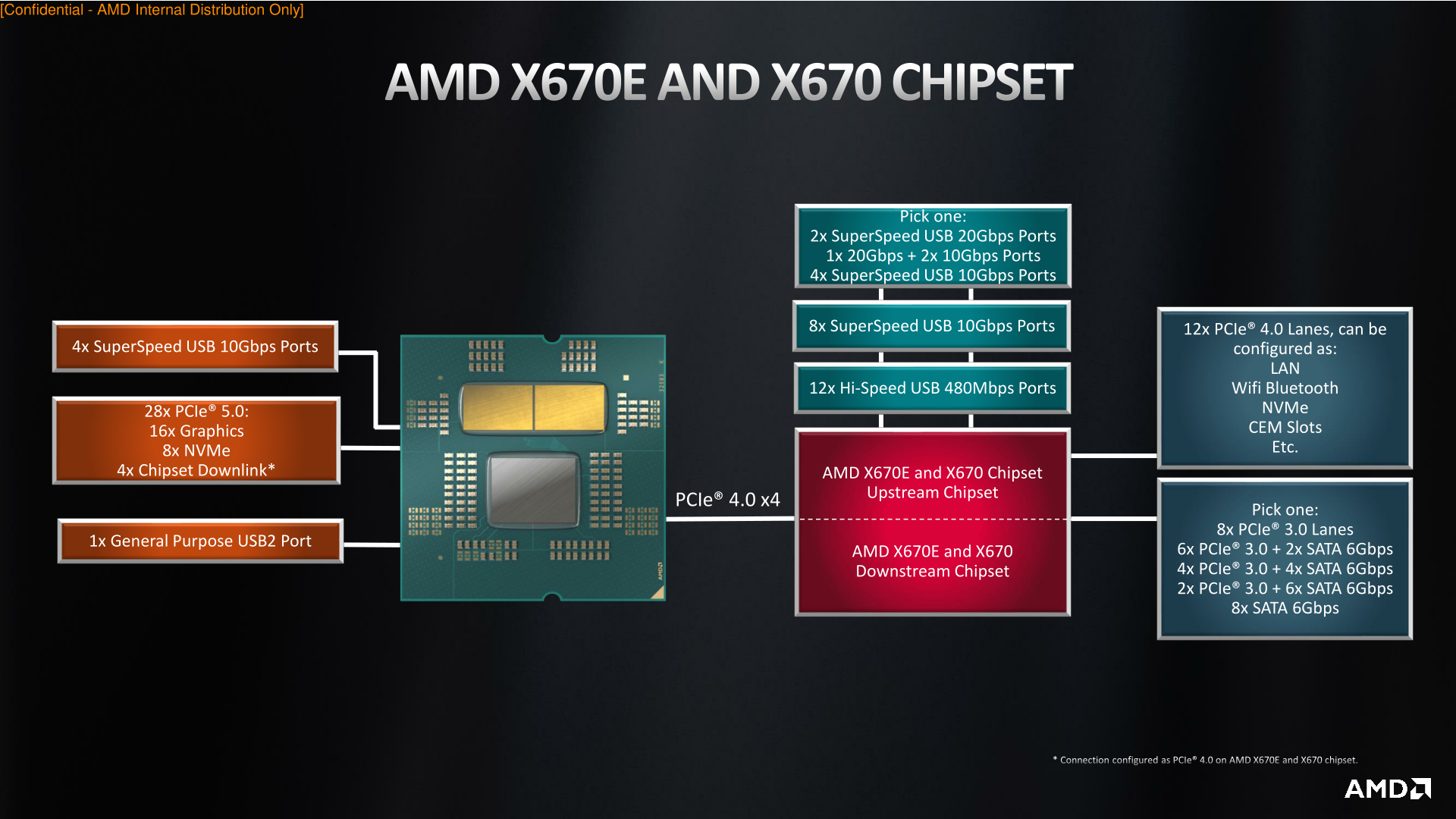

Plant AMD TR auf AM5 und hat deshalb den X670E Chipsatz überhaupt im Programm für AM5?

Folgende Indikatoren warfen bei mir die Frage auf:

Hier fängt für mich die erste Merkwürdigkeit an: die Chipsatz Anbindung ist als PCIe 4.0 konfiguriert. Warum? Und kann das auch als PCIe 5.0 konfiguriert werden?

Dann gibt es Boards für 1.600,-€ wie dieses hier: https://forum.planet3dnow.de/index.php?mbdb/mainboards/msi-meg-x670e-godlike.1049/

Mit Multi GPU Support - Warum?

Sind das Vorbereitungen um einen 32-Kerner auf AM5 nachzuschieben als Dualchannel Konkurrenz zu Intels Alder Lake-S auf W680, der ja ebenfalls als Dualchannel kommen soll?

AMD würde ja eine ganze Plattform damit einsparen und den AM5 nochmals aufwerten zeitgleich, doch ist das möglich dass da so ein Bluff gefahren wird? Damit würde eine eigene HEDT-Plattform von Intel mit erscheinen schon EOL werden, zumindest als Retail.

Dazu passt auch das relativ frühe erscheinen der Threadripper in Q1/2023 - weniger Arbeit für eine eigene Plattform, SP5-Boards mit Epyc und TR bestückbar, AM5 mit AGESA Update mit TR nutzbar um die Lücken zu Workstation zu schließen.

Irgendwie ergeben für mich nur auf diese Weise die Chipsatzeinteilungen - vor allem der 670E, einen Sinn. Denn ich wüsste nicht warum man sonst so viele Chipsatz-Varianten benötigen würde.

Siehe: https://en.wikichip.org/wiki/amd/packages/socket_swrx8#Package_Description

Ich denke AMD geht da ein Problem an, das sie mit dem Software-Ökosystem haben. Die OEMs übernehmen das und HEDT verschwindet aus dem Retail-Markt. Derzeit ist Lenovo ja nach wie vor exklusiver Partner für die TR 5000 SKUs.However all sockets SP3, TR4, sTRX4, and sWRX8, and all processors for these sockets have the same keying. It is worth noting that these processors are also electrically keyed by pin SP3R1 and SP3R2. To boot the processor the motherboard must also provide compatible firmware. A triangular symbol on both sides of the substrate marks the location of pin A1, with corresponding markings on the socket. Decoupling capacitors are placed under the lid around the chiplets on the top side, and in two windows in the pad grid on the bottom side.

sWRX8 is a multi-chip package integrating one central I/O die and 4, 6, or 8 identical Core Complex Dies which contain eight CPU cores each. This silicon is "Starship" rev. SSP-B0 (CPU Family 17h) and "Genesis" GN-B1 (19h). AMD used the same chips for second and third generation EPYC server and embedded processors, and Ryzen Threadripper HEDT processors.

sWRX8 has the same memory and I/O interfaces, and the same on-package routing of signals as Socket SP3 Type-1/2 packages, with the differences noted above. The xGMI protocol and the WAFL interface, used to link processors on dual-socket platforms, are not supported on this socket. If sWRX8 processors are in fact EPYC 7002/7003 processors with different firmware and branding is unclear.

Allerdings kam mir gerade der Gedanke ob AMD sich auch darauf vorbereitet ein oder 2 TR in Retail mit 32 Kernen für AM5 zu releasen, für all jene denen die Anzahl der PCIe lanes und Speicherkanäle nicht so wichtig sind, aber eben mehr als 16 Kerne und hoher Takt ihre Workloads unterstützen. Da ergibt sich ja eine Lücke die Intel nutzen kann um ihr Retail-HEDT wieder zu etablieren mit Sapphire Rapids.

Plant AMD TR auf AM5 und hat deshalb den X670E Chipsatz überhaupt im Programm für AM5?

Folgende Indikatoren warfen bei mir die Frage auf:

- Warum sind die ersten AM5 Boards dermaßen überzogen mit der Stromversorgung und daher so teuer?

- TDP Klasse 170W hätte 7950X nicht gebraucht. Siehe: https://www.computerbase.de/2022-09/amd-ryzen-7950x-7900x-7700x-7600x-test/2/

Ryzen 9 7950X bis zu 230 Watt statt vormals bis zu 142 Watt zuzugestehen, hebt die Leistung im Multi-Core-Testparcours um lediglich 5 Prozent an. Andersherum sinkt die Leistung um nur 5 Prozent, wenn die bekannte Obergrenze für den 16-Kern-Prozessor genutzt wird. Und selbst bei 88 Watt, also lediglich 38 % der offiziellen Obergrenze, ist die neue CPU noch 12 Prozent schneller als der Vorgänger.

- Der 7950X hat 24 PCIe 5.0 Lanes

- 4 Reserviert für Chipsatz Anbindung

- 8 Reserviert für NVMe SSDs

- 16 reserviert für GPU

Hier fängt für mich die erste Merkwürdigkeit an: die Chipsatz Anbindung ist als PCIe 4.0 konfiguriert. Warum? Und kann das auch als PCIe 5.0 konfiguriert werden?

Dann gibt es Boards für 1.600,-€ wie dieses hier: https://forum.planet3dnow.de/index.php?mbdb/mainboards/msi-meg-x670e-godlike.1049/

Mit Multi GPU Support - Warum?

3x PCI-E x16 slot

Supports x16/x0/x4, x8/x8/x4 - das sind schon 20 Lanes bei Bestückung der 3 16x Slots.alle von der CPU

Dazu M2.Slot 4x lanes PCIe 5.0von der CPU

Da sind dann 24 lanes aufgebraucht und noch keine Chipsatz Anbindung genutzt, die ja ebenfalls 4 lanes benötigt.Sind das Vorbereitungen um einen 32-Kerner auf AM5 nachzuschieben als Dualchannel Konkurrenz zu Intels Alder Lake-S auf W680, der ja ebenfalls als Dualchannel kommen soll?

AMD würde ja eine ganze Plattform damit einsparen und den AM5 nochmals aufwerten zeitgleich, doch ist das möglich dass da so ein Bluff gefahren wird? Damit würde eine eigene HEDT-Plattform von Intel mit erscheinen schon EOL werden, zumindest als Retail.

Dazu passt auch das relativ frühe erscheinen der Threadripper in Q1/2023 - weniger Arbeit für eine eigene Plattform, SP5-Boards mit Epyc und TR bestückbar, AM5 mit AGESA Update mit TR nutzbar um die Lücken zu Workstation zu schließen.

Irgendwie ergeben für mich nur auf diese Weise die Chipsatzeinteilungen - vor allem der 670E, einen Sinn. Denn ich wüsste nicht warum man sonst so viele Chipsatz-Varianten benötigen würde.

E555user

Admiral Special

- Mitglied seit

- 05.10.2015

- Beiträge

- 1.551

- Renomée

- 593

Nein, wie im Bild gezeigt hat der 7000er deren 28 PCIe5 Lanes. Nur diese erste Chipsatz-Generation begnügt sich in der Anbindung mit PCIe4. Bleiben 24 direkte Leitungen am SoC übrig.Der 7950X hat 24 PCIe 5.0 Lanes

Ich bin sicher bei den sehr teuren Multi-GPU Boards ist ein PCIe Switch verbaut oder die günstigeren verweisen beim Betrieb via Slot am Chipsatz auf reduzierte Anbindung.

Der Chipsatz selbst braucht die PCIe5 Anbindung nicht, es sollte energetisch günstiger sein langsamer zu takten und die Chips können/müssen einfacher in grösserer Entfernung zum Sockel platziert werden.

Die Anhebung der TDP über den aktuellen Nutzen hinaus sehe ich nur als Vorsichtsmassnahme für den Lebenszyklus des AM5. AMD musste das tun um nicht wegen einer zu geringen TDP von Intel übertrumpft zu werden. Die Anhebung ist ggü. Intel moderat, die maximalen Watt-Zahlen für den Betrieb im Desktop grenzwertig.

Für Threadripper halte ich die These von Moores-Law-is-Dead als realistischer. Als Workstation-CPU profitiert man von mehr Kernen mehr als von grösserem L3, deshalb wird der dort halbiert. Mit Zen4C würde genau das möglich werden. Ich würde annehmen man wird in der Zielsetzung für Zen4C keinen V-Cache supporten. Das ist dann allerdings überhaupt nicht mehr im "HEDT-Gaming" vermarktbar.

Nachtrag: Es wurden die E-Varianten der Chipsätze damit erklärt, dass die Kunden günstige Boards haben wollen ohne die Zukunftssicherheit von teurerem PCIe5. Deshalb gibts den Buchstaben für die Unterscheidung. Technisch ist das alles nur ein Chipsatz-Chip für alle Konfigurationen. Nur das Board-Layout definiert am Ende welcher Chipsatz-Typ vermarktet wird.

Zuletzt bearbeitet:

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Danke Dir - ich habe mir das 10x angeschaut vor meinem Post - dabei steht da ganz eindeutig die 28 im Bild. Manchmal ist es echt seltsam mit dem HirnNein, wie im Bild gezeigt hat der 7000er deren 28 PCIe5 Lanes. Nur diese erste Chipsatz-Generation begnügt sich in der Anbindung mit PCIe4. Bleiben 24 direkte Leitungen am SoC übrig.Der 7950X hat 24 PCIe 5.0 Lanes

Edit: HEDT-Gaming gibt es ja nicht mehr in dem Sinn, wenn schon 16 Kerne zu viel sind um hoch genug zu takten. Zu 4-Core Desktop Zeiten war das noch möglich inkl. höherem Powerbudget. Die Desktop-Plattformen lassen da ja keinen Raum mehr, was ich irgendwie auch sinnvoll finde.

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

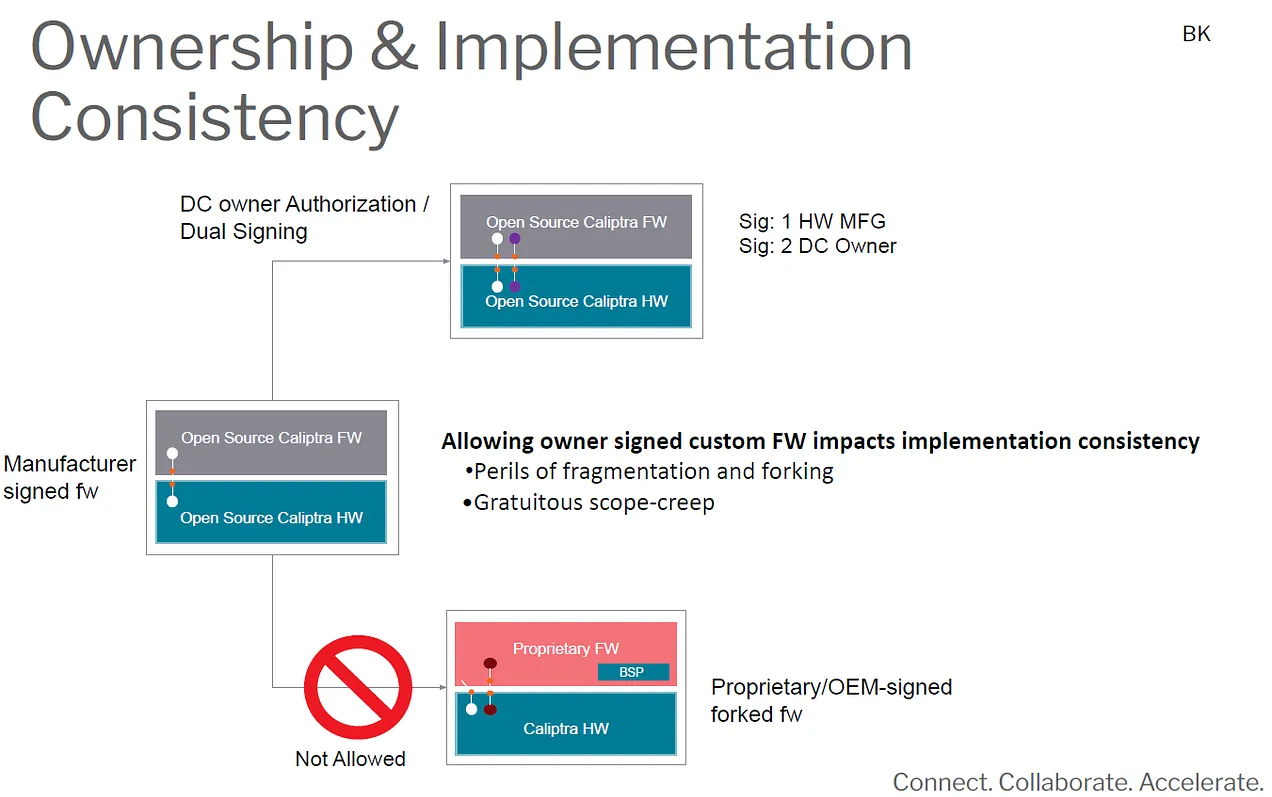

Es scheint beim Security Prozessor geht es nun doch in eine andere Richtung mit der ersten OpenSource Hardware mit RISC-V:Aus PSP (ARM) wird ASP (Microsoft Pluton)

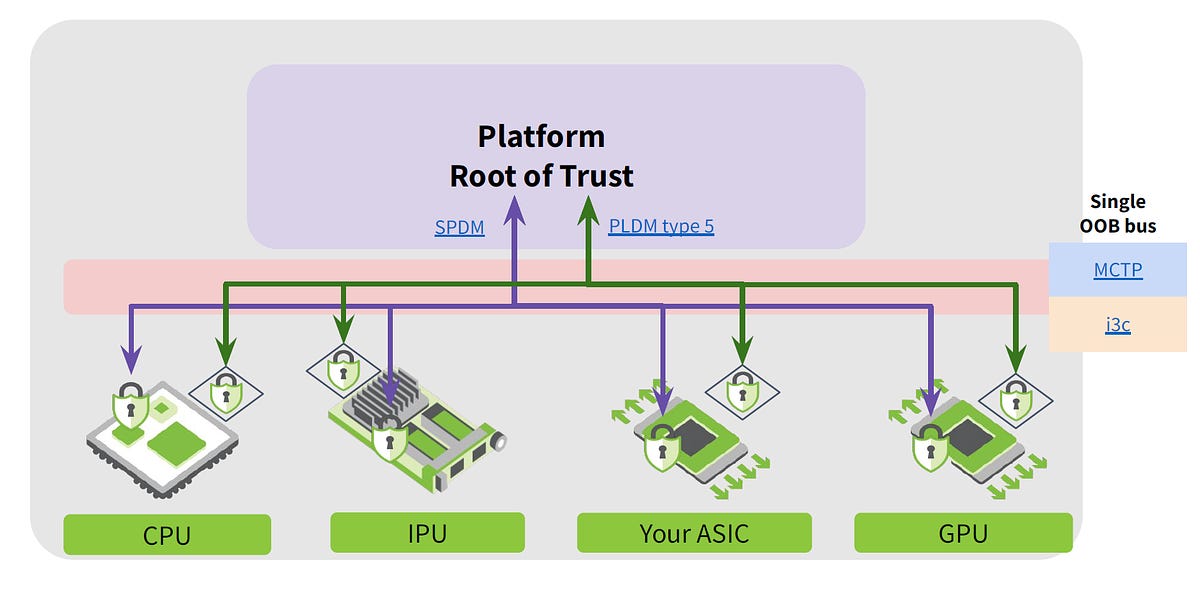

Caliptra – First Open-Source Silicon Going Into All Datacenter Chips

Every chip from Microsoft, Google, AMD, and Nvidia

[...]At the Open Compute Project 2022, Caliptra was jointly announced by Microsoft, Google, AMD. Nvidia also joined the project more recently and will begin contributing to the effort. After having spoken to a few engineers about the project at OCP, it seems clear that Microsoft and Google will make it a requirement for all compute, networking, and memory/storage controller chips supplied to their datacenters to implement a Caliptra-based open-source silicon root of trust.

Das wäre dann bei Zen5 oder erst Zen6?Our understanding is AMD took these requests and wanted to align their partners together. All 3 firms joined together to create an open standard like Titan, but with more buy-in and focused open development. Google and Microsoft are targeting Caliptra implementation in their own silicon in 2024, and AMD is targeting soon after.

In jedem Fall würde es sämtliche Firmware-Änderungen für OEMs genehmigungspflichtig machen und solche Geschichten der Vergangenheit angehören: https://www.securityweek.com/us-gov...alling-firmware-security-single-point-failure

“In addition, as devices and firmware change, OEMs often contract with different firmware developers, which can lead to delays or a lack of any update when older devices require updating and the original developer is not available. All of these factors can leave firmware open to malicious attacks,” the report said.

The agencies also called attention to the pain-point of applying firmware updates. “A firmware’s update process and capability vary by device. Some devices receive regular firmware updates. Some may only receive one update over their lifetimes, while others may never receive an update.”

Even worse, the process to install firmware updates is not simple, leading to skipped patches for critical-level vulnerabilities.

“Firmware updates present a major logistical challenge for many enterprises,” the agences said. “In many instances, device firmware is never updated or may only be updated in an emergency. In addition, vendors may only supply firmware updates if driven by an incident or identified vulnerability.”

Auch bei heise gefunden:

AMD, Google, Microsoft, Nvidia: Offengelegter Sicherheitsprozessor Caliptra

Branchenschwergewichte setzen auf RISC-V-Technik für offengelegte Hardware-Security. Sie könnte Black-Box-Umsetzungen wie Microsofts Pluton ersetzen.

Ich bin ein wenig perplex und AMD und Nvidia vielleicht auch - ob dieser Ueberschrift:

www.computerbase.de

www.computerbase.de

Auch wenn man nicht sagen kann, ob die Gamerkarte etwas taugt, haette man vor wenigen Jahren eine solche Entwicklung noch ins Reich der Maerchen verdammt und nun kommt sie aus dem selbigen der Mitte**.

Ob dieser nur auf dem Papier erzielte 'Vorsprung' an der Schnittstelle nur ein Papyrus Sieg ist, wird sich noch zeigen muessen.

Aber das sich hier insbesondere AMD den Schneid hat abkaufen lassen...

PCIe 5.0 geht also auch in 16/12?nm ... und demnaechst dann auf AM5?

Wenn die Leistung & Stabi (Woher kommen in solch kurzer Zeit vernueftige Treiber, was ist mit dem Verbrauch bei der staatlichen Taktrate von 1800Mhz@16/12nm usw. !? Dreiste Kopien? ) ansatzweise stimmen und diese in Stueckzahlen zu konkurrenzfaehigen (End)Preisen produziert werden kann - werden AMD und Nvidia in China Marktanteile verlieren - oder!?

Ob es sonst fuer die beiden grossen Player relevant wird - glaube ich eher nicht. Aber wenn die Geschwindigkeit nur im Ansatz so weitergeht - dann wird MT vielleicht doch in wenigen Jahren am Kuchen von unten knabbern zu mal im guenstigen Sektor AMD & Co. eher blank sind.

Gruss,

TNT

** Ja, woher auch immer die IP / das Know-how (Nvidia inkl. Lederjacke? ) kommt...

) kommt...

Moore Threads MTT S80: Die erste Gaming-GPU mit PCIe 5.0 kommt jetzt aus China

Die Moore Threads MTT S80 ist die weltweit erste an Spieler adressierte Grafikkarte mit PCIe 5.0 und bietet 4.096 Shader und 16 GB GDDR6.

Auch wenn man nicht sagen kann, ob die Gamerkarte etwas taugt, haette man vor wenigen Jahren eine solche Entwicklung noch ins Reich der Maerchen verdammt und nun kommt sie aus dem selbigen der Mitte**.

Ob dieser nur auf dem Papier erzielte 'Vorsprung' an der Schnittstelle nur ein Papyrus Sieg ist, wird sich noch zeigen muessen.

Aber das sich hier insbesondere AMD den Schneid hat abkaufen lassen...

PCIe 5.0 geht also auch in 16/12?nm ... und demnaechst dann auf AM5?

Wenn die Leistung & Stabi (Woher kommen in solch kurzer Zeit vernueftige Treiber, was ist mit dem Verbrauch bei der staatlichen Taktrate von 1800Mhz@16/12nm usw. !? Dreiste Kopien? ) ansatzweise stimmen und diese in Stueckzahlen zu konkurrenzfaehigen (End)Preisen produziert werden kann - werden AMD und Nvidia in China Marktanteile verlieren - oder!?

Ob es sonst fuer die beiden grossen Player relevant wird - glaube ich eher nicht. Aber wenn die Geschwindigkeit nur im Ansatz so weitergeht - dann wird MT vielleicht doch in wenigen Jahren am Kuchen von unten knabbern zu mal im guenstigen Sektor AMD & Co. eher blank sind.

Gruss,

TNT

** Ja, woher auch immer die IP / das Know-how (Nvidia inkl. Lederjacke?

Zuletzt bearbeitet:

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 14.375

- Renomée

- 1.980

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 3950X

- Mainboard

- MSI MPG X570 GAMING PRO CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 4x 16 GB G.Skill Trident Z RGB, DDR4-3200, CL14

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Intel 600p 1TB

- HDD

- Western Digital WD Red 2 & 3TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

Woher kommt überhaupt das Gerede um angebliches nvidia Knowhow?

PCIe 5.0 ist ein kein Nvidia Knowhow sondern ein normaler Standard den jeder nutzen kann der ihn lizensiert.

Die IO Geschichten lassen sich nur schlecht sinnvoll schrumpfen da die Treiberstufen für die erforderlichen Stromstärken nunmal eine Mindestgröße benötigen und dabei letztendlich nur deren Logik Teil vernünftig geschrumpft werden kann. Genau das macht sich AMD ja bei seiner Chiplet Strategie zum Nutzen.

Chinesischen Herstellern steht wegen der Sanktionen kein modernerer Fertigungsprozess zur Verfügung und so ziemlich alle GPUs aus der damaligen Zeit die einen 12/16nm Prozess nutzten hingen im Taktbereich unter 2 GHz rum weshalb man wohl eher auf eine Grenze des Designs/Fertigunsgprozesses ausgehen kann.

PCIe 5.0 ist ein kein Nvidia Knowhow sondern ein normaler Standard den jeder nutzen kann der ihn lizensiert.

Die IO Geschichten lassen sich nur schlecht sinnvoll schrumpfen da die Treiberstufen für die erforderlichen Stromstärken nunmal eine Mindestgröße benötigen und dabei letztendlich nur deren Logik Teil vernünftig geschrumpft werden kann. Genau das macht sich AMD ja bei seiner Chiplet Strategie zum Nutzen.

Chinesischen Herstellern steht wegen der Sanktionen kein modernerer Fertigungsprozess zur Verfügung und so ziemlich alle GPUs aus der damaligen Zeit die einen 12/16nm Prozess nutzten hingen im Taktbereich unter 2 GHz rum weshalb man wohl eher auf eine Grenze des Designs/Fertigunsgprozesses ausgehen kann.

Was heisst hier Gerede!? Schau mal wer den Laden gegruendet haben soll -> Ex-Nvidia GM fuer China.Woher kommt überhaupt das Gerede um angebliches nvidia Knowhow?

Was ist da naeherliegend?

Zu einem kompletten Grafikchip und Karte gehoert sicherlich mehr als nur die Schnittstelle - oder!?

AMD und Nvidia haben noch keine Notwendigkeit gesehen bei ihrer top-aktuellen Generation - warum auch immer (Vermutlich zu wenig Nutzen oder schlechte Kosten/Nutzen Relation, Energiehunger etc.).

Dass Schnittstellenlogik schlechter skaliert bei kleinen Fertigungsgroessen kann nicht allein der Grund sein (AMDs Chipletansatz arbeitet jan einer 'Loesung'); denn ich hoffe doch, dass mit der naechsten Generation (oder gar schon mit dem Refresh dieser?) die neue Schnittstelle Einzug haelt,

Sprich irgendwann kommt auch PCIe 5.0 zu AMDs/Nivida/Intel Karten - auch wenn es mehr Die Space kostet als man sich wuenscht.

Es bleibt aber fuer mich erstaunlich, dass ein chin. Entwickler/Hersteller hier (zu welchen Kosten (Preis, Stromverbrauch), auf welchem Wege auch immer (Patente?)) den BigPlayern zuvor kommt. Zumal - wenn das alles so stimmt - man hier nicht mehr nur von einer Ankuendigung sprechen kann, wenn am 11.11 erste Exemplare verkauft werden sollen (Oder doch nur Hoax?).

All das PCIe 5.0 nutzt sicherlich nichts, wenn es nicht funktioniert oder die Karte sonst nur Mist ist.

Das Aufgreifen von PCIe 5.0 zeigt mir nur, dass man hier mit Ehrgeiz (oder nur Marketing?) zur Sache geht und wer weiss wo sie in 5 bis 10 Jahren sind.

Es duerfte klar sein, dass man sich nicht vor zwei Jahren hingesetzt hat mit einem leeren Blatt Papier und von ganz vorn ohne Know-How angefangen hat eine GPU zu entwerfen. Und schwupps in 24 Monaten hat man eine fertige Karte in der Hand... viel geht - aber das?

Aber warten wir kurz ab - die ersten Karten werden sicherlich irgendwo getestet werden - vielleicht sogar auf AM5 Boards...

Dann wird man vielleicht auch schlauer - wer gedanklich der ZIehvater dieser GPU ist...

Ich finde es spannend - ob man bei AMD/Nividia - abgesehen von Patenten - dort genauer hinschaut?

TNT

Vielleicht ist der Vorteil von PCIe 5.0 in der Praxis nicht so wichtig,Aber das sich hier insbesondere AMD den Schneid hat abkaufen lassen...

da selbst die PCIe 3.0 Schnittstelle von der Bandbreite im Gaming oft nicht mal gesättigt wird.

Für was brauche ich PCIe 5.0 wenn selbst PCIe 3.0 locker ausreicht ?

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Das ist eine 14,4 TFlops Karte - Die RX6700XT hat 12,4 TFlops. Was da PCIe5 bringen soll ist fraglich. Das wirkt eher unnötig, erhöht ohne Mehrwert den Stromverbrauch und verbraucht Diefläche.

Für was brauche ich PCIe 5.0 wenn selbst PCIe 3.0 locker ausreicht ?

Es koennte AMD nuetzlich sein, um fuer die AM5-Plattform aktuell bessere Argumente zu haben.

Selbst wenn der Benefit von PCIe 5.0 (oder oft sogar bei PCIe 4.0, je nach Karte auch bei PCIe 3.0?) Anschlusses fuer Grafikarten aktuell eher gering ist oder nur im lauten Getoese von Benchmarks nachgewiesen werden koennte.

Das ist eine 14,4 TFlops Karte - Die RX6700XT hat 12,4 TFlops. Was da PCIe5 bringen soll ist fraglich. Das wirkt eher unnötig, erhöht ohne Mehrwert den Stromverbrauch und verbraucht Diefläche.

Ganz richtig - ein reiner Marketing Stunt? Und dann nur fuer China!?

Oder soll das nur den Anspruch und den Ehrgeiz (und den Willen irgendwann weltweit zu verkaufen?) dokumentieren (oder der Schnittstellen Block muss noch ein paar Chipgenerationen herhalten und man will sich Neutentwicklungen an dieser Stelle sparen?)? NoAhnung.

Deswegen bin ich ja so perplex - dass es nun bei einem chin. Entwickler/Hersteller kommen soll (auch sonst liest sich die Featureliste des Chips erstaunlich modern).

Gruss,

TNT

Zuletzt bearbeitet:

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 14.375

- Renomée

- 1.980

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 3950X

- Mainboard

- MSI MPG X570 GAMING PRO CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 4x 16 GB G.Skill Trident Z RGB, DDR4-3200, CL14

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Intel 600p 1TB

- HDD

- Western Digital WD Red 2 & 3TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

Das war es schon für diese wilde Spekulation? Nichts handfestes? Hast du ne Ahnung wieviel in der Wirtschaft kreuz und quer durch die Firmen gewechselt wird?Was heisst hier Gerede!? Schau mal wer den Laden gegruendet haben soll -> Ex-Nvidia GM fuer China.

Was ist da naeherliegend?

Und dann ausgerechnet PCIe 5.0 als Anhaltspunkt nehmen obwohl nvidia kein Produkt mit der Schnittstelle auf dem Markt hat und wohl auch die nächsten 1-2 Jahre kein entsprechendes Produkt auf den Markt bringen wird?

Und natürloch werden auch AMD, Intel und nvidia irgendwann mit entsprechenden Produkten rauskommen, schließlich ist das keine herstellerspezifische Schnittstelle.

Für einen Neuling könnte es übrigens von Vorteil sein gleich auf die neueste Schnittstellengeneration zu setzen. Man kann das knowhow auch bei späteren Produktgenerationen nutzen und spart sich den Entwicklungsaufwand und -Kosten für die auslaufende Generation.

@sompe - das ist doch keine wilde Speku. Handfest ist, dass der (Mit)Gruender bei Nvidia als GM fuer China taetig war.

Das ist nicht strittig. Das ist der Anhaltspunkt und nicht die Schnittstelle! Wie kommst Du darauf?

Wenn man jemand bei Nvidia gearbeitet hat - dann bringt er sein dort erworbenes Know-how mit zu seiner naechsten Arbeitsplatz.

Er hat die Philosophie Nvidias und Kontkate intus und nicht die von AMD oder von Intel was seinen Fachbereich angeht.

Was liegt also ferner anzunehmen, dass die Ideen einer Grafikarchitektur bzw. wie man eine solche entwickelt eher Nvidias aehneln als jemanden anderen?

Wie wird er den neuen Laden wohl fuehren?

Das heisst nun nicht, dass 1:1 abgekupfert wird oder es nur um dreiste Kopien (siehe eben PCIe 5.0 Schnittstellenblock) geht.

Eine Grafikkarte und Chip besteht aus viel mehr als nur diesem Block.

Wenn ein GM wechselt - dann vermute ich, dass er den einen oder anderen mitgezogen hat - ebenfalls mit Nvidia Background. Es ist nicht der Pfoertner von Nvidia gewechselt sondern der GM China. So etwas passiert jeden Tag wie Du es selbst sagst.

Sicherlich ist das Speku was den Umfang angeht - aber nicht wild.

Ich bin auf Deine Idee gespannt - woher das Know-How mehrheitlich kommen soll. PowerVR, S3, Intel, Matrox, dortige Uniabsolventen?

Die neuen Chips sind gewiss nicht von Neulingen auf dem Gebiet designt worden. Nicht in der kurzen Zeit IMHO.

Gruss,

TNT

Das ist nicht strittig. Das ist der Anhaltspunkt und nicht die Schnittstelle! Wie kommst Du darauf?

Wenn man jemand bei Nvidia gearbeitet hat - dann bringt er sein dort erworbenes Know-how mit zu seiner naechsten Arbeitsplatz.

Er hat die Philosophie Nvidias und Kontkate intus und nicht die von AMD oder von Intel was seinen Fachbereich angeht.

Was liegt also ferner anzunehmen, dass die Ideen einer Grafikarchitektur bzw. wie man eine solche entwickelt eher Nvidias aehneln als jemanden anderen?

Wie wird er den neuen Laden wohl fuehren?

Das heisst nun nicht, dass 1:1 abgekupfert wird oder es nur um dreiste Kopien (siehe eben PCIe 5.0 Schnittstellenblock) geht.

Eine Grafikkarte und Chip besteht aus viel mehr als nur diesem Block.

Wenn ein GM wechselt - dann vermute ich, dass er den einen oder anderen mitgezogen hat - ebenfalls mit Nvidia Background. Es ist nicht der Pfoertner von Nvidia gewechselt sondern der GM China. So etwas passiert jeden Tag wie Du es selbst sagst.

Sicherlich ist das Speku was den Umfang angeht - aber nicht wild.

Ich bin auf Deine Idee gespannt - woher das Know-How mehrheitlich kommen soll. PowerVR, S3, Intel, Matrox, dortige Uniabsolventen?

Die neuen Chips sind gewiss nicht von Neulingen auf dem Gebiet designt worden. Nicht in der kurzen Zeit IMHO.

Gruss,

TNT

sompe

Grand Admiral Special

- Mitglied seit

- 09.02.2009

- Beiträge

- 14.375

- Renomée

- 1.980

- Mein Laptop

- Dell G5 15 SE 5505 Eclipse Black

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 3950X

- Mainboard

- MSI MPG X570 GAMING PRO CARBON WIFI

- Kühlung

- Wasserkühlung

- Speicher

- 4x 16 GB G.Skill Trident Z RGB, DDR4-3200, CL14

- Grafikprozessor

- AMD Radeon RX 6900 XT

- Display

- 1x 32" LG 32UD89-W + 1x 24" Dell Ultrasharp 2405FPW

- SSD

- Samsung SSD 980 PRO 1TB, Crucial MX500 500GB, Intel 600p 512GB, Intel 600p 1TB

- HDD

- Western Digital WD Red 2 & 3TB

- Optisches Laufwerk

- LG GGC-H20L

- Soundkarte

- onboard

- Gehäuse

- Thermaltake Armor

- Netzteil

- be quiet! Dark Power Pro 11 1000W

- Betriebssystem

- Windows 10 Professional, Windows 7 Professional 64 Bit, Ubuntu 20.04 LTS

- Webbrowser

- Firefox

Mag sein aber darum ging es auch nicht sondern darum das daher das Knowhow bzw. die Technologie kam.@sompe - das ist doch keine wilde Speku. Handfest ist, dass der (Mit)Gruender bei Nvidia als GM fuer China taetig war.

Das ist nicht strittig. Das ist der Anhaltspunkt und nicht die Schnittstelle! Wie kommst Du darauf?

Da du offenbar damit davon ablenken willst und dir damit dessen sehr wohl bewußt bist kann ich mir wohl jede weiter Diskussion mit dir sparen.

Klassischer Auftakt zum Trollen eben.

Doppelposting wurde automatisch zusammengeführt:

Ganz interessante News zum aktuellen Marktumfeld.

Nachfragerückgang: TSMCs 7-nm-Prozess kaum noch zu 50 % ausgelastet

TSMC hatte bereits davor gewarnt, jetzt kommt es aber schneller als gedacht. Die Nachfrage nach 7-nm-Chips bricht massiv ein.

Könnte AMD in dem Zusammenhang versuchen bessere Konsitionen für ihre entsprechenden Produkte auszuhandeln?

Intel könnten mit seinen N6 GPUs eventuell auch davon profitieren.

Zuletzt bearbeitet:

@sompe - das ist traurig. Du vermischt hier und drehst die Dinge wie sie Dir gerade passen. Null Argumente.

Ich habe nur vom KnowHow gesprochen.

Dass das KnowHow bei Nividia erlernt/geholt wurde wird in dieser Quellen auch so gesehen:

Tomshardware - Moore Threads MTT S10 Graphics Card Hits Retail at $112

Wie kommen sie wohl dazu so was zu schreiben - aber gut Dir gefaellt es nicht - warum auch immer - vielleicht einfach nur schlechte Laune?

Das schlimme daran ist erst mal nichts dramatisches oder verwerfliches und damit schon gar nicht die Spucke wert.

Aber genug davon - fuehrt zu nichts und ist OT.

Da sind wir uns einig. Vola.

DNFTT

TNT

Ich habe nur vom KnowHow gesprochen.

Dass das KnowHow bei Nividia erlernt/geholt wurde wird in dieser Quellen auch so gesehen:

Tomshardware - Moore Threads MTT S10 Graphics Card Hits Retail at $112

Wie kommen sie wohl dazu so was zu schreiben - aber gut Dir gefaellt es nicht - warum auch immer - vielleicht einfach nur schlechte Laune?

Das schlimme daran ist erst mal nichts dramatisches oder verwerfliches und damit schon gar nicht die Spucke wert.

Aber genug davon - fuehrt zu nichts und ist OT.

Da sind wir uns einig. Vola.

DNFTT

TNT

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Also wer einmal einen Job erfolgreich 5 Jahre lange in einem Unternehmen geleistet hat, nimmt dieses Know How dann immer mit zum nächsten? Ich glaub Du vermischst da etwas. Die Technologie ist geschützt und das wars. Das andere sind Skills und Qualifikation. Die gehören nicht dem Ex-Arbeitgeber. Das mitgebrachte Mindset von Nvidia ist allerdings gut zu erkennen, mit dem implementieren von unnützen und teuren Features, nur um Erster zu sein.

in china?Die Technologie ist geschützt und das wars.

Complicated

Grand Admiral Special

- Mitglied seit

- 08.10.2010

- Beiträge

- 4.949

- Renomée

- 441

- Mein Laptop

- Lenovo T15, Lenovo S540

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 7 3700X

- Mainboard

- MSI X570-A PRO

- Kühlung

- Scythe Kama Angle - passiv

- Speicher

- 32 GB (4x 8 GB) G.Skill TridentZ Neo DDR4-3600 CL16-19-19-39

- Grafikprozessor

- Sapphire Radeon RX 5700 Pulse 8GB PCIe 4.0

- Display

- 27", Lenovo, 2560x1440

- SSD

- 1 TB Gigabyte AORUS M.2 PCIe 4.0 x4 NVMe 1.3

- HDD

- 2 TB WD Caviar Green EADS, NAS QNAP

- Optisches Laufwerk

- Samsung SH-223L

- Gehäuse

- Lian Li PC-B25BF

- Netzteil

- Corsair RM550X ATX Modular (80+Gold) 550 Watt

- Betriebssystem

- Win 10 Pro.

Auch wieder wahr  Aber dafür müssten sie nicht ein ganzes Team einstellen.

Aber dafür müssten sie nicht ein ganzes Team einstellen.

Aber dafür müssten sie nicht ein ganzes Team einstellen.

Aber dafür müssten sie nicht ein ganzes Team einstellen.- Mitglied seit

- 16.10.2000

- Beiträge

- 24.371

- Renomée

- 9.696

- Standort

- East Fishkill, Minga, Xanten

- Aktuelle Projekte

- Je nach Gusto

- Meine Systeme

- Ryzen 9 5900X, Ryzen 7 3700X

- BOINC-Statistiken

- Folding@Home-Statistiken

- Mein Laptop

- Samsung P35 (16 Jahre alt ;) )

- Details zu meinem Desktop

- Prozessor

- AMD Ryzen 9 5900X

- Mainboard

- ASRock B550

- Speicher

- 2x 16 GB DDR4 3200

- Grafikprozessor

- GeForce GTX 1650

- Display

- 27 Zoll Acer + 24 Zoll DELL

- SSD

- Samsung 980 Pro 256 GB

- HDD

- diverse

- Soundkarte

- Onboard

- Gehäuse

- Fractal Design R5

- Netzteil

- be quiet! Straight Power 10 CM 500W

- Tastatur

- Logitech Cordless Desktop

- Maus

- Logitech G502

- Betriebssystem

- Windows 10

- Webbrowser

- Firefox, Vivaldi

- Internetanbindung

- ▼250 MBit ▲40 MBit

Offering Unmatched Performance, Leadership Energy Efficiency and Next-Generation Architecture, AMD Brings 4th Gen AMD EPYC™ Processors to The Modern Data Center - Planet 3DNow!

Auf Planet 3DNow! gibt es alle wichtigen Informationen für AMD-User: News, Downloads, Support, Tests

www.planet3dnow.de

Ähnliche Themen

- Antworten

- 731

- Aufrufe

- 51K

- Antworten

- 0

- Aufrufe

- 2K

- Antworten

- 0

- Aufrufe

- 1K

- Antworten

- 763

- Aufrufe

- 100K